### **ABSOLUTE MAXIMUM RATINGS**

| AV <sub>CC</sub> to V <sub>SS</sub> , AGND, DGND, REFGND0.3V to +12V<br>V <sub>SS</sub> to AGND, DGND6V to +0.3V<br>AV <sub>DD</sub> , DV <sub>DD</sub> to AGND, DGND, REFGND0.3V to +6V |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AGND to DGND0.3V to +0.3V                                                                                                                                                                |

| REF to AGND, DGND,                                                                                                                                                                       |

| REFGND0.3V to the lower of (AV <sub>DD</sub> + 0.3V) and +6V                                                                                                                             |

| REFGND to AGND0.3V to +0.3V                                                                                                                                                              |

| Digital Inputs to AGND, DGND,                                                                                                                                                            |

| REFGND0.3V to the lower of (DVDD + 0.3V) and +6V                                                                                                                                         |

| DOUT to DGND0.3V to the lower of (DV <sub>DD</sub> + 0.3V) and +6V                                                                                                                       |

| OUT_ to V <sub>SS</sub> 0.3V to the lower of (AV <sub>CC</sub> + 0.3V) and +12V                                                                                                          |

| GS to AGND1V to +1V                                                                                                                                                                      |

| Maximum Current into REF<br>Maximum Current into Any Pin                                         |         |

|--------------------------------------------------------------------------------------------------|---------|

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)<br>Thin QFN (derate 31.3mW/°C above +70°C) |         |

| ,                                                                                                |         |

| TQFP (derate 25mW/°C above +70°C)                                                                | 2.0W    |

| Operating Temperature Ranges                                                                     |         |

| MAX573_UCB0°C t                                                                                  | o +85°C |

| Junction Temperature                                                                             | .+150°C |

| Storage Temperature Range65°C to                                                                 | +150°C  |

| Lead Temperature (soldering, 10s)                                                                | .+300°C |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### ELECTRICAL CHARACTERISTICS—MAX5732 (0 to +5V Output Voltage Range)

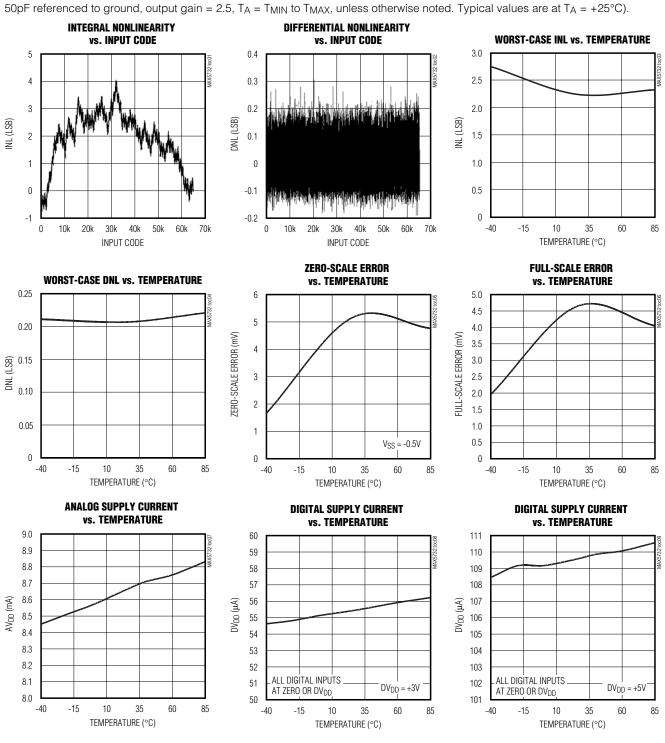

$(AV_{CC} = +5.25V \text{ to } +5.5V \text{ (Note 1)}, AV_{DD} = +5V \pm 5\%, DV_{DD} = +2.7V \text{ to } AV_{DD}, V_{SS} = AGND = DGND = REFGND = GS = 0, V_{REF} = +3.0V, R_L = \infty, C_L = 50pF$  referenced to ground, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                             | SYMBOL | CONDITIONS                                                  | MIN | ТҮР  | МАХ  | UNITS         |

|---------------------------------------|--------|-------------------------------------------------------------|-----|------|------|---------------|

| DC CHARACTERISTICS                    |        |                                                             | •   |      |      |               |

| Resolution                            | Ν      |                                                             | 16  |      |      | Bits          |

| Integral Naplingerity (Nate 2)        | INL    | MAX5732A                                                    |     | ±4   | ±8   | LSB           |

| Integral Nonlinearity (Note 2)        |        | MAX5732B                                                    |     | ±8   | ±16  | LSB           |

| Differential Nonlinearity             | DNL    | Guaranteed monotonic (Note 3)                               |     |      | ±1   | LSB           |

| Zero-Scale Error                      | VOS    | V <sub>SS</sub> = -0.5V, AV <sub>CC</sub> = +5.25V (Note 4) |     | ±8   | ±40  | mV            |

| Full-Scale Error                      |        | (Note 4)                                                    |     | ±8   | ±50  | mV            |

| Gain Error                            |        |                                                             |     | ±0.1 | ±0.5 | %FSR          |

| Gain Temperature Coefficient          |        |                                                             |     | 20   |      | ppm<br>FSR/°C |

| DC Crosstalk                          |        | V <sub>SS</sub> = -0.5V, AV <sub>CC</sub> = +5V (Note 5)    |     | 50   | 250  | μV            |

| DYNAMIC CHARACTERISTICS               | •      |                                                             | •   |      |      |               |

| Output-Voltage Settling Time          |        | Full-scale change to $\pm 0.5$ LSB                          |     | 20   |      | μs            |

| Voltage-Output Slew Rate              |        |                                                             |     | 1    |      | V/µs          |

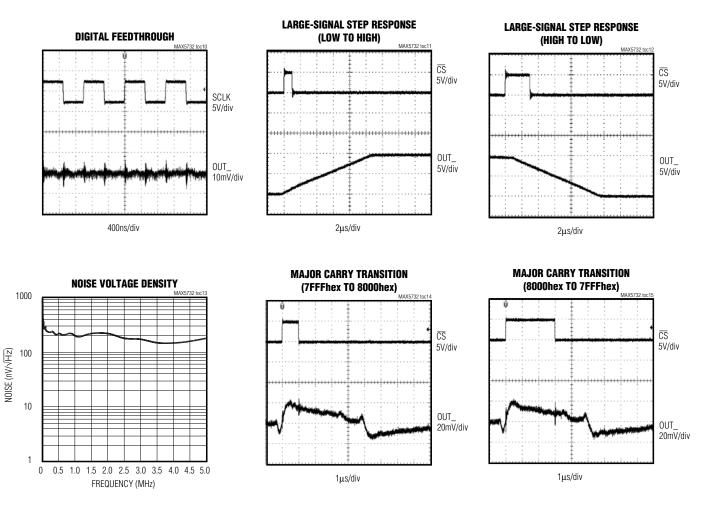

| Digital Feedthrough                   |        | (Note 6)                                                    |     | 5    |      | nV-s          |

| Digital Crosstalk                     |        | (Note 7)                                                    |     | 5    |      | nV-s          |

| Digital-to-Analog Glitch Impulse      |        | Major carry transition                                      |     | 120  |      | nV-s          |

| DAC-to-DAC Crosstalk                  |        | (Note 8)                                                    |     | 15   |      | nV-s          |

| Output Noise Spectral Density at 1kHz |        | Full-scale code                                             |     | 250  |      | nV/√Hz        |

| ANALOG OUTPUTS (OUT0 to OL            | JT31)  | •                                                           | ·   |      |      |               |

| Output Voltage Range                  |        | V <sub>SS</sub> = -0.5V, AV <sub>CC</sub> = +5.25V (Note 1) | 0   |      | 5    | V             |

| Resistive Load to Ground              |        |                                                             | 10  | 50   |      | kΩ            |

### ELECTRICAL CHARACTERISTICS—MAX5732 (0 to +5V Output Voltage Range) (continued)

$(AV_{CC} = +5.25V \text{ to } +5.5V \text{ (Note 1)}, AV_{DD} = +5V \pm 5\%, DV_{DD} = +2.7V \text{ to } AV_{DD}, V_{SS} = AGND = DGND = REFGND = GS = 0, V_{REF} = +3.0V, R_L = \infty, C_L = 50pF$  referenced to ground,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                     | SYMBOL           |                                         | CONDITIONS                         | MIN                  | ТҮР   | MAX   | UNITS |

|-----------------------------------------------|------------------|-----------------------------------------|------------------------------------|----------------------|-------|-------|-------|

| Capacitive Load to Ground                     |                  |                                         |                                    |                      | 50    | 100   | рF    |

| DC Output Impedance                           |                  |                                         |                                    |                      | 0.1   |       | Ω     |

| Short-Circuit Current                         |                  | Sourcing, full-sc<br>to AGND            | ale code, output connected         |                      | 5     |       | ~^^   |

| Short-Circuit Current                         |                  | Sinking, zero-sc<br>to AV <sub>CC</sub> | ale code, output connected         |                      | -5    |       | mA    |

| GROUND-SENSE ANALOG INPU                      | T (GS)           |                                         |                                    |                      |       |       |       |

| Input Voltage Range                           | VGS              | Relative to AGN                         | D                                  | -0.5                 |       | +0.5  | V     |

| GS Gain                                       | Ags              |                                         |                                    | 0.995                | 1.000 | 1.005 | V/V   |

| Input Resistance                              |                  | $-0.5V \le V_{GS} \le +$                | 0.5V, V <sub>SS</sub> = -0.5V      | 35                   |       |       | kΩ    |

| REFERENCE INPUT (REF)                         |                  |                                         |                                    |                      |       |       |       |

| Input Resistance                              |                  |                                         |                                    | 1                    |       |       | MΩ    |

| Reference Input Voltage Range                 | V <sub>REF</sub> | Referred to REF                         | GND                                | 2.900                | 3.000 | 3.100 | V     |

| DIGITAL INPUTS (CS, SCLK, DIN                 | , LDAC, CLI      | R, DSP)                                 |                                    |                      |       |       |       |

|                                               | Maria            | $DV_{DD} = +2.7V t$                     | o +3.6V                            | $0.7 \times DV_{DD}$ |       |       | V     |

| Input-Voltage High                            | VIH              |                                         |                                    |                      |       |       | v     |

|                                               |                  | $DV_{DD} = +4.75V$                      | to +5.25V                          | 2.4                  |       | 0.0   |       |

| Input-Voltage Low                             | VIL              |                                         |                                    |                      | 10    | 0.8   | V     |

| Input Capacitance                             | CIN              | Distitutions at                         | 0 D\/                              |                      | 10    |       | pF    |

|                                               |                  | Digital inputs =                        |                                    |                      |       | ±1    | μA    |

| POWER REQUIREMENTS (AV <sub>CC</sub>          | VSS, AGNL        | , AVDD, DVDD, L                         | (GND)                              |                      |       |       |       |

| Output-Amplifier Positive Supply<br>Voltage   | AV <sub>CC</sub> | (Note 1)                                |                                    | 4.75                 |       | 5.50  | V     |

| Output-Amplifier Negative Supply Voltage      | V <sub>SS</sub>  |                                         |                                    | -0.5                 |       | 0     | V     |

| Output-Amplifier Supply Voltage<br>Difference |                  | AV <sub>CC</sub> - V <sub>SS</sub>      |                                    |                      |       | 5.75  | V     |

| Analog Supply Voltage                         | AV <sub>DD</sub> |                                         |                                    | 4.75                 |       | 5.25  | V     |

| Digital Supply Voltage                        | DVDD             |                                         |                                    | 2.70                 |       | 5.25  | V     |

|                                               |                  | VOUT0 through                           | /OUT31 = 0                         |                      | 10    | 15    | mA    |

| Analog Supply Current                         | AIDD             | Software shutdo                         |                                    |                      | 10    |       | μA    |

|                                               |                  | Viн = DVpp, Vii                         | = 0, f <sub>SCLK</sub> = 20MHz     |                      | 2.5   | 3.5   |       |

| Digital Supply Current                        | DI <sub>DD</sub> |                                         | = +0.8V, f <sub>SCLK</sub> = 20MHz |                      | 5     | 6.5   | mA    |

| Output-Amplifier Positive Supply              |                  | VOUT0 through                           |                                    |                      | 4     | 10    | mA    |

| Current                                       | AICC             | Software shutdo                         |                                    |                      | 20    |       | μA    |

| Output-Amplifier Negative Supply              | 1.               |                                         | $V_{OUT0}$ through $V_{OUT31} = 0$ |                      | -4    | -10   | mA    |

| Current                                       | ISS              | $V_{SS} = -0.5V$                        | Software shutdown                  |                      | -20   |       | μA    |

| Power-Supply Rejection Ratio                  | PSRR             |                                         |                                    |                      | -95   |       | dB    |

### ELECTRICAL CHARACTERISTICS—MAX5733 (0 to +10V Output Voltage Range)

$(AV_{CC} = +10.5V \text{ to } +11V, AV_{DD} = 5V \pm 5\%, DV_{DD} = +2.7V \text{ to } AV_{DD}, V_{SS} = AGND = DGND = REFGND = GS = 0, V_{REF} = +3.0V, R_L = \infty, C_L = 50pF$  referenced to ground, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                                | SYMBOL  | CONDITIONS                                                  | MIN      | ТҮР   | MAX   | UNITS         |

|------------------------------------------|---------|-------------------------------------------------------------|----------|-------|-------|---------------|

| DC CHARACTERISTICS                       | •       | ·                                                           | •        |       |       |               |

| Resolution                               | Ν       |                                                             | 16       |       |       | Bits          |

|                                          | INII    | MAX5733A                                                    |          | ±4    | ±8    |               |

| Integral Nonlinearity (Note 2)           | INL     | MAX5733B                                                    |          | ±8    | ±16   | LSB           |

| Differential Nonlinearity                | DNL     | Guaranteed monotonic (Note 3)                               |          |       | ±1    | LSB           |

| Zero-Scale Error                         | Vos     | $V_{SS} = -0.5V, AV_{CC} = +10V (Note 4)$                   |          | ±8    | ±40   | mV            |

| Full-Scale Error                         |         | (Note 4)                                                    |          | ±8    | ±50   | mV            |

| Gain Error                               |         |                                                             |          | ±0.1  | ±0.5  | % FSR         |

| Gain Temperature Coefficient             |         |                                                             |          | 20    |       | ppm<br>FSR/°C |

| DC Crosstalk                             |         | V <sub>SS</sub> = -0.5V, AV <sub>CC</sub> = +10V (Note 5)   |          | 50    | 250   | μV            |

| DYNAMIC CHARACTERISTICS                  |         | • • •                                                       | <b>I</b> |       |       |               |

| Output-Voltage Settling Time             |         | Full-scale change to $\pm 0.5$ LSB                          |          | 20    |       | μs            |

| Voltage-Output Slew Rate                 |         |                                                             |          | 1     |       | V/µs          |

| Digital Feedthrough                      |         | (Note 6)                                                    |          | 5     |       | nV-s          |

| Digital Crosstalk                        |         | (Note 7)                                                    | Ì        | 5     |       | nV-s          |

| Digital-to-Analog Glitch Impulse         |         | Major carry transition                                      |          | 120   |       | nV-s          |

| DAC-to-DAC Crosstalk                     |         | (Note 8)                                                    |          | 15    |       | nV-s          |

| Output Noise Spectral Density at<br>1kHz |         | Full-scale code                                             |          | 250   |       | nV/√Hz        |

| ANALOG OUTPUTS (OUT0 to O                | JT31)   | 1                                                           |          |       |       |               |

| Output Voltage Range                     |         | V <sub>SS</sub> = -0.5V, AV <sub>CC</sub> = +10.5V (Note 1) | 0        |       | 10    | V             |

| Resistive Load to Ground                 |         |                                                             | 10       | 50    |       | kΩ            |

| Capacitive Load to Ground                |         |                                                             |          | 50    | 100   | рF            |

| DC Output Impedance                      |         |                                                             | Ì        | 0.1   |       | Ω             |

|                                          |         | Sourcing, full scale, output connected to AGND              |          | 5     |       |               |

| Short-Circuit Current                    |         | Sinking, zero scale, output connected to AV <sub>CC</sub>   |          | -5    |       | mA            |

| GROUND-SENSE ANALOG INPL                 | IT (GS) |                                                             |          |       |       |               |

| Input Voltage Range                      | VGS     | Relative to AGND                                            | -0.5     |       | +0.5  | V             |

| GS Gain                                  | Ags     |                                                             | 0.995    | 1.000 | 1.005 | V/V           |

| Input Resistance                         |         | $-0.5V \le V_{GS} \le +0.5V, V_{SS} = -0.5V$                | 70       |       |       | kΩ            |

| REFERENCE INPUT (REF)                    |         |                                                             |          |       |       |               |

| Input Resistance                         |         |                                                             | 1        |       |       | MΩ            |

| Reference Input Voltage Range            | VREF    | Referred to REFGND                                          | 2.900    | 3.000 | 3.100 | V             |

M/IXI/M

### ELECTRICAL CHARACTERISTICS—MAX5733 (0 to +10V Output Voltage Range) (continued)

$(AV_{CC} = +10.5V \text{ to } +11V, AV_{DD} = 5V \pm 5\%, DV_{DD} = +2.7V \text{ to } AV_{DD}, V_{SS} = AGND = DGND = REFGND = GS = 0, V_{REF} = +3.0V, R_L = \infty, C_L = 50pF$  referenced to ground, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                                     | SYMBOL                                         |                                           | CONDITIONS                         | MIN                       | ТҮР | MAX  | UNITS |  |  |  |  |

|-----------------------------------------------|------------------------------------------------|-------------------------------------------|------------------------------------|---------------------------|-----|------|-------|--|--|--|--|

| DIGITAL INPUTS (CS, SCLK, DIN                 | DIGITAL INPUTS (CS, SCLK, DIN, LDAC, CLR, DSP) |                                           |                                    |                           |     |      |       |  |  |  |  |

| Input-Voltage High                            | VIH                                            | $DV_{DD} = +2.7V to$                      | o +3.6V                            | 0.7 ×<br>DV <sub>DD</sub> |     |      | V     |  |  |  |  |

|                                               |                                                | $DV_{DD} = +4.75V$                        | to +5.25V                          | 2.4                       |     |      |       |  |  |  |  |

| Input-Voltage Low                             | VIL                                            |                                           |                                    |                           |     | 0.8  | V     |  |  |  |  |

| Input Capacitance                             | CIN                                            |                                           |                                    |                           | 10  |      | pF    |  |  |  |  |

| Input Current                                 | IIN                                            | Digital inputs = 0                        | ) or DV <sub>DD</sub>              |                           |     | ±1   | μA    |  |  |  |  |

| POWER REQUIREMENTS (AV <sub>CC</sub> ,        | V <sub>SS</sub> , AGNE                         | , AV <sub>DD</sub> , DV <sub>DD</sub> , D | GND)                               |                           |     |      |       |  |  |  |  |

| Output-Amplifier Positive Supply<br>Voltage   | AV <sub>CC</sub>                               | (Note 1)                                  |                                    | 10                        |     | 11   | V     |  |  |  |  |

| Output-Amplifier Negative Supply<br>Voltage   | V <sub>SS</sub>                                |                                           |                                    | -0.5                      |     | 0    | V     |  |  |  |  |

| Output-Amplifier Supply Voltage<br>Difference |                                                | AV <sub>CC</sub> - V <sub>SS</sub>        |                                    |                           |     | 11   | V     |  |  |  |  |

| Analog Supply Voltage                         | AV <sub>DD</sub>                               |                                           |                                    | 4.75                      |     | 5.25 | V     |  |  |  |  |

| Digital Supply Voltage                        | DV <sub>DD</sub>                               |                                           |                                    | 2.70                      |     | 5.25 | V     |  |  |  |  |

| Analog Supply Current                         | Aldd                                           | $V_{OUT0}$ through $\$                    | / <sub>OUT31</sub> = 0             |                           | 10  | 15   | mA    |  |  |  |  |

| Analog Supply Current                         | AIDD                                           | Software shutdo                           | wn                                 |                           | 10  |      | μA    |  |  |  |  |

| Digital Supply Current                        | DIDD                                           | $V_{IH} = DV_{DD}, V_{IL}$                | = 0, f <sub>SCLK</sub> = 20MHz     |                           | 2.5 | 3.5  | mA    |  |  |  |  |

|                                               | 000                                            | $V_{IH} = +2.4V, V_{IL}$                  | = +0.8V, f <sub>SCLK</sub> = 20MHz |                           | 5   | 6.5  | 110/  |  |  |  |  |

| Output-Amplifier Positive Supply              | Alcc                                           | Vouto through \                           | /OUT31 = 0                         |                           | 4   | 10   | mA    |  |  |  |  |

| Current                                       |                                                | Software shutdo                           | wn                                 |                           | 20  |      | μA    |  |  |  |  |

| Output-Amplifier Negative Supply              | ISS                                            | Vss = -0.5V                               | $V_{OUT0}$ through $V_{OUT31} = 0$ |                           | -4  | -10  | mA    |  |  |  |  |

| Current                                       | '33                                            | V33 - 0.0V                                | Software shutdown                  |                           | -20 |      | μA    |  |  |  |  |

| Power-Supply Rejection Ratio                  | PSRR                                           |                                           |                                    |                           | -95 |      | dB    |  |  |  |  |

### ELECTRICAL CHARACTERISTICS—MAX5734 (-2.5V to +7.5V Output Voltage Range)

$(AV_{CC} = +7.75V \text{ to } +8.25V, AV_{DD} = +5V \pm 5\%, DV_{DD} = +2.7V \text{ to } AV_{DD}, V_{SS} = -2.75V \text{ to } -3.25V, AGND = DGND = REFGND = GS = 0, program the offset DAC to 4000hex. V_{REF} = +3.0V, R_L = ∞, C_L = 50pF referenced to ground, T_A = T_{MIN} \text{ to } T_{MAX}$ , unless otherwise noted. Typical values are at T\_A = +25°C.)

| PARAMETER                             | SYMBOL           | CONDITIONS                                                   | MIN   | ТҮР   | MAX   | UNITS         |

|---------------------------------------|------------------|--------------------------------------------------------------|-------|-------|-------|---------------|

| DC CHARACTERISTICS                    |                  |                                                              |       |       |       |               |

| Resolution                            | Ν                |                                                              | 16    |       |       | Bits          |

| Integral Marlinegrity (Mate 2)        | INII             | MAX5734A                                                     |       | ±4    | ±8    |               |

| Integral Nonlinearity (Note 2)        | INL              | MAX5734B                                                     |       | ±8    | ±16   | LSB           |

| Differential Nonlinearity             | DNL              | Guaranteed monotonic (Note 3)                                |       |       | ±1    | LSB           |

| Zero-Scale Error                      | Vos              | V <sub>SS</sub> = -3.25V, AV <sub>CC</sub> = +7.75V (Note 4) |       | ±8    | ±40   | mV            |

| Full-Scale Error                      |                  | (Note 4)                                                     |       | ±8    | ±50   | mV            |

| Gain Error                            |                  |                                                              |       | ±0.1  | ±0.5  | %FSR          |

| Gain Temperature Coefficient          |                  |                                                              |       | 20    |       | ppm<br>FSR/°C |

| DC Crosstalk                          |                  | V <sub>SS</sub> = -3.25V, AV <sub>CC</sub> = +7.75V (Note 4) |       | 50    | 250   | μV            |

| DYNAMIC CHARACTERISTICS               |                  | · · · · · · · · · · · · · · · · · · ·                        |       |       |       |               |

| Output-Voltage Settling Time          |                  | Full-scale change to ±0.5 LSB                                |       | 20    |       | μs            |

| Voltage-Output Slew Rate              |                  |                                                              |       | 1     |       | V/µs          |

| Digital Feedthrough                   |                  | (Note 6)                                                     |       | 5     |       | nV-s          |

| Digital Crosstalk                     |                  | (Note 7)                                                     |       | 5     |       | nV-s          |

| Digital-to-Analog Glitch Impulse      |                  | Major carry transition                                       |       | 120   |       | nV-s          |

| DAC-to-DAC Crosstalk                  |                  | (Note 8)                                                     |       | 15    |       | nV-s          |

| Output Noise Spectral Density at 1kHz |                  | Full-scale code                                              |       | 250   |       | nV/√Hz        |

| ANALOG OUTPUTS (OUT0 to OU            | JT31)            |                                                              |       |       |       |               |

| Output Voltage Range                  |                  | V <sub>SS</sub> = -2.75V, AV <sub>CC</sub> = +7.75V (Note 1) | -2.5  |       | +7.5  | V             |

| Resistive Load to Ground              |                  |                                                              | 10    | 50    |       | kΩ            |

| Capacitive Load to Ground             |                  |                                                              |       | 50    | 100   | рF            |

| DC Output Impedance                   |                  |                                                              |       | 0.1   |       | Ω             |

|                                       |                  | Sourcing, full scale, output connected to AGND               |       | 5     |       |               |

| Short-Circuit Current                 |                  | Sinking, zero scale, output connected to AV <sub>CC</sub>    |       | -5    |       | mA            |

| GROUND-SENSE ANALOG INPU              | T (GS)           | •                                                            |       |       |       |               |

| Input Voltage Range                   | VGS              | Relative to AGND                                             | -0.5  |       | +0.5  | V             |

| GS Gain                               | Ags              |                                                              | 0.995 | 1.000 | 1.005 | V/V           |

| Input Resistance                      |                  | $-0.5V \le V_{GS} \le +0.5V$ , $V_{SS} = -0.5V$              | 70    |       |       | kΩ            |

| REFERENCE INPUT (REF)                 |                  |                                                              |       |       |       |               |

| Input Resistance                      |                  |                                                              | 1     |       |       | MΩ            |

| Reference Input Voltage Range         | V <sub>REF</sub> | Referred to REFGND                                           | 2.900 | 3.000 | 3.100 | V             |

# ELECTRICAL CHARACTERISTICS—MAX5734 (-2.5V to +7.5V Output Voltage Range) (continued)

$(AV_{CC} = +7.75V \text{ to } +8.25V, AV_{DD} = +5V \pm 5\%, DV_{DD} = +2.7V \text{ to } AV_{DD}, V_{SS} = -2.75V \text{ to } -3.25V, AGND = DGND = REFGND = GS = 0, program the offset DAC to 4000hex. V_{REF} = +3.0V, R_{L} = \infty, C_{L} = 50pF referenced to ground, T_{A} = T_{MIN} \text{ to } T_{MAX}$ , unless otherwise noted. Typical values are at T\_{A} = +25°C.)

| PARAMETER                                     | SYMBOL                 | (                                         | CONDITIONS                         | MIN                       | ТҮР | MAX   | UNITS |

|-----------------------------------------------|------------------------|-------------------------------------------|------------------------------------|---------------------------|-----|-------|-------|

| DIGITAL INPUTS (CS, SCLK, DIN                 | LDAC, CLI              | R, DSP)                                   |                                    |                           |     |       |       |

| Input-Voltage High                            | VIH                    | $DV_{DD} = +2.7V to$                      | o +3.6V                            | 0.7 ×<br>DV <sub>DD</sub> |     |       | V     |

|                                               |                        | $DV_{DD} = +4.75V$                        | to +5.25V                          | 2.4                       |     |       |       |

| Input-Voltage Low                             | VIL                    |                                           |                                    |                           |     | 0.8   | V     |

| Input Capacitance                             | CIN                    |                                           |                                    |                           | 10  |       | рF    |

| Input Current                                 | lin                    | Digital inputs = 0                        | ) or DV <sub>DD</sub>              |                           |     | ±1    | μA    |

| POWER REQUIREMENTS (AV <sub>CC</sub> ,        | V <sub>SS</sub> , AGNE | , AV <sub>DD</sub> , DV <sub>DD</sub> , D | GND)                               |                           |     |       |       |

| Output-Amplifier Positive Supply<br>Voltage   | AV <sub>CC</sub>       | (Note 1)                                  |                                    | 7.50                      |     | 8.25  | V     |

| Output-Amplifier Negative Supply<br>Voltage   | V <sub>SS</sub>        |                                           |                                    | -3.25                     |     | -2.50 | V     |

| Output-Amplifier Supply Voltage<br>Difference |                        | AV <sub>CC</sub> - V <sub>SS</sub>        |                                    |                           |     | 11    | V     |

| Analog Supply Voltage                         | AV <sub>DD</sub>       |                                           |                                    | 4.75                      |     | 5.25  | V     |

| Digital Supply Voltage                        | DVDD                   |                                           |                                    | 2.70                      |     | 5.25  | V     |

| Analog Cupply Current                         | A                      | Vouto through V                           | /OUT31 = 0                         |                           | 10  | 15    | mA    |

| Analog Supply Current                         | AIDD                   | Software shutdo                           | wn                                 |                           | 10  |       | μΑ    |

| Digital Supply Current                        | Dian                   | $V_{IH} = DV_{DD}, V_{IL}$                | = 0, f <sub>SCLK</sub> = 20MHz     |                           | 2.5 | 3.5   | mA    |

| Digital Supply Current                        | DIDD                   | $V_{IH} = +2.4V, V_{IL}$                  | = +0.8V, $f_{SCLK}$ = 20MHz        |                           | 5   | 6.5   | ШA    |

| Output-Amplifier Positive Supply              | A                      | Vouto through V                           | /OUT31 = 0                         |                           | 4   | 10    | mA    |

| Current                                       | AICC                   | Software shutdo                           | wn                                 |                           | 20  |       | μA    |

| Output-Amplifier Negative Supply              | 100                    | V <sub>SS</sub> = -2.75V                  | $V_{OUT0}$ through $V_{OUT31} = 0$ |                           | -4  | -10   | mA    |

| Current                                       | ISS                    | v55 = -2.75V                              | Software shutdown                  |                           | -20 |       | μA    |

| Power-Supply Rejection Ratio                  | PSRR                   |                                           |                                    |                           | -95 |       | dB    |

### ELECTRICAL CHARACTERISTICS—MAX5735 (-5V to +5V Output Voltage Range)

$(AV_{CC} = +5.25V \text{ to } +5.5V, AV_{DD} = +5V \pm 5\%, DV_{DD} = +2.7V \text{ to } AV_{DD}, V_{SS} = -5.25V \text{ to } -5.5V, AGND = DGND = REFGND = GS = 0, program the offset DAC to 8000hex. V_{REF} = +3.0V, R_L = ∞, C_L = 50pF referenced to ground, T_A = T_{MIN} \text{ to } T_{MAX}$ , unless otherwise noted. Typical values are at T\_A = +25°C.)

| PARAMETER                             | SYMBOL     | CONDITIONS                                                   | MIN   | ТҮР   | МАХ   | UNITS         |

|---------------------------------------|------------|--------------------------------------------------------------|-------|-------|-------|---------------|

| DC CHARACTERISTICS                    | •          |                                                              | •     |       |       |               |

| Resolution                            | Ν          |                                                              | 16    |       |       | Bits          |

|                                       |            | MAX5735A                                                     |       | ±4    | ±8    |               |

| Integral Nonlinearity (Note 2)        | INL        | MAX5735B                                                     |       | ±8    | ±16   | LSB           |

| Differential Nonlinearity             | DNL        | Guaranteed monotonic (Note 3)                                |       |       | ±1    | LSB           |

| Zero-Scale Error                      | Vos        | V <sub>SS</sub> = -5.25V, AV <sub>CC</sub> = +5.25V (Note 4) |       | ±8    | ±40   | mV            |

| Full-Scale Error                      |            | (Note 4)                                                     |       | ±8    | ±50   | mV            |

| Gain Error                            |            |                                                              |       | ±0.1  | ±0.5  | %FSR          |

| Gain Temperature Coefficient          |            |                                                              |       | 20    |       | ppm<br>FSR/°C |

| DC Crosstalk                          |            | V <sub>SS</sub> = -5.75V, AV <sub>CC</sub> = +5.25V (Note 5) |       | 50    | 250   | μV            |

| DYNAMIC CHARACTERISTICS               |            | •                                                            | •     |       |       | •             |

| Output-Voltage Settling Time          |            | Full-scale change to ±0.5 LSB                                |       | 20    |       | μs            |

| Voltage-Output Slew Rate              |            |                                                              |       | 1     |       | V/µs          |

| Digital Feedthrough                   |            | (Note 6)                                                     |       | 5     |       | nV-s          |

| Digital Crosstalk                     |            | (Note 7)                                                     |       | 5     |       | nV-s          |

| Digital-to-Analog Glitch Impulse      |            | Major carry transition                                       |       | 120   |       | nV-s          |

| DAC-to-DAC Crosstalk                  |            | (Note 8)                                                     |       | 15    |       | nV-s          |

| Output Noise Spectral Density at 1kHz |            | Full-scale code                                              |       | 250   |       | nV/√Hz        |

| ANALOG OUTPUTS (OUT0 throu            | igh OUT31) |                                                              |       |       |       |               |

| Output Voltage Range                  |            | V <sub>SS</sub> = -5.25V, AV <sub>CC</sub> = +5.25V (Note 1) | -5    |       | +5    | V             |

| Resistive Load to Ground              |            |                                                              | 10    | 50    |       | kΩ            |

| Capacitive Load to Ground             |            |                                                              |       | 50    | 100   | pF            |

| DC Output Impedance                   |            |                                                              |       | 0.1   |       | Ω             |

|                                       |            | Sourcing, full scale, output connected to AGND               |       | 5     |       |               |

| Short-Circuit Current                 |            | Sinking, zero scale, output connected to AV <sub>CC</sub>    |       | -5    |       | mA            |

| GROUND-SENSE ANALOG INPU              | IT (GS)    |                                                              |       |       |       |               |

| Input Voltage Range                   | VGS        | Relative to AGND                                             | -0.5  |       | +0.5  | V             |

| GS Gain                               | Ags        |                                                              | 0.995 | 1.000 | 1.005 | V/V           |

| Input Resistance                      |            | $-0.5V \le V_{GS} \le +0.5V, V_{SS} = -0.5V$                 | 70    |       |       | kΩ            |

| REFERENCE INPUT (REF)                 | •          | •                                                            |       |       |       |               |

| Input Resistance                      |            |                                                              | 1     |       |       | MΩ            |

| Reference Input Voltage Range         | VREF       | Referred to REFGND                                           | 2.900 | 3.000 | 3.100 | V             |

### ELECTRICAL CHARACTERISTICS—MAX5735 (-5V to +5V Output Voltage Range) (continued)

$(AV_{CC} = +5.25V \text{ to } +5.5V, AV_{DD} = +5V \pm 5\%, DV_{DD} = +2.7V \text{ to } AV_{DD}, V_{SS} = -5.25V \text{ to } -5.5V, AGND = DGND = REFGND = GS = 0, program the offset DAC to 8000hex. V_{REF} = +3.0V, R_L = ∞, C_L = 50pF referenced to ground, T_A = T_{MIN} \text{ to } T_{MAX}, unless otherwise noted. Typical values are at T_A = +25°C.)$

| PARAMETER                                     | SYMBOL                 | (                                         | CONDITIONS                         | MIN                       | ТҮР | MAX   | UNITS |

|-----------------------------------------------|------------------------|-------------------------------------------|------------------------------------|---------------------------|-----|-------|-------|

| DIGITAL INPUTS (CS, SCLK, DIN,                | LDAC, CLF              | R, DSP)                                   |                                    |                           |     |       |       |

| Input-Voltage High                            | VIH                    | $DV_{DD} = +2.7V \text{ to}$              | ) +3.6V                            | 0.7 ×<br>DV <sub>DD</sub> |     |       | V     |

|                                               |                        | $DV_{DD} = +4.75V$                        | to 5.25V                           | 2.4                       |     |       |       |

| Input-Voltage Low                             | VIL                    |                                           |                                    |                           |     | 0.8   | V     |

| Input Capacitance                             | CIN                    |                                           |                                    |                           | 10  |       | рF    |

| Input Current                                 | lin                    | Digital inputs = 0                        | ) or DV <sub>DD</sub>              |                           |     | ±1    | μA    |

| POWER REQUIREMENTS (AV <sub>CC</sub> ,        | V <sub>SS</sub> , AGND | , AV <sub>DD</sub> , DV <sub>DD</sub> , D | GND)                               |                           |     |       |       |

| Output-Amplifier Positive Supply<br>Voltage   | AV <sub>CC</sub>       | (Note 1)                                  |                                    | 4.75                      |     | 5.50  | V     |

| Output-Amplifier Negative Supply<br>Voltage   | V <sub>SS</sub>        |                                           |                                    | -5.50                     |     | -4.75 | V     |

| Output-Amplifier Supply Voltage<br>Difference |                        | AV <sub>CC</sub> - V <sub>SS</sub>        |                                    |                           |     | 11    | V     |

| Analog Supply Voltage                         | AV <sub>DD</sub>       |                                           |                                    | 4.75                      |     | 5.25  | V     |

| Digital Supply Voltage                        | DV <sub>DD</sub>       |                                           |                                    | 2.70                      |     | 5.25  | V     |

| Analog Supply Current                         | Aldd                   | V <sub>OUT0</sub> through V               | 'OUT31 = 0                         |                           | 10  | 15    | mA    |

| Analog Supply Current                         | AIDD                   | Software shutdow                          | wn                                 |                           | 10  |       | μA    |

| Digital Supply Current                        | Diss                   | $V_{IH}=DV_{DD},V_{IL}$                   | = 0, f <sub>SCLK</sub> = 20MHz     |                           | 2.5 | 3.5   | mA    |

| Digital Supply Current                        | DI <sub>DD</sub>       | $V_{IH}=+2.4V,V_{IL}$                     | = +0.8V, f <sub>SCLK</sub> = 20MHz |                           | 5   | 6.5   | MA    |

| Output-Amplifier Positive Supply              | Alee                   | V <sub>OUT0</sub> through V               | 'OUT31 = 0                         |                           | 4   | 10    | mA    |

| Current                                       | AICC                   | Software shutdow                          | wn                                 |                           | 20  |       | μΑ    |

| Output-Amplifier Negative Supply              | Iss                    | Vss = -0.5V                               | $V_{OUT0}$ through $V_{OUT31} = 0$ |                           | -4  | -10   | mA    |

| Current                                       | 122                    | v 550.5 v                                 | Software shutdown                  |                           | -20 |       | μA    |

| Power-Supply Rejection Ratio                  | PSRR                   |                                           |                                    |                           | -95 |       | dB    |

Note 1: AV<sub>CC</sub> should be at least 0.25V higher than the maximum output voltage required from the DAC. Full-scale output is 5V for the MAX5732.

Note 2: Linearity guaranteed from code 2047 to full scale and from (V<sub>SS</sub> + 0.3V) to (AV<sub>CC</sub> - 0.3V).

Note 3: DNL guaranteed over all codes for ( $V_{SS} + 0.3V$ ) to (AV<sub>CC</sub> - 0.3V).

Note 4: Zero-scale error is measured at code 0. Full-scale error is measured at code FFFFhex.

Note 5: DC crosstalk is the change in the output level of one DAC at zero or full scale in response to the full-scale output change of all other DACs.

**Note 6:** Digital feedthrough is a measure of the impulse injected into the analog outputs from the digital control inputs when the device is not being written to. It is measured with a worst-case change on the digital inputs.

Note 7: Digital crosstalk is the glitch impulse transferred to the output of one DAC at midscale while a full-scale code change is written into another DAC.

**Note 8:** DAC-to-DAC crosstalk is the glitch impulse that appears at the output of one converter due to both the digital change and subsequent analog output change at another converter.

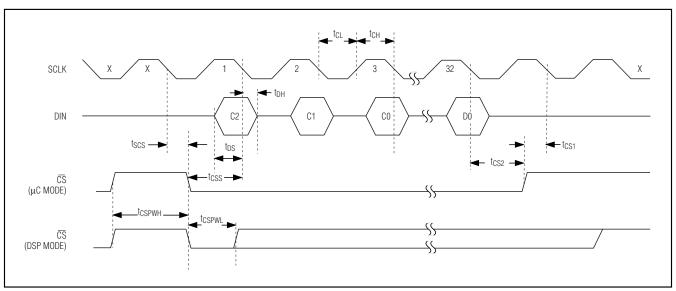

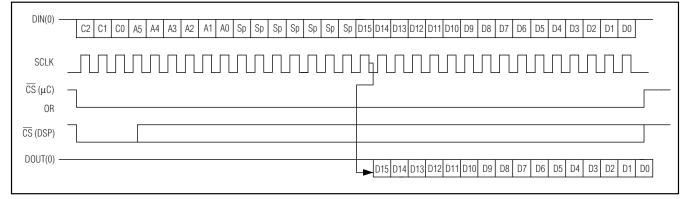

### TIMING CHARACTERISTICS—DVDD = +4.75V to +5.25V

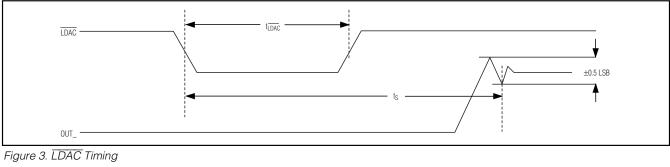

(Figures 2 and 3, AV<sub>DD</sub> = +4.75V to +5.25V, DV<sub>DD</sub> = +4.75V to +5.25V, AGND = DGND = REFGND = GS = 0,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C.)

| PARAMETER                                    | SYMBOL            | CONDITIONS                       | MIN | ТҮР | MAX | UNITS |

|----------------------------------------------|-------------------|----------------------------------|-----|-----|-----|-------|

| Serial Clock Frequency                       | <b>f</b> SCLK     |                                  | 0   |     | 33  | MHz   |

| SCLK Pulse-Width High                        | tсн               |                                  | 10  |     |     | ns    |

| SCLK Pulse-Width Low                         | tCL               |                                  | 10  |     |     | ns    |

| SCLK Fall to $\overline{CS}$ Fall Setup Time | tscs              |                                  | 6   |     |     | ns    |

| CS Fall to SCLK Fall Setup Time              | tcss              |                                  | 5   |     |     | ns    |

| CS Rise to SCLK Fall                         | tCS1              | At end of cycle in SPI mode only | 15  |     |     | ns    |

| SCLK Fall to $\overline{CS}$ Rise Setup Time | tCS2              |                                  | 0   |     |     | ns    |

| DIN to SCLK Fall Setup Time                  | tDS               |                                  | 10  |     |     | ns    |

| DIN to SCLK Fall Hold Time                   | tDH               |                                  | 2   |     |     | ns    |

| SCLK Fall to DOUT Fall                       | tSCL              | Load capacitance = 20pF          |     |     | 20  | ns    |

| SCLK Fall to DOUT Rise                       | tsdh              | Load capacitance = 20pF          |     |     | 20  | ns    |

| CS Pulse-Width High                          | <b>t</b> CSPWH    |                                  | 50  |     |     | ns    |

| CS Pulse-Width Low                           | tCSPWL            |                                  | 20  |     |     | ns    |

| LDAC Pulse-Width Low                         | t <sub>LDAC</sub> |                                  | 20  |     |     | ns    |

| CLR Pulse-Width Low                          | t <u>CLR</u>      |                                  | 20  |     |     | ns    |

### TIMING CHARACTERISTICS—DVDD = +2.7V to +5.25V

(Figures 2 and 3, AV<sub>DD</sub> = +4.75V to +5.25V, DV<sub>DD</sub> = +2.7V to +5.25V, AGND = DGND = REFGND = GS = 0, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                       | SYMBOL           | CONDITIONS                       | MIN | ТҮР | MAX | UNITS |

|---------------------------------|------------------|----------------------------------|-----|-----|-----|-------|

| Serial Clock Frequency          | <b>f</b> SCLK    |                                  | 0   |     | 25  | MHz   |

| SCLK Pulse-Width High           | tсн              |                                  | 10  |     |     | ns    |

| SCLK Pulse-Width Low            | tCL              |                                  | 10  |     |     | ns    |

| SCLK Fall to CS Fall Setup Time | tscs             |                                  | 10  |     |     | ns    |

| CS Fall to SCLK Fall Setup Time | tcss             |                                  | 10  |     |     | ns    |

| CS Rise to SCLK Fall            | tCS1             | At end of cycle in SPI mode only | 18  |     |     | ns    |

| SCLK Fall to CS Rise Setup Time | t <sub>CS2</sub> |                                  | 0   |     |     | ns    |

| DIN to SCLK Fall Setup Time     | tDS              |                                  | 10  |     |     | ns    |

| DIN to SCLK Fall Hold Time      | tDH              |                                  | 2   |     |     | ns    |

| SCLK Fall to DOUT Fall          | tSCL             | Load capacitance = 20pF (Note 9) |     |     | 35  | ns    |

| SCLK Fall to DOUT Rise          | tsdh             | Load capacitance = 20pF (Note 9) |     |     | 35  | ns    |

| CS Pulse-Width High             | <b>t</b> CSPWH   |                                  | 50  |     |     | ns    |

| CS Pulse-Width Low              | tCSPWL           |                                  | 20  |     |     | ns    |

| LDAC Pulse-Width Low            | <b>T</b> LDAC    |                                  | 20  |     |     | ns    |

| CLR Pulse-Width Low             | <b>t</b> CLR     |                                  | 20  |     |     | ns    |

**Note 9:** The maximum clock frequency ( $f_{SCLK}$ ) is 10MHz in daisy-chain mode when  $DV_{DD} < 4.75V$ .

**MAX5732-MAX5735**

### **Typical Operating Characteristics (continued)**

$(AV_{CC} = +10.5V \pm 5\%, AV_{DD} = +5V \pm 5\%, DV_{DD} = +5V, V_{SS} = AGND = DGND = REFGND = GS = 0, V_{REF} = +3.000V, R_L = ∞, C_L = 50pF$  referenced to ground, output gain = 2.5, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C).

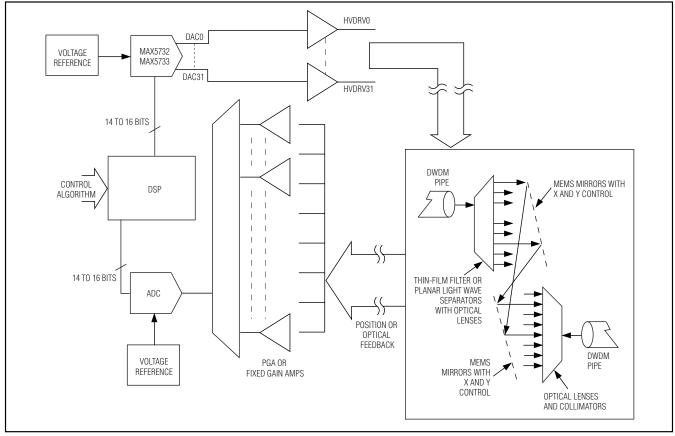

### \_Pin Description

| P          | PIN                         |                  |                                                                                                                                                                                            |  |  |  |

|------------|-----------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| TQFN       | TQFP                        | NAME             | FUNCTION                                                                                                                                                                                   |  |  |  |

| 1, 42, 48  | 1, 48, 55                   | AV <sub>CC</sub> | Output Amplifier Positive Supply Input. Bypass to $V_{SS}$ with a 0.1µF capacitor.                                                                                                         |  |  |  |

| 2          | 2                           | OUT9             | DAC9 Buffered Analog Output Voltage                                                                                                                                                        |  |  |  |

| 3          | 3                           | OUT8             | DAC8 Buffered Analog Output Voltage                                                                                                                                                        |  |  |  |

| 4          | 4                           | OUT7             | DAC7 Buffered Analog Output Voltage                                                                                                                                                        |  |  |  |

| 5          | 5, 15–18, 33,<br>34, 49, 64 | N.C.             | No Connection. Internally connected. Do not make any connections to N.C.                                                                                                                   |  |  |  |

| 6          | 6                           | OUT6             | DAC6 Buffered Analog Output Voltage                                                                                                                                                        |  |  |  |

| 7          | 7                           | OUT5             | DAC5 Buffered Analog Output Voltage                                                                                                                                                        |  |  |  |

| 8          | 8                           | OUT4             | DAC4 Buffered Analog Output Voltage                                                                                                                                                        |  |  |  |

| 9, 38      | 9, 44                       | AGND             | Analog Ground                                                                                                                                                                              |  |  |  |

| 10         | 10                          | OUT3             | DAC3 Buffered Analog Output Voltage                                                                                                                                                        |  |  |  |

| 11, 28, 39 | 11, 32, 45                  | V <sub>SS</sub>  | Output-Amplifier Negative-Supply Input                                                                                                                                                     |  |  |  |

| 12         | 12                          | OUT2             | DAC2 Buffered Analog Output Voltage                                                                                                                                                        |  |  |  |

| 13         | 13                          | OUT1             | DAC1 Buffered Analog Output Voltage                                                                                                                                                        |  |  |  |

| 14         | 14                          | OUTO             | DAC0 Buffered Analog Output Voltage                                                                                                                                                        |  |  |  |

| 15         | 19                          | DSP              | Digital Serial-Interface Select Input. Drive low for DSP-interface mode. Drive high for SPI-<br>interface mode.                                                                            |  |  |  |

| 16         | 20                          | CS               | Active-Low Digital Chip-Select Input                                                                                                                                                       |  |  |  |

| 17         | 21                          | DOUT             | Digital Serial Data Output. Use DOUT to daisy-chain and read the contents of the DAC registers.                                                                                            |  |  |  |

| 18         | 22                          | SCLK             | Digital Serial Clock Input Clock                                                                                                                                                           |  |  |  |

| 19         | 23                          | DIN              | Digital Serial Data Input                                                                                                                                                                  |  |  |  |

| 20         | 24                          | DVDD             | Digital Power Supply Input. Bypass to DGND with a 0.1µF capacitor.                                                                                                                         |  |  |  |

| 21         | 25                          | DGND             | Digital Ground                                                                                                                                                                             |  |  |  |

| 22         | 26                          | LDAC             | Active-Low Digital-Load DAC Input. Drive this asynchronous input low to transfer the contents of the input register to their respective DAC registers and set all DAC outputs accordingly. |  |  |  |

| 23         | 27                          | CLR              | Active-Low Digital-Clear Input. Drive this asynchronous input low to clear the contents of the input and DAC registers and set all the DAC outputs to zero.                                |  |  |  |

| 24         | 28                          | GS               | Ground-Sense Analog Input. Offsets the DAC amplifier outputs by $\pm 0.5V$ to compensate for a remote system ground potential difference.                                                  |  |  |  |

| 25, 49     | 29, 56                      | REFGN            | Reference Ground                                                                                                                                                                           |  |  |  |

| 26         | 30                          | REF              | Analog Reference Voltage Input                                                                                                                                                             |  |  |  |

| 27, 50     | 31, 57                      | AV <sub>DD</sub> | Analog Power Supply Input. Bypass to AGND with a 0.1µF capacitor.                                                                                                                          |  |  |  |

| 29         | 35                          | OUT31            | DAC31 Buffered Analog Output Voltage                                                                                                                                                       |  |  |  |

| 30         | 36                          | OUT30            | DAC30 Buffered Analog Output Voltage                                                                                                                                                       |  |  |  |

| 31         | 37                          | OUT29            |                                                                                                                                                                                            |  |  |  |

| 32         | 38                          | OUT28            |                                                                                                                                                                                            |  |  |  |

| 33         | 39                          | OUT27            | DAC27 Buffered Analog Output Voltage                                                                                                                                                       |  |  |  |

| 34         | 40                          | OUT26            | DAC26 Buffered Analog Output Voltage                                                                                                                                                       |  |  |  |

| 35         | 41                          | OUT25            | DAC25 Buffered Analog Output Voltage                                                                                                                                                       |  |  |  |

### \_\_\_\_\_Pin Description (continued)

| F    | PIN  |       | FUNCTION                                                                                                      |

|------|------|-------|---------------------------------------------------------------------------------------------------------------|

| TQFN | TQFP | NAME  | FUNCTION                                                                                                      |

| 36   | 42   | OUT24 | DAC24 Buffered Analog Output Voltage                                                                          |

| 37   | 43   | OUT23 | DAC23 Buffered Analog Output Voltage                                                                          |

| 40   | 46   | OUT22 | DAC22 Buffered Analog Output Voltage                                                                          |

| 41   | 47   | OUT21 | DAC21 Buffered Analog Output Voltage                                                                          |

| 43   | 50   | OUT20 | DAC20 Buffered Analog Output Voltage                                                                          |

| 44   | 51   | OUT19 | DAC19 Buffered Analog Output Voltage                                                                          |

| 45   | 52   | OUT18 | DAC18 Buffered Analog Output Voltage                                                                          |

| 46   | 53   | OUT17 | DAC17 Buffered Analog Output Voltage                                                                          |

| 47   | 54   | OUT16 | DAC16 Buffered Analog Output Voltage                                                                          |

| 51   | 58   | OUT15 | DAC15 Buffered Analog Output Voltage                                                                          |

| 52   | 59   | OUT14 | DAC14 Buffered Analog Output Voltage                                                                          |

| 53   | 60   | OUT13 | DAC13 Buffered Analog Output Voltage                                                                          |

| 54   | 61   | OUT12 | DAC12 Buffered Analog Output Voltage                                                                          |

| 55   | 62   | OUT11 | DAC11 Buffered Analog Output Voltage                                                                          |

| 56   | 63   | OUT10 | DAC10 Buffered Analog Output Voltage                                                                          |

| EP   | _    | EP    | Exposed Paddle. Internally connected to $V_{SS}$ . Connect externally to a metal pad for thermal dissipation. |

### **Detailed Description**

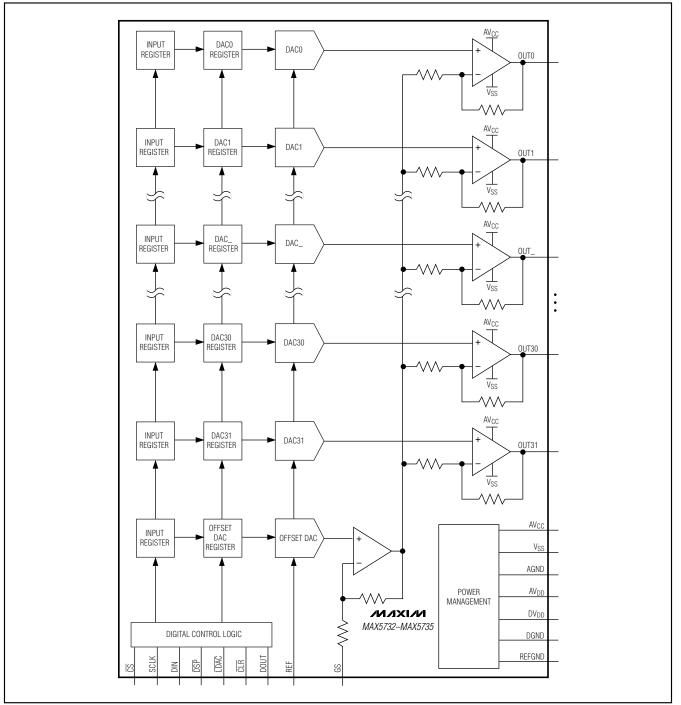

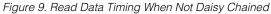

The MAX5732–MAX5735 are 32-channel, 16-bit, voltage-output DACs (Figure 1). The devices accept a 3V external reference input at REF. An internal offset DAC allows all outputs to be offset (see Table 1). The devices provide a ground-sensing function that allows the output voltages to be referenced to a remote ground.

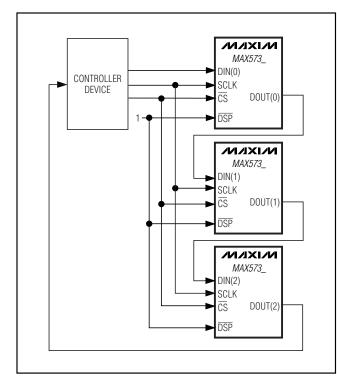

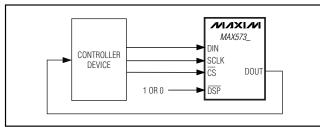

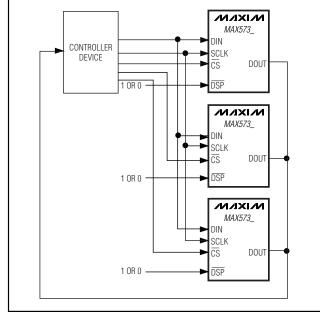

A 33MHz SPI-/QSPI/-MICROWIRE- and DSP-compatible serial interface controls the MAX5732–MAX5735 (Figure 2). Each DAC includes a double-buffered input structure to minimize the digital noise feedthrough from the digital inputs to the outputs, and allows for synchronous or asynchronous updating of the outputs. The two buffers are organized as an input register followed by a DAC register that stores the contents of the output. Input registers update the DAC registers independently or simultaneously with a single software or hardware command. The MAX5732–MAX5735 also have a DOUT that allows for read-back or daisy chaining multiple devices.

The MAX5732–MAX5735 analog and digital sections have separate power inputs. Separate power inputs are also provided for the output buffer amplifiers. Proprietary deglitch circuits prevent output glitches at power-up and eliminate the need for power sequencing. A software-shutdown mode allows efficient power management. The MAX5732–MAX5735 consume 50µA of supply current in shutdown.

All DACs provide buffered outputs that can drive  $10k\Omega$  in parallel with 100pF. The MAX5732 has a 0 to +5V output range; the MAX5733 has a 0 to +10V output

range; the MAX5734 has a -2.5V to +7.5V output range; and the MAX5735 has a -5V to +5V output range.

### **External Reference Input (REF)**

The REF voltage sets the full-scale output voltage for all 32 DACs. REF accepts a  $+3V \pm 3\%$  input. Reference voltages outside these limits can result in a degradation of device performance.

REF is a buffered input. The typical input impedance is  $10M\Omega$ , and it does not vary with code. Use a high-accuracy, low-noise voltage reference such as the MAX6126AASA30 (3ppm/°C temp drift and 0.02% initial accuracy) to improve static accuracy. REF does not accept AC signals.

### **Ground Sense (GS)**

The MAX5732–MAX5735 include a GS that allows the output voltages to be referenced to a remote ground. The GS input voltage range (V<sub>GS</sub>) is -0.5V to +0.5V. V<sub>GS</sub> is added to the output voltage with unity gain. The resulting output voltage must be within the valid output-voltage range set by the power supplies. See the *Output Amplifiers (OUTO–OUT31)* section for the effect of the GS inputs on the DAC outputs.

### **Offset DAC**

The MAX5732–MAX5735 feature an offset DAC that determines the output voltage range. While each part number has an output voltage range associated with it, it is the offset DAC that determines the end-point voltages of the range. Table 1 shows the offset DAC code required during power-up.

Figure 2. Serial-interface Timing

### Table 1. Offset DAC Codes

| PART NUMBER | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| MAX5732     | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| MAX5733     | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| MAX5734     | 0   | 1   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| MAX5735     | 1   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

**Note:** For the MAX5732, the maximum code for the offset DAC is 16384. For the MAX5733/MAX5734/MAX5735, the maximum code for the offset DAC is 40000.

**Note:** The offset DAC of every device can be programmed with any of the four output voltage ranges. However, the specifications in the *Electrical Characteristics* table are only guaranteed (production tested) for the offset code associated with each particular part number. For example, the MAX5734 specifications are only valid with the MAX5734 offset- DAC code shown in Table 1.

The offset DAC is summed with GS (Figure 1). The offset DAC can also cancel the offset of the output buffers. Any change in the offset DAC affects all 32 DACs.

The offset DAC is also configured identically to the other 32 DACs with an input and DAC register. Write to the offset DAC through the serial interface by using control bits C2, C1, and C0 = 001 followed by the data bits D15–D0. The CLR command affects the offset DAC as well as the other DACs.

The data format for the offset DAC codes are: control bits C2, C1, and C0 = 011, address bits A5-A0 = 100000, 7 don't-care bits, and 16 data bits as shown in Table 2.

### Output Amplifiers (OUT0-OUT31)

All DAC outputs are internally buffered. The internal buffers provide gain, improved load regulation, and transition glitch suppression for the DAC outputs. The output buffers slew at 1V/µs and can drive 10k $\Omega$  in parallel with 100pF. The output buffers are powered by AV<sub>CC</sub> and V<sub>SS</sub>. AV<sub>CC</sub> and V<sub>SS</sub> determine the maximum output voltage range of the device.

### Table 2. Serial Data Format

| CONTROL<br>BITS   | ADDRESS<br>BITS | DON'T-<br>CARE<br>BITS | DATA BITS   |

|-------------------|-----------------|------------------------|-------------|

| C2, C1,<br>AND C0 | A5–A0           | _                      | D15–D0      |

| 011               | 100000          | XXXXXXX                | See table 1 |

The input code, the voltage reference, the offset DAC output, the voltage on GS, and the gain of the output amplifier determine the output voltage. Calculate  $V_{OUT}$  as follows:

$$V_{OUT} = \frac{\text{GAIN} \times \text{V}_{\text{REF}} \times (\text{DAC code} - \text{offset DAC code})}{2^{16}} + \text{V}_{\text{GS}}$$

where GAIN = 5/3 for the MAX5732, or GAIN = 10/3 for the MAX5733/MAX5734/MAX5735.

### Load-DAC (LDAC) Input

The MAX5732–MAX5735 feature an active-low LDAC logic input that allows the outputs OUT\_ to update asynchronously. Keep LDAC high during normal operation (when the device is controlled only through the serial interface). Drive LDAC low to simultaneously update all DAC outputs with data from their respective input registers. Figure 3 shows the LDAC timing with respect to OUT\_.

A software command can also activate the LDAC operation. To activate LDAC by software, set control bits

C2, C1, and C0 = 010, address bits A5-A0 = 111111, and all data bits to don't care. See Table 3 for the data format. This operation updates all DAC outputs.

Note: The software load DAC does not affect the offset DAC.

### Clear (CLR)

The MAX5732–MAX5735 feature an active-low  $\overline{\text{CLR}}$  logic input that sets all channels including the offset DAC to 0V (code 0000hex). The offset DAC needs to be reprogrammed after  $\overline{\text{CLR}}$  is asserted. Driving  $\overline{\text{CLR}}$  low clears the contents of both the input and DAC registers. The serial interface can also issue a software clear command. Setting the control bits C2, C1, and C0 = 111 (Table 4) performs the same function as driving logic-input  $\overline{\text{CLR}}$  low. Table 4 shows the clear-data format for the software-controlled clear command. This register-reset process cannot be interrupted. All serial input data is ignored until the entire reset process is complete.

| CONTROL<br>BITS   | ADDRESS<br>BITS | DON'T-<br>CARE<br>BITS | DATA BITS           |

|-------------------|-----------------|------------------------|---------------------|

| C2, C1,<br>AND C0 | A5–A0           | _                      | D15–D0              |

| 010               | 111111          | XXXXXXX                | XXXXXXXXXXXXXXXXXXX |

### Table 3. Load-DAC Data Format

### Table 4. Clear-Data Format

| CONTROL<br>BITS   | ADDRESS<br>BITS | DON'T-<br>CARE<br>BITS | DATA BITS           |

|-------------------|-----------------|------------------------|---------------------|

| C2, C1,<br>AND C0 | A5–A0           | _                      | D15–D0              |

| 111               | See table 7     | XXXXXXX                | XXXXXXXXXXXXXXXXXXX |

### Table 5. Serial-Data Format

| CONTROL<br>BITS   | ADDRESS<br>BITS | DON'T-<br>CARE<br>BITS | DATA BITS |  |  |  |

|-------------------|-----------------|------------------------|-----------|--|--|--|

| MSB               |                 |                        | LSB       |  |  |  |

| C2, C1,<br>and C0 | A5-A0           | XXXXXXX                | D15-D0    |  |  |  |

### **Serial Interface**

A 3-wire SPI-/QSPI-/MICROWIRE- and DSP-compatible serial interface controls the MAX5732–MAX5735. The interface requires a 32-bit command word to control the device. The command word consists of 3 control bits, 6 address bits, 7 don't-care bits, and 16 data bits. Table 5 shows the general serial-data format. The control bits control various write and read commands as well as the load DAC and clear commands. Table 6 shows the control-bit functions. The address bits select the register(s) to be written. Table 7 shows the address functions. The data bits control the value of the DAC outputs.

### **Table 6. Control-Bit Functions**

|    | NTR<br>BITS | -  | CONTROL-BIT DESCRIPTION                                                                                                                                                                                                                                                                                                               |

|----|-------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|