### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> , IN, SHDN to GND     | 0.3V to +6V                   |

|---------------------------------------|-------------------------------|

| IN to V <sub>CC</sub>                 |                               |

| GND to PGND                           | ±0.3V                         |

| COMP, FB, TOFF, FBSEL, REF to GND0.3\ | / to (V <sub>CC</sub> + 0.3V) |

| LX Current (Note 1)                   | 5.1Å                          |

| REF Short Circuit to GND Duration     | Continuous                    |

| ESD Protection                        | ±2kV                          |

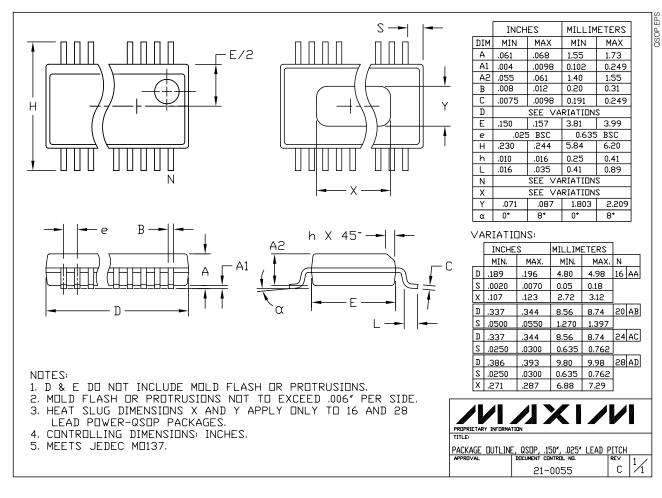

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                 |

|-------------------------------------------------------|-----------------|

| 16-Pin QSOP (derate 14mW/°C above +70°C               |                 |

| part mounted on 1in <sup>2</sup> of 1oz copper)       | 1.12W           |

| Operating Temperature Range                           | 40°C to +85°C   |

| Storage Temperature Range                             | -65°C to +150°C |

| Junction Temperature                                  |                 |

| Lead Temperature (soldering, 10s)                     | +300°C          |

Note 1: LX has internal clamp diodes to PGND and IN. Applications that forward bias the diode should take care not to exceed the IC's package power dissipation.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

(VIN = V<sub>CC</sub> = +3.3V, FBSEL = GND, T<sub>A</sub> = 0°C to +85°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                       | SYMBOL                            |                                                                             |                 | MIN               | ТҮР   | MAX             | UNITS |             |

|---------------------------------|-----------------------------------|-----------------------------------------------------------------------------|-----------------|-------------------|-------|-----------------|-------|-------------|

| Input Voltage                   | V <sub>IN</sub> , V <sub>CC</sub> |                                                                             |                 | 3.0               |       | 5.5             | V     |             |

|                                 |                                   | $V_{IN} = +3V$ to +5.5V,                                                    | FBSEL           | = V <sub>CC</sub> | 2.487 | 2.525           | 2.563 | -<br>-<br>- |

|                                 |                                   |                                                                             | FBSEL<br>unconr |                   | 1.492 | 1.515           | 1.538 |             |

| Preset Output Voltage           | Vout                              | $I_{LOAD} = 0$ to 3A,<br>$V_{FB} = V_{OUT}$                                 | FBSEL<br>(MAX1  |                   | 1.791 | 1.818           | 1.845 |             |

|                                 |                                   |                                                                             | FBSEL           | = GND             | 1.084 | 1.100           | 1.117 |             |

|                                 |                                   | $V_{IN}$ = +3.7V to +5.5V,<br>$I_{LOAD}$ = 0 to 3A,<br>$V_{FB}$ = $V_{OUT}$ | FBSEL<br>(MAX1  |                   | 3.283 | 3.333           | 3.383 |             |

| Adjustable Output Voltage Range |                                   | $V_{CC} = V_{IN} = +3V$ to +5.5V, $I_{LOAD} = 0$ ,<br>FBSEL = GND           |                 | VREF              |       | V <sub>IN</sub> | V     |             |

| AC Load Regulation Error        |                                   |                                                                             |                 |                   | 2     |                 | %     |             |

| DC Load Regulation Error        |                                   |                                                                             |                 |                   |       | 0.4             |       | %           |

| Dropout Voltage                 | V <sub>DO</sub>                   | $V_{CC} = V_{IN} = +3V$ , $I_{LOAD}$                                        | = 3A            |                   |       | 150             | 330   | mV          |

| Reference Voltage               | V <sub>REF</sub>                  |                                                                             |                 |                   | 1.089 | 1.100           | 1.111 | V           |

| Reference Load Regulation       | $\Delta V_{REF}$                  | $I_{REF} = -1\mu A \text{ to } + 10\mu A$                                   |                 |                   |       | 0.5             | 2     | mV          |

| Current-Limit Threshold         | ILIMIT                            |                                                                             |                 |                   | 4.0   | 4.8             | 5.4   | А           |

| Maximum Output RMS Current      | IOUT(RMS)                         | (Note 4)                                                                    |                 |                   |       |                 | 3.4   | А           |

| Idle Mode Current Threshold     | IIM                               |                                                                             |                 |                   | 0.2   | 0.6             | 1.0   | А           |

| PMOS Switch On-Resistance       | Davia                             | 5                                                                           |                 | $V_{IN} = 4.5V$   |       | 45              | 90    |             |

| PMOS Switch On-Resistance       | Ron, p                            | I <sub>L</sub> X = 0.5A                                                     |                 | $V_{IN} = 3V$     |       | 50              | 110   | mΩ          |

| NMOS Switch On-Resistance       | R <sub>ON</sub> , N               | $I_{LX} = 0.5A \qquad \qquad \frac{V_{IN} = 4.5V}{V_{IN} = 3V}$             |                 | $V_{IN} = 4.5V$   |       | 55              | 95    | 11152       |

|                                 |                                   |                                                                             |                 |                   | 55    | 100             |       |             |

| Switching Frequency             | f                                 | (Note 2)                                                                    |                 |                   |       | 1               | MHz   |             |

| No-Load Supply Current          | IIN + ICC                         | $V_{FB} = 1.2V$                                                             |                 |                   |       | 325             | 750   | μΑ          |

### M/IXI/M

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = V_{CC} = +3.3V, FBSEL = GND, T_A = 0^{\circ}C \text{ to } +85^{\circ}C, unless otherwise noted. Typical values are at T_A = +25^{\circ}C.)$

| PARAMETER                      | SYMBOL            | CONDITIONS                                                                       | MIN                            | ТҮР                | MAX                            | UNITS  |

|--------------------------------|-------------------|----------------------------------------------------------------------------------|--------------------------------|--------------------|--------------------------------|--------|

| Ohuddaur Oursch, Ourset        |                   | $\overline{\text{SHDN}}$ = GND, into V <sub>CC</sub> and IN pins; LX = 0 or 3.3V |                                | 0.2                | 20                             |        |

| Shutdown Supply Current        |                   | $\overline{\text{SHDN}} = \text{GND}$ , into IN with LX = 0                      |                                | 0.2                | 20                             | μA     |

|                                |                   | $\overline{\text{SHDN}}$ = GND, into IN with LX = 3.3V                           |                                | 0.1                | 20                             |        |

| Thermal Shutdown Threshold     | T <sub>SHDN</sub> | Hysteresis = 15°C                                                                |                                | 165                |                                | °C     |

| Undervoltage Lockout Threshold | VUVLO             | V <sub>IN</sub> falling, hysteresis = 90mV                                       | 1.8                            | 2.6                | 2.8                            | V      |

| FB Input Bias Current          | I <sub>FB</sub>   | $V_{FB} = 1.2V$                                                                  | 0                              | 70                 | 300                            | nA     |

|                                |                   | $R_{TOFF} = 110 k\Omega$                                                         | 0.85                           | 1.00               | 1.15                           | μs     |

| Off-Time                       | toff              | $R_{TOFF} = 44k\Omega$                                                           | 0.3                            | 0.4                | 0.5                            | μs     |

|                                |                   | $R_{TOFF} = 440 k\Omega$                                                         | 3.0                            | 3.9                | 5.0                            | μs     |

| Startup Off-Time               |                   |                                                                                  |                                | $4 \times t_{OFF}$ |                                | μs     |

| Minimum On-Time                | ton               | (Note 2)                                                                         | 0.40                           |                    |                                | μs     |

| Soft-Start Time (Note 3)       |                   |                                                                                  |                                | 3 × 256            |                                | cycles |

| SHDN Input Current             | ISHDN             | $\overline{\text{SHDN}} = 0 \text{ or } V_{CC}$                                  | -0.5                           |                    | 0.5                            | μA     |

| SHDN Logic Input Low Voltage   | VIL               |                                                                                  |                                |                    | 0.8                            | V      |

| SHDN Logic Input High Voltage  | VIH               |                                                                                  | 2.0                            |                    |                                | V      |

| FBSEL Input Current            |                   |                                                                                  | -5                             |                    | 5                              | μA     |

|                                |                   | FBSEL = GND                                                                      |                                |                    | 0.2                            | V      |

|                                |                   | FBSEL = REF                                                                      | 0.9                            |                    | 1.3                            | V      |

| FBSEL Logic Thresholds         |                   | FBSEL = unconnected                                                              | 0.7 × V <sub>CC</sub><br>- 0.2 | ; (                | ).7 × V <sub>CC</sub><br>+ 0.2 | V      |

|                                |                   | FBSEL = V <sub>CC</sub>                                                          | V <sub>CC</sub> - 0.2          | <u>2</u> V         | ′CC + 0.2                      | V      |

### **ELECTRICAL CHARACTERISTICS**

(V<sub>IN</sub> = V<sub>CC</sub> = +3.3V, FBSEL = GND,  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 5)

| PARAMETER             | SYMBOL   | CONDITIONS                                                                |                          | MIN   | ТҮР | МАХ   | UNITS |

|-----------------------|----------|---------------------------------------------------------------------------|--------------------------|-------|-----|-------|-------|

| Input Voltage         | VIN, VCC |                                                                           |                          | 3.0   |     | 5.5   | V     |

| Preset Output Voltage |          |                                                                           | $FBSEL = V_{CC}$         | 2.475 | :   | 2.575 |       |

|                       | Vout     | $V_{IN}$ = +3V to +5.5V,<br>$I_{LOAD}$ = 0 to 3A,<br>$V_{FB}$ = $V_{OUT}$ | FBSEL =<br>unconnected   | 1.485 |     | 1.545 |       |

|                       |          |                                                                           | FBSEL = REF<br>(MAX1830) | 1.782 |     | 1.854 | V     |

|                       |          |                                                                           | FBSEL = GND              | 1.078 |     | 1.122 |       |

|                       |          | $V_{IN} = +3.7V$ to +5.5V,<br>$I_{LOAD} = 0$ to 3A,<br>$V_{FB} = V_{OUT}$ | FBSEL = REF<br>(MAX1831) | 3.267 | :   | 3.399 |       |

## **ELECTRICAL CHARACTERISTICS (continued)**

(V<sub>IN</sub> = V<sub>CC</sub> = +3.3V, FBSEL = GND, **T<sub>A</sub>** = -40°C to +85°C, unless otherwise noted.) (Note 5)

| PARAMETER                       | SYMBOL              | CON                                                               | IDITIONS        | MIN                    | TYP | MAX             | UNITS |    |

|---------------------------------|---------------------|-------------------------------------------------------------------|-----------------|------------------------|-----|-----------------|-------|----|

| Adjustable Output Voltage Range |                     | $V_{CC} = V_{IN} = +3V$ to +5.5V, $I_{LOAD} = 0$ , FBSEL<br>= GND |                 | VREF                   |     | V <sub>IN</sub> | V     |    |

| Reference Voltage               | V <sub>REF</sub>    |                                                                   |                 | 1.078                  |     | 1.122           | V     |    |

| Current-Limit Threshold         | ILIMIT              |                                                                   |                 | 3.9                    |     | 5.4             | А     |    |

| Idle Mode Current Threshold     | IМ                  |                                                                   |                 | 0.14                   |     | 1.0             | А     |    |

|                                 | R <sub>ON</sub> , p | I <sub>LX</sub> = 0.5A                                            | $V_{IN} = 4.5V$ |                        |     | 90              |       |    |

| PMOS Switch On-Resistance       |                     |                                                                   | $V_{IN} = +3V$  |                        |     | 110             |       |    |

| NMOC Curitab On Desistance      |                     |                                                                   |                 | V <sub>IN</sub> = 4.5V |     |                 | 95    | mΩ |

| NMOS Switch On-Resistance       | Ron, n              | N, N ILX = 0.5A VIN =                                             |                 |                        |     | 100             |       |    |

| No-Load Supply Current          | IIN + ICC           | $V_{FB} = 1.2V$                                                   |                 |                        |     | 750             | μA    |    |

| FB Input Bias Current           | I <sub>FB</sub>     | V <sub>FB</sub> = 1.2V                                            |                 | 0                      |     | 360             | nA    |    |

| Off-Time                        | tOFF                | $R_{TOFF} = 110 k\Omega$                                          |                 | 0.8                    |     | 1.2             | μs    |    |

Note 2: Not production tested.

Note 3: Soft-start time is measured with respect to the number of cycles on LX.

**Note 4:** This is a metal migration limit. Maximum output current may be limited by thermal capability to a lower value than this. **Note 5:** Specifications from 0°C to -40°C are guaranteed by design, not production tested.

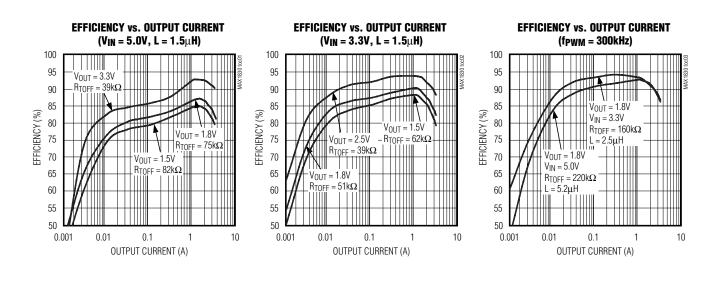

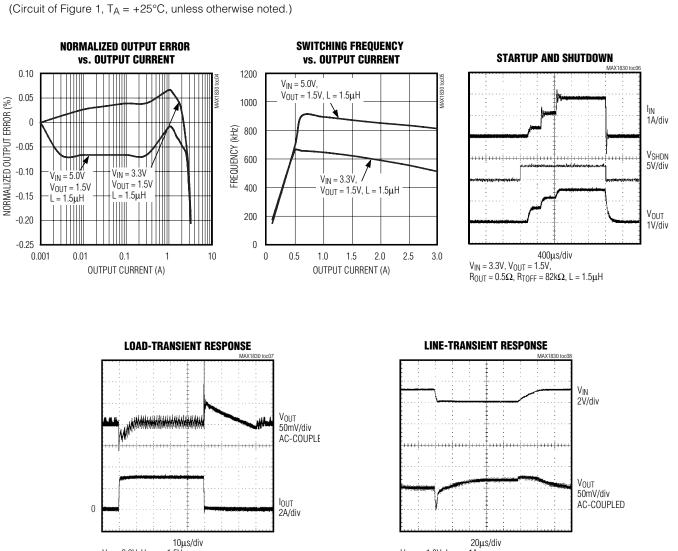

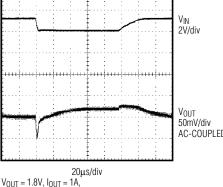

(Circuit of Figure 1,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

**Typical Operating Characteristics**

$V_{IN} = 3.3V, V_{OUT} = 1.5V,$  $R_{TOFF} = 82k\Omega$ ,  $L = 1.5\mu$ H,  $I_{OUT} = 0.1$ A TO 3A

$R_{TOFF} = 75k\Omega$ ,  $L = 1.5\mu H$

**Typical Operating Characteristics (continued)**

MAX1830/MAX1831

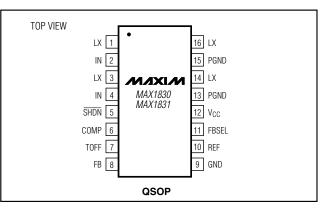

## **Pin Description**

| PIN          | NAME            | FUNCTION                                                                                                                                                                                      |

|--------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

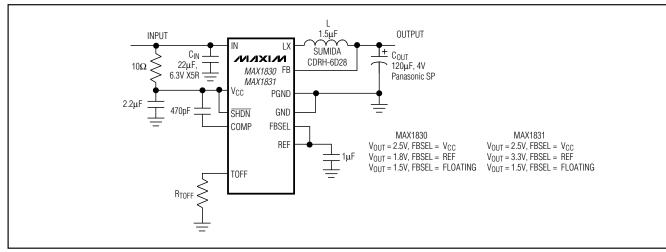

| 1, 3, 14, 16 | LX              | Connection for the drains of the PMOS power switch and NMOS synchronous-rectifier switch.<br>Connect the inductor from this node to the output filter capacitor and load.                     |

| 2, 4         | IN              | Supply Voltage Input for the internal PMOS power switch                                                                                                                                       |

| 5            | SHDN            | Shutdown Control Input. Drive $\overline{SHDN}$ low to disable the reference, control circuitry, and internal MOSFETs. Drive high or connect to V <sub>CC</sub> for normal operation.         |

| 6            | COMP            | Integrator Compensation. Connect a capacitor from COMP to V <sub>CC</sub> for integrator compensation. See <i>Integrator Amplifier</i> section.                                               |

| 7            | TOFF            | Off-Time Select Input. Sets the PMOS power switch off-time during constant-off-time operation.<br>Connect a resistor from TOFF to GND to adjust the PMOS switch off-time.                     |

| 8            | FB              | Feedback Input for both preset-output and adjustable-output operating modes. Connect directly to output for fixed-voltage operation or to a resistive divider for adjustable operating modes. |

| 9            | GND             | Analog Ground                                                                                                                                                                                 |

| 10           | REF             | Reference Output. Bypass REF to GND with a 1µF capacitor.                                                                                                                                     |

| 11           | FBSEL           | Feedback Select Input. Selects output voltage. See Table 3 for programming instructions.                                                                                                      |

| 12           | V <sub>CC</sub> | Analog Supply Voltage Input. Supplies internal analog circuitry. Bypass V <sub>CC</sub> with a 10 $\Omega$ and 2.2µF lowpass filter (Figure 1).                                               |

| 13, 15       | PGND            | Power Ground. Internally connected to the internal NMOS synchronous-rectifier switch.                                                                                                         |

## **Detailed Description**

The MAX1830/MAX1831 synchronous, current-mode, constant-off-time, PWM DC-DC converters step down input voltages of +3V to +5.5V to preset output voltages, or to an adjustable output voltage from +1.1V to V<sub>IN</sub>. The MAX1830 has preset outputs +2.5V, +1.8V, and +1.5V. The MAX1831 has preset outputs of +3.3V, +2.5V or +1.5V. Both devices deliver up to 3A of continuous output current. Internal switches composed of a 45m $\Omega$  PMOS power switch and a 55m $\Omega$  NMOS synchronous rectifier switch improve efficiency, reduce component count, and eliminate the need for an external Schottky diode.

The MAX1830/MAX1831 optimize efficiency by operating in constant-off-time mode under heavy loads and in Maxim's proprietary Idle Mode under light loads. A single resistor-programmable constant-off-time control sets switching frequencies up to 1MHz, allowing the user to optimize performance trade-offs in efficiency, switching noise, component size, and cost. Under lowdropout conditions, the device operates in a 100% duty-cycle mode, where the PMOS switch remains continuously on. Idle Mode enhances light-load efficiency by skipping cycles, thus reducing transition and gatecharge losses. When power is drawn from a regulated supply, constantoff-time PWM architecture essentially provides constantfrequency operation. This architecture has the inherent advantage of quick response to line and load transients.

The MAX1830/MAX1831 current-mode, constant-offtime PWM architecture regulates the output voltage by changing the PMOS switch on-time relative to the constant off-time. Increasing the on-time increases the peak inductor current and the amount of energy transferred to the load per pulse.

#### **Modes of Operation**

The current through the PMOS switch determines the mode of operation: constant-off-time mode (for load currents greater than half the Idle Mode threshold), or Idle Mode (for load currents less than half the Idle Mode threshold). Current sense is achieved through a proprietary architecture that eliminates current-sensing  $I^2R$  losses.

#### Constant-Off-Time Mode

Constant-off-time operation occurs when the current through the PMOS switch is greater than the Idle Mode threshold current (which corresponds to a load current of half the Idle Mode threshold). In this mode, the regu-

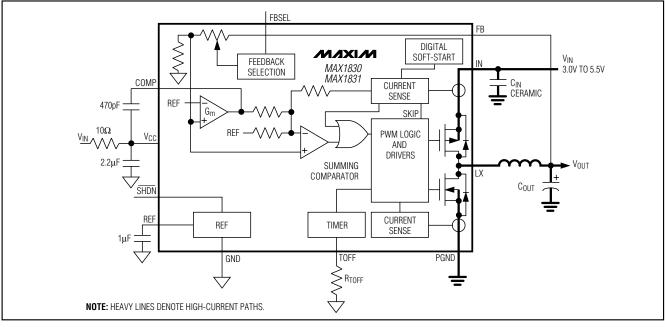

Figure 1. Typical Circuit

Figure 2. Functional Diagram

lation comparator turns the PMOS switch on at the end of each off-time, keeping the device in continuous-conduction mode. The PMOS switch remains on until the output is in regulation or the current limit is reached. When the PMOS switch turns off, it remains off for the programmed off-time (toFF). To control the current under short-circuit conditions, the PMOS switch remains off for approximately 4 x toFF when VoUT < VOUT(NOM) / 4.

#### Idle Mode

Under light loads, the devices improve efficiency by switching to a pulse-skipping Idle Mode. Idle Mode operation occurs when the current through the PMOS switch is less than the Idle Mode threshold current. Idle Mode forces the PMOS to remain on until the current through the switch reaches the Idle Mode threshold, thus minimizing the unnecessary switching that degrades efficiency under light loads. In Idle Mode, the

M/IXI/M

| V <sub>IN</sub> (V) | V <sub>OUT</sub> (V) | f <sub>PWM</sub> (kHz) | L (µH) | <b>R</b> TOFF ( <b>k</b> Ω) |

|---------------------|----------------------|------------------------|--------|-----------------------------|

| 5                   | 3.3                  | 800                    | 2.2    | 39                          |

| 5                   | 2.5                  | 865                    | 2.2    | 56                          |

| 5                   | 1.8                  | 850                    | 2.2    | 75                          |

| 5                   | 1.5                  | 860                    | 2.2    | 82                          |

| 5                   | 1.1                  | 625                    | 2.2    | 130                         |

| 3.3                 | 2.5                  | 570                    | 1.5    | 39                          |

| 3.3                 | 1.8                  | 850                    | 1.5    | 51                          |

| 3.3                 | 1.5                  | 860                    | 1.5    | 62                          |

| 3.3                 | 1.1                  | 680                    | 1.5    | 100                         |

#### Table 1. Recommended Component Values (IOUT = 3.0A)

device operates in discontinuous conduction. Currentsense circuitry monitors the current through the NMOS synchronous switch, turning it off before the current reverses. This prevents current from being pulled from the output filter through the inductor and NMOS switch to ground. As the device switches between operating modes, no major shift in circuit behavior occurs.

#### 100% Duty-Cycle Operation

When the input voltage drops near the output voltage, the duty cycle increases until the PMOS MOSFET is on continuously. The dropout voltage in 100% duty cycle is the output current multiplied by the on-resistance of the internal PMOS switch and parasitic resistance in the inductor. The PMOS switch remains on continuously as long as the current limit is not reached.

#### Internal Digital Soft-Start Circuit

Soft-start allows a gradual increase of the current-limit level at startup to reduce input-surge currents. The MAX1830/MAX1831 contain internal digital soft-start circuits, controlled by a counter, a digital-to-analog converter (DAC), and the current-limit comparator. At power-on or in shutdown mode, the soft-start counter is reset to zero. When the MAX1830/MAX1831 are enabled or powered up, its counter starts counting LX switching cycles, and the DAC begins incrementing the comparison voltage applied to the current-limit comparator. The DAC ramps up the internal current limit in four 25% steps, as the count increases to 256 cycles. As a result, the main output capacitor charges up relatively slowly. The exact time of the output rise depends on nominal switching frequency, output capacitance, and the load current, and is typically 1ms.

#### Shutdown

Drive SHDN to a logic-level low to place the MAX1830/MAX1831 in low-power shutdown mode and

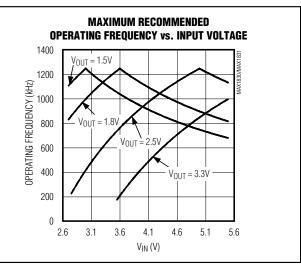

Figure 3. Maximum Recommended Operating Frequency vs. Input Voltage

reduce supply current to less than 1 $\mu$ A. In shutdown, all circuitry and internal MOSFETs turn off, and the LX node becomes high impedance. Drive SHDN to a logic-level high or connect to V<sub>CC</sub> for normal operation.

#### **Summing Comparator**

Three signals are added together at the input of the summing comparator (Figure 2): an output-voltage error signal relative to the reference voltage, an integrated output-voltage error correction signal, and the sensed PMOS switch current. The integrated error signal is provided by a transconductance amplifier with an external capacitor at COMP. This integrator provides high DC accuracy without the need for a high-gain amplifier. Connecting a capacitor at COMP modifies the overall loop response (see *Integrator Amplifier*).

| Р               | OUTPUT VOLTAGE (V) |            |         |  |

|-----------------|--------------------|------------|---------|--|

| FBSEL           | FB                 | MAX1830    | MAX1831 |  |

| V <sub>CC</sub> | Output voltage     | 2.5        | 2.5     |  |

| Unconnected     | Output voltage     | 1.5        | 1.5     |  |

| REF             | Output voltage     | 1.8        | 3.3     |  |

| GND             | Resistive divider  | Adjustable |         |  |

#### **Table 2. Output Voltage Programming**

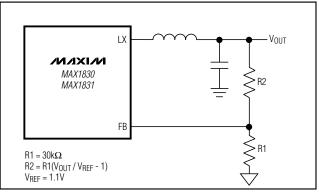

Figure 4. Adjustable Output Voltage

#### Synchronous Rectification

In a step-down regulator without synchronous rectification, an external Schottky diode provides a path for current to flow when the inductor is discharging. Replacing the Schottky diode with a low-resistance NMOS synchronous switch reduces conduction losses and improves efficiency.

The NMOS synchronous-rectifier switch turns on following a short delay after the PMOS power switch turns off, thus preventing cross conduction or "shoot through." In constant-off-time mode, the synchronous-rectifier switch turns off just prior to the PMOS power switch turning on. While both switches are off, inductor current flows through the internal-body diode of the NMOS switch. The internal-body diode's forward voltage is relatively high. An external Schottky diode from PGND to LX can improve efficiency.

#### **Thermal Resistance**

Junction-to-ambient thermal resistance,  $\theta_{JA}$ , is highly dependent on the amount of copper area immediately surrounding the IC leads. The MAX1830/MAX1831 evaluation kit has 0.7in<sup>2</sup> of copper area and a thermal resistance of +71°C/W with no forced airflow. Airflow over the board significantly reduces the junction-to-ambient thermal resistance. For heatsinking purposes,

evenly distribute the copper area connected at the IC among the high-current pins.

#### **Power Dissipation**

Power dissipation in the MAX1830/MAX1831 is dominated by conduction losses in the two internal power switches. Power dissipation due to supply current in the control section and average current used to charge and discharge the gate capacitance of the internal switches (i.e., switching losses) is approximately:

$$P_{DS} = C \times V_{IN}^2 \times f_{PWN}$$

where C = 5nF and  $f_{PWM}$  is the switching frequency in PWM mode.

This number is reduced when the switching frequency decreases as the part enters Idle Mode. Combined conduction losses in the two power switches are approximated by:

$$P_D = I_{OUT}^2 \times R_{PMOS}$$

where RPMOS is the on-resistance of the PMOS switch.

The junction-to-ambient thermal resistance required to dissipate this amount of power is calculated by:

$$\theta_{JA} = (T_{J,MAX} - T_{A,MAX}) / P_{D(TOT)}$$

where:

$\theta_{JA}$  = junction-to-ambient thermal resistance

$T_{J,MAX}$  = maximum junction temperature

$T_{A,MAX}$  = maximum ambient temperature

$P_{D(TOT)} = total losses$

### Design Procedure

For typical applications, use the recommended component values in Table 1. For other applications, take the following steps:

- Select the desired PWM-mode switching frequency; 1MHz is a good starting point. See Figure 3 for maximum operating frequency.

- 2) Select the constant off-time as a function of input voltage, output voltage, and switching frequency.

- 3) Select RTOFF as a function of off-time.

- 4) Select the inductor as a function of output voltage, off-time, and peak-to-peak inductor current.

#### Setting the Output Voltage

The output of the MAX1830/MAX1831 is selectable between one of three preset output voltages. For a preset output voltage, connect FB to the output voltage and connect FBSEL as indicated in Table 2. For an adjustable output voltage, connect FBSEL to GND and connect FB to a resistive divider between the output

##

voltage and ground (Figure 4). Regulation is maintained for adjustable output voltages when  $V_{FB} = V_{REF}$ . Use  $30k\Omega$  for R1. R2 is given by the equation:

$$R2 = R1 \left( \frac{V_{OUT}}{V_{REF}} - 1 \right)$$

where VREF is typically 1.1V.

#### Programming the Switching Frequency and Off-Time

The MAX1830/MAX1831 feature a programmable PWM mode-switching frequency, which is set by the input and output voltage and the value of RTOFF, connected from TOFF to GND. RTOFF sets the PMOS power switch off-time in PWM mode. Use the following equation to select the off-time according to your desired switching frequency in PWM mode:

$$t_{OFF} = \frac{(V_{IN} - V_{OUT} - V_{PMOS})}{f_{PWM}(V_{IN} - V_{PMOS} + V_{NMOS})}$$

where:

tOFF = the programmed off-time

VIN = the input voltage

Vout = the output voltage

VPMOS = the voltage drop across the internal PMOS power switch

V<sub>NMOS</sub> = the voltage drop across the internal NMOS synchronous-rectifier switch

fPWM = switching frequency in PWM mode

Select RTOFF according to the formula:

RTOFF = (tope - 0.07 $\mu$ s) (110k $\Omega$  / 1.00 $\mu$ s)

Recommended values for RTOFF range from 36k $\Omega$  to 430k $\Omega$  for off-times of 0.4  $\mu s$  to 4  $\mu s.$

#### Inductor Selection

The key inductor parameters must be specified: inductor value (L) and peak current (IPEAK). The following equation includes a constant, denoted as LIR, which is the ratio of peak-to-peak inductor AC current (ripple current) to maximum DC load current. A higher value of LIR allows smaller inductance but results in higher losses and ripple. A good compromise between size and losses is found at approximately a 25% ripple-current to load-current ratio (LIR = 0.25), which corresponds to a peak-inductor current 1.125 times the DC load current:

$$L = \frac{V_{OUT} \times t_{OFF}}{I_{OUT} \times LIR}$$

where:

IOUT = maximum DC load current

LIR = ratio of peak-to-peak AC inductor current to DC load current, typically 0.25

The peak-inductor current at full load is  $1.125 \times I_{OUT}$  if the above equation is used; otherwise, the peak current is calculated by:

$$I_{PEAK} = I_{OUT} + \frac{V_{OUT} \times t_{OFF}}{2 \times L}$$

Choose an inductor with a saturation current at least as high as the peak-inductor current. The inductor you select should exhibit low losses at your chosen operating frequency.

#### **Capacitor Selection**

The input-filter capacitor reduces peak currents and noise at the voltage source. Use a low-ESR and low-ESL capacitor located no further than 5mm from IN. Select the input capacitor according to the RMS input ripple-current requirements and voltage rating:

$$I_{RIPPLE} = I_{LOAD} \frac{\sqrt{V_{OUT}(V_{IN} - V_{OUT})}}{V_{IN}}$$

where IRIPPLE = input RMS current ripple.

The output-filter capacitor affects the output-voltage ripple, output load-transient response, and feedback-loop stability. For stable operation, the MAX1830/MAX1831 require a minimum output ripple voltage of VRIPPLE  $\geq$  1%  $\times$  VOUT.

The minimum ESR of the output capacitor should be:

$$ESR > 1\% \times \frac{L}{t_{OFF}}$$

Stable operation requires the correct output-filter capacitor. When choosing the output capacitor, ensure that:

$$C_{OUT} \ge \frac{t_{OFF}}{V_{OUT}}$$

79µFV/µs

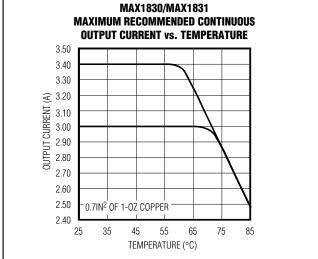

Figure 5. Maximum Recommended Continuous Output Current vs. Temperature

#### **Integrator Amplifier**

An internal transconductance amplifier fine tunes the output DC accuracy. A capacitor, C<sub>COMP</sub>, from COMP to V<sub>CC</sub> compensates the transconductance amplifier. For stability, choose C<sub>COMP</sub> = 470pF.

A large capacitor value maintains a constant average output voltage but slows the loop response to changes in output voltage. A small capacitor value speeds up the loop response to changes in output voltage but decreases stability.

**High-Current Thermal Considerations** High ambient temperatures can limit the maximum current or duty factor of the output current, depending on the total copper, are connected to the MAX1830/ MAX1831 and available airflow.

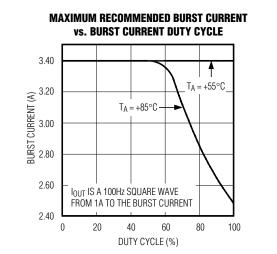

Figure 5 shows the maximum recommended continuous output current vs. ambient temperature. Figure 6 shows the maximum recommended output current vs. the output current duty cycle at high temperatures. These figures are based on 0.7in<sup>2</sup> of 1oz copper in free air.

Figure 6 assumes that the output current is a square wave with a 100Hz frequency. The duty cycle is defined as the duration of the burst current divided by the period of the square wave. This figure shows the limitations for continuous bursts of output current.

Note that if the thermal limitations of the MAX1830/ MAX1831 are exceeded, it enters thermal shutdown to prevent destructive failure.

Figure 6. Maximum Recommended Burst Current vs. Burst Current Duty Cycle

#### Frequency Variation with Output Current

The operating frequency of the MAX1830/MAX1831 is determined primarily by topp (set by RTOFF), VIN, and VOUT as shown in the following formula:

$$f_{PWM} = \frac{(V_{IN} - V_{OUT} - V_{PMOS})}{[t_{OFF}(V_{IN} - V_{PMOS} + V_{NMOS})]}$$

However, as the output current increases, the voltage drop across the NMOS and PMOS switches increases and the voltage across the inductor decreases. This causes the frequency to drop. The change in frequency can be approximated with the following formula:

$$\Delta f_{PWM} = -I_{OUT} \times R_{PMOS} / (V_{IN} \times t_{OFF})$$

where  $\mathsf{R}_{PMOS}$  is the resistance of the internal MOSFETs (50m $\Omega$  typ).

#### **Circuit Layout and Grounding**

Good layout is necessary to achieve the MAX1830/ MAX1831s' intended output power level, high efficiency, and low noise. Good layout includes the use of a ground plane, careful component placement, and correct routing of traces using appropriate trace widths.

The following points are in order of decreasing importance:

- 1) Minimize switched-current and high-current ground loops. Connect the input capacitor's ground, the output capacitor's ground, and PGND. Connect the resulting island to GND at only one point.

- 2) Connect the input filter capacitor less than 5mm away from IN. The connecting copper trace carries large currents and must be at least 1mm wide, preferably 2.5mm.

- 3) Place the LX node components as close together and as near to the device as possible. This reduces resistive and switching losses as well as noise.

- 4) A ground plane is essential for optimum performance. In most applications, the circuit is located on a multilayer board, and full use of the four or more layers is recommended. Use the top and bottom layers for interconnections and the inner layers for an uninterrupted ground plane. Avoid large AC currents through the ground plane.

MAX1830/MAX1831

### Pin Configuration

### **Chip Information**

TRANSISTOR COUNT: 3662

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2001 Maxim Integrated Products

Printed USA

is a registered trademark of Maxim Integrated Products.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated: <u>MAX1830EEE+</u> MAX1831EEE+ MAX1830EEE+T MAX1831EEE+T