#### **ABSOLUTE MAXIMUM RATINGS**

| V+ to GNDVCC, VDD to GND          | 0.3V to +6V               |

|-----------------------------------|---------------------------|

| D0-D4, ZMODE, VGATE, OVP, SUS, to | GND0.3V to +6V            |

| SKP/SDN to GND                    | 0.3V to +16V              |

| ILIM, CC, REF, POS, NEG, S1, S0,  |                           |

| TON, TIME to GND                  | 0.3V to $(V_{CC} + 0.3V)$ |

| DL to GND                         | 0.3V to $(V_{DD} + 0.3V)$ |

| BST to GND                        | 0.3V to +36V              |

| DH to LX                          | 0.3V to (BST + $0.3V$ )   |

| LX to BST                           | 6V to +0.3V   |

|-------------------------------------|---------------|

| REF Short Circuit to GND            | Continuous    |

| Continuous Power Dissipation        |               |

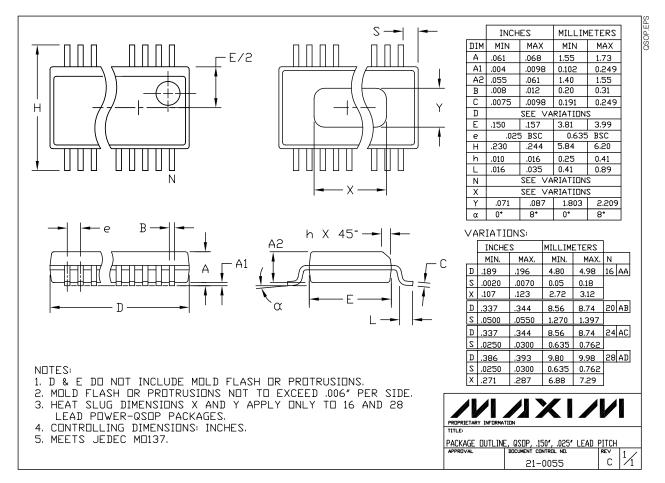

| 28-Pin QSOP (derate 10.8mW/°C above | e +70°C)860mW |

| Operating Temperature Range         | 40°C to +85°C |

| Junction Temperature                | +150°C        |

| Storage Temperature                 |               |

| Lead Temperature (soldering, 10s)   | +300°C        |

|                                     |               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1, V+ = 15V, V<sub>CC</sub> = V<sub>DD</sub> = SKP/SDN = 5V, V<sub>OUT</sub> = 1.25V, T<sub>A</sub> = 0°C to +85°C, unless otherwise noted.)

| PARAMETER                                   | CONDITIONS                                                       |                         |                            | MIN  | TYP  | MAX  | UNITS |

|---------------------------------------------|------------------------------------------------------------------|-------------------------|----------------------------|------|------|------|-------|

| PWM CONTROLLER                              | l .                                                              |                         |                            |      |      |      |       |

| Innut Valtage Dange                         | Battery voltage, V+                                              |                         | 2                          |      | 28   | V    |       |

| Input Voltage Range                         | V <sub>CC</sub> , V <sub>DD</sub>                                |                         |                            | 4.5  |      | 5.5  | ] V   |

| DC Output Voltage Accuracy                  | V+ = 4.5V to 28V, includes load                                  | DAC                     | codes from 0.9V to 1.75V   | -1   |      | +1   | %     |

| Do Guipat Voltage Accordey                  | regulation error                                                 | DAC                     | codes from 0.6V to 0.875V  | -1.5 |      | +1.5 | %     |

| Line Regulation Error                       | $V_{CC} = 4.5V \text{ to } 5.5V, V_{CC}$                         | / <sub>BATT</sub> =     | 4.5V to 28V                |      | 5    |      | mV    |

| Input Bias Current                          | FB, POS, NEG                                                     |                         |                            | -0.2 |      | +0.2 | μΑ    |

| POS, NEG Common-Mode Range                  |                                                                  |                         |                            | 0.4  |      | 2.5  | V     |

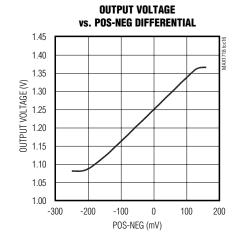

| POS, NEG Differential Range                 | POS - NEG                                                        |                         |                            | -80  |      | +80  | mV    |

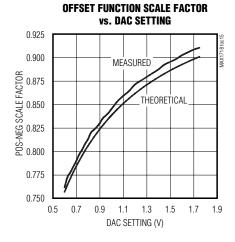

| POS, NEG Offset Gain                        | $\Delta V_{FB}$ / (POS - NEG);                                   | POS - N                 | NEG = 50mV                 | 0.81 | 0.86 | 0.91 | V/V   |

|                                             | 150kHz nominal, RTII                                             | ME = 12                 | ?0kΩ                       | -8   |      | +8   |       |

| TIME Frequency Accuracy                     | 380kHz nominal, R <sub>TIME</sub> = 47kΩ                         |                         | -12                        |      | +12  | %    |       |

|                                             | 38kHz nominal, R <sub>TIME</sub> = 470kΩ                         |                         | -12                        |      | +12  |      |       |

|                                             | V+ = 5V, FB = 1.2V, TON = GND (1000kHz)                          |                         |                            | 230  | 260  | 290  |       |

| On Time (Note 1)                            |                                                                  |                         | TON = REF (550kHz)         | 165  | 190  | 215  | ns    |

| On-Time (Note 1)                            |                                                                  |                         | TON = open (300kHz)        | 320  | 355  | 390  |       |

|                                             |                                                                  | $TON = V_{CC} (200kHz)$ |                            | 465  | 515  | 565  |       |

| Minimum Off Time (NI-to 1)                  | TON = V <sub>CC</sub> , open, or REF (200kHz, 300kHz, or 550kHz) |                         | 200kHz, 300kHz, or 550kHz) |      | 400  | 500  |       |

| Minimum Off-Time (Note 1)                   | TON = GND (1000kH                                                | łz)                     |                            |      | 300  | 375  | ns    |

| BIAS AND REFERENCE                          |                                                                  |                         |                            |      |      |      | •     |

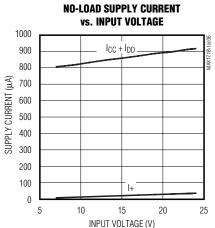

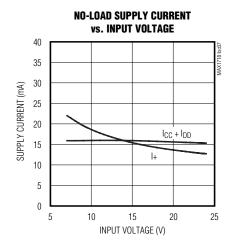

| Quiescent Supply Current (VCC)              | Measured at V <sub>CC</sub> , FE                                 | 3 forced                | above the regulation point |      | 700  | 1200 | μΑ    |

| Quiescent Supply Current (V <sub>DD</sub> ) | Measured at V <sub>DD</sub> , FE                                 | 3 forced                | above the regulation point |      | <1   | 5    | μΑ    |

| Quiescent Battery Supply<br>Current (V+)    |                                                                  |                         |                            | 25   | 40   | μΑ   |       |

| Shutdown Supply Current (VCC)               | SKP/SDN = GND                                                    |                         |                            |      | 2    | 5    | μΑ    |

| Shutdown Supply Current (V <sub>DD</sub> )  | SKP/SDN = GND                                                    |                         |                            |      | <1   | 5    | μΑ    |

| Shutdown Battery Supply<br>Current (V+)     | $SKP/\overline{SDN} = GND, V_{CC} = V_{DD} = 0V \text{ or } 5V$  |                         |                            |      | <1   | 5    | μΑ    |

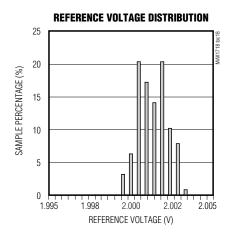

| Reference Voltage                           | $V_{CC} = 4.5V \text{ to } 5.5V, r$                              | no REF                  | load                       | 1.98 | 2    | 2.02 | V     |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1, V + = 15V,  $V_{CC} = V_{DD} = SKP/\overline{SDN} = 5V$ ,  $V_{OUT} = 1.25V$ ,  $T_A = 0^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted.)

| PARAMETER                                         | CON                                      | CONDITIONS                                   |      | TYP                 | MAX                   | UNITS |

|---------------------------------------------------|------------------------------------------|----------------------------------------------|------|---------------------|-----------------------|-------|

| Reference Load Regulation                         | $I_{REF} = 0\mu A$ to $50\mu A$          |                                              |      |                     | 0.01                  | V     |

| REF Sink Current                                  | REF in regulation                        |                                              | 10   |                     |                       | μΑ    |

| FAULT PROTECTION                                  |                                          |                                              |      |                     |                       |       |

| Overvoltage Trip Threshold                        | Measured at FB                           | Measured at FB                               |      |                     | 2.05                  | V     |

| Overvoltage Fault Propagation Delay               | FB forced 2% above trip to               | hreshold                                     |      | 10                  |                       | μs    |

| Output Undervoltage Fault<br>Protection Threshold | With respect to unloaded                 | output voltage                               | 65   | 70                  | 75                    | %     |

| Output Undervoltage Fault<br>Propagation Delay    | FB forced 2% below trip the              | nreshold                                     |      | 10                  |                       | μs    |

| Output Undervoltage Fault<br>Blanking Time        | From SKP/SDN signal goin                 | g high, clock speed set by R <sub>TIME</sub> |      | 256                 |                       | clks  |

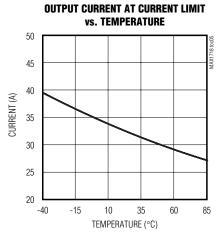

| Current-Limit Threshold Voltage                   | CNID LV II IM V                          | T <sub>A</sub> = +25°C to +85°C              | 90   | 100                 | 110                   |       |

| (Positive, Default)                               | GND - LX, ILIM = V <sub>CC</sub>         | $T_A = 0$ °C to +85°C                        | 85   |                     | 115                   | mV    |

| Current-Limit Threshold Voltage                   | GND - LX                                 | ILIM = 0.5V                                  | 35   | 50                  | 65                    |       |

| (Positive, Adjustable)                            |                                          | ILIM = REF (2V)                              | 165  | 200                 | 230                   | mV    |

| Current-Limit Threshold Voltage (Negative)        | LX - GND, ILIM = V <sub>CC</sub>         |                                              | -140 | -117                | -95                   | mV    |

| Current-Limit Threshold Voltage (Zero Crossing)   | GND - LX                                 | GND - LX                                     |      | 4                   |                       | mV    |

| Current-Limit Default<br>Switchover Threshold     |                                          |                                              | 3    | V <sub>CC</sub> - 1 | V <sub>CC</sub> - 0.4 | V     |

| Thermal Shutdown Threshold                        | Hysteresis = 10°C                        |                                              |      | 150                 |                       | °C    |

| V <sub>CC</sub> Undervoltage Lockout<br>Threshold | Rising edge, hysteresis = this level     | 20mV, PWM disabled below                     | 4.1  |                     | 4.4                   | V     |

| VGATE Lower Trip Threshold                        | Measured at FB with resp                 | ect to unloaded output voltage               | -12  | -10                 | -8                    | %     |

| VGATE Upper Trip Threshold                        | Measured at FB with resp                 | ect to unloaded output voltage               | +8   | +10                 | +12                   | %     |

| VGATE Propagation Delay                           | FB forced 2% outside VG/                 | ATE trip threshold                           |      | 10                  |                       | μs    |

| VGATE Output Low Voltage                          | Isink = 1mA                              |                                              |      |                     | 0.4                   | V     |

| VGATE Leakage Current                             | High state, forced to 5.5V               |                                              |      |                     | 1                     | μΑ    |

| GATE DRIVERS                                      | •                                        |                                              |      |                     |                       |       |

| DH Gate Driver On-Resistance                      | BST - LX forced to 5V                    |                                              |      | 1.0                 | 3.5                   | Ω     |

| DL Gate Driver On-Resistance                      | DL, high state (pullup)                  |                                              |      | 1.0                 | 3.5                   | Ω     |

| DE Gale Dilver Officesistatice                    | DL, low state (pulldown)                 |                                              |      | 0.4                 | 1.0                   | 22    |

| DH Gate-Driver Source/Sink<br>Current             | DH forced to 2.5V, BST - LX forced to 5V |                                              |      | 1.6                 |                       | А     |

| DL Gate-Driver Sink Current                       | DL forced to 2.5V                        |                                              |      | 4                   |                       | Α     |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1, V+ = 15V,  $V_{CC} = V_{DD} = SKP/\overline{SDN} = 5V$ ,  $V_{OUT} = 1.25V$ ,  $T_A = 0^{\circ}C$  to +85°C, unless otherwise noted.)

| PARAMETER                                | CONDITIONS                                               |                                                                             | MIN                   | TYP | MAX  | UNITS |

|------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------|-----|------|-------|

| DL Gate-Driver Source Current            | DL forced to 2.5V                                        |                                                                             |                       | 1.6 |      | А     |

| Dood Time                                | DL rising                                                |                                                                             | 35                    |     |      |       |

| Dead Time                                | DH rising                                                |                                                                             |                       | 26  |      | - ns  |

| LOGIC AND I/O                            |                                                          |                                                                             | '                     |     |      |       |

| Logic Input High Voltage                 | D0-D4, ZMODE, SUS, OVP                                   | DO-D4, ZMODE, SUS, OVP                                                      |                       |     |      | V     |

| Logic Input Low Voltage                  | D0-D4, ZMODE, SUS, OVP                                   |                                                                             |                       |     | 0.8  | V     |

| DAC B-Mode Programming<br>Resistor, Low  | D0-D4, 0 to 0.4V or 2.6V to 5<br>ZMODE = V <sub>CC</sub> | 5.5V applied through resistor,                                              |                       |     | 1.05 | kΩ    |

| DAC B-Mode Programming<br>Resistor, High | D0-D4, 0 to 0.4V or 2.6V to 5<br>ZMODE = V <sub>CC</sub> | D0–D4, 0 to 0.4V or 2.6V to 5.5V applied through resistor, ZMODE = $V_{CC}$ |                       |     |      | kΩ    |

| D0-D4 Pullup/Pulldown                    | Entering impedance mode Pullup Pulldown                  | Pullup                                                                      |                       | 40  |      | kΩ    |

|                                          |                                                          | Pulldown                                                                    |                       | 8   |      | K22   |

| Logic Input Current                      | D0-D4, ZMODE = GND                                       |                                                                             | -1                    |     | +1   | μA    |

| Logic input ourient                      | ZMODE, SUS, OVP                                          |                                                                             | -1                    |     | +1   | μπ    |

|                                          | For high                                                 |                                                                             | V <sub>CC</sub> - 0.4 |     |      |       |

| 4 Level Input Logic Levels               | For open                                                 |                                                                             | 3.15                  |     | 3.85 |       |

| (TON, S0, S1)                            | For REF                                                  |                                                                             | 1.65                  |     | 2.35 | ľ     |

|                                          | For low                                                  |                                                                             |                       |     | 0.5  |       |

| SKP/SDN, S0, S1, and TON Input Current   | SKP/SDN, S0, S1, TON forced to GND or V <sub>CC</sub>    |                                                                             | -3                    |     | +3   | μΑ    |

|                                          | SKP/SDN = logic high (SKIP mode)                         |                                                                             | 2.8                   |     | 6    | - V   |

| OKD ODNI                                 | SKP/SDN = open (PWM mode)                                |                                                                             | 1.4                   |     | 2.2  |       |

| SKP/SDN Input Levels                     | SKP/SDN = logic low (shutdown mode)                      |                                                                             |                       |     | 0.5  |       |

|                                          | To enable no-fault mode 12                               |                                                                             |                       |     | 15   |       |

| SKP/SDN Float Level                      | I <sub>SKP/SDN</sub> = 0µA                               |                                                                             | 1.8                   |     | 2.2  | V     |

#### **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1, V+ = 15V,  $V_{CC} = V_{DD} = SKP/\overline{SDN} = 5V$ ,  $V_{OUT} = 1.25V$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                  | CONDITIONS                             |                               |      | TYP | MAX  | UNITS |  |  |

|----------------------------|----------------------------------------|-------------------------------|------|-----|------|-------|--|--|

| PWM CONTROLLER             |                                        |                               |      |     |      |       |  |  |

| DC Output Voltage Accuracy | V+ = 4.5V to 28V, includes load        | DAC codes from 0.9V to 1.75V  | -1.5 |     | +1.5 | %     |  |  |

|                            |                                        | DAC codes from 0.6V to 0.875V | -2.0 |     | +2.0 | - %   |  |  |

|                            | 150kHz nominal, $R_{TIME} = 120kΩ$     |                               | -8   |     | +8   |       |  |  |

| TIME Frequency Accuracy    | 380kHz nominal, $R_{TIME} = 47k\Omega$ |                               | -12  |     | +12  | %     |  |  |

|                            | 38kHz nominal, $R_{TIME} = 470k\Omega$ |                               | -12  |     | +12  |       |  |  |

|                            | V+ = 5V, FB = 1.2V,                    | TON = GND (1000kHz)           | 230  |     | 290  |       |  |  |

| On-Time (Note 1)           |                                        | TON = REF (550kHz)            | 165  |     | 215  | ns    |  |  |

|                            | V+ = 12V, FB = 1.2V                    | TON = open (300kHz)           | 320  |     | 390  | 1 115 |  |  |

|                            |                                        | $TON = V_{CC} (200kHz)$       | 465  |     | 565  |       |  |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1, V+ = 15V,  $V_{CC} = V_{DD} = SKP/\overline{SDN} = 5V$ ,  $V_{OUT} = 1.25V$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                                           |                                                        | CONDITIONS                                                        |       | TYP | MAX   | UNITS |

|-----------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------|-------|-----|-------|-------|

| Minimum Off Time (NI-te 4)                          | TON = V <sub>CC</sub> , open, c                        | or REF (200kHz, 300kHz, or 550kHz)                                |       |     | 500   |       |

| Minimum Off-Time (Note 1)                           | TON = GND (1000k                                       | Hz)                                                               |       |     | 375   | ns    |

| BIAS AND REFERENCE                                  |                                                        |                                                                   |       |     |       |       |

| Quiescent Supply Current (V <sub>CC</sub> )         | Measured at V <sub>CC</sub> , F                        | easured at V <sub>CC</sub> , FB forced above the regulation point |       |     | 1300  | μΑ    |

| Quiescent Supply Current (V <sub>DD</sub> )         | Measured at V <sub>DD</sub> , F                        | B forced above the regulation point                               |       |     | 5     | μΑ    |

| Quiescent Battery Supply<br>Current (V+)            |                                                        |                                                                   |       |     | 40    | μΑ    |

| Shutdown Supply Current (V <sub>CC</sub> )          | SKP/SDN = 0                                            |                                                                   |       |     | 5     | μA    |

| Shutdown Supply Current (V <sub>DD</sub> )          | SKP/SDN = 0                                            |                                                                   |       |     | 5     | μΑ    |

| Shutdown Battery Supply<br>Current (V+)             | SKP/SDN = 0, V <sub>CC</sub> =                         | = V <sub>DD</sub> = 0 or 5V                                       |       |     | 5     | μΑ    |

| Reference Voltage                                   | $V_{CC} = 4.5V \text{ to } 5.5V,$                      | V <sub>CC</sub> = 4.5V to 5.5V, no REF load                       |       |     | 2.02  | V     |

| FAULT PROTECTION                                    |                                                        |                                                                   |       |     |       |       |

| Overvoltage Trip Threshold                          | Measured at FB                                         |                                                                   | 1.95  |     | 2.05  | V     |

| Output Undervoltage Protection<br>Threshold         | With respect to unloaded output voltage                |                                                                   | 65    |     | 75    | %     |

| Current-Limit Threshold Voltage (Positive, Default) | GND - LX, ILIM = V <sub>0</sub>                        | cc                                                                | 80    |     | 115   | mV    |

| Current-Limit Threshold Voltage                     | GND - LX                                               | ILIM = 0.5V                                                       | 33    |     | 65    | mV    |

| (Positive, Adjustable)                              | GND - LX                                               | ILIM = REF (2V)                                                   | 160   |     | 240   | IIIV  |

| Current-Limit Threshold Voltage (Negative)          | LX - GND, ILIM = V <sub>C</sub>                        | cc                                                                | -145  |     | -90   | mV    |

| V <sub>CC</sub> Undervoltage Lockout<br>Threshold   | Rising edge, hystere level                             | esis = 20mV, PWM disabled below this                              | 4.1   |     | 4.4   | V     |

| VGATE Lower Trip Threshold                          | Measured at FB with respect to unloaded output voltage |                                                                   | -12.5 |     | -7.5  | %     |

| VGATE Upper Trip Threshold                          | Measured at FB with respect to unloaded output voltage |                                                                   | +7.5  |     | +12.5 | %     |

| GATE DRIVERS                                        |                                                        |                                                                   |       |     |       |       |

| DH Gate Driver On-Resistance                        | BST - LX forced to 5V                                  |                                                                   |       |     | 3.5   | Ω     |

| DL Gate Driver On-Resistance                        | DL, high state (pullu                                  | p)                                                                |       |     | 3.5   | Ω     |

| DE Gate Differ Off-Hesistatice                      | DL, low state (pulldo                                  | own)                                                              |       |     | 1.0   | 52    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1, V + = 15V,  $V_{CC} = V_{DD} = SKP/\overline{SDN} = 5V$ ,  $V_{OUT} = 1.25V$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                                | CONDITIONS                                                             | MIN | TYP | MAX  | UNITS |

|------------------------------------------|------------------------------------------------------------------------|-----|-----|------|-------|

| LOGIC AND I/O                            | •                                                                      |     |     |      |       |

| Logic Input High Voltage                 | D0-D4, ZMODE, SUS, OVP                                                 | 2.4 |     |      | V     |

| Logic Input Low Voltage                  | D0-D4, ZMODE, SUS, OVP                                                 |     |     | 0.8  | V     |

| DAC B-Mode Programming<br>Resistor, Low  | D0–D4, 0 to 0.4V or 2.6V to 5.5V applied through resistor, ZMODE = VCC |     |     | 1.05 | kΩ    |

| DAC B-Mode Programming<br>Resistor, High | D0–D4, 0 to 0.4V or 2.6V to 5.5V applied through resistor, ZMODE = VCC | 95  |     |      | kΩ    |

Note 1: On-Time specifications are measured from 50% to 50% at the DH pin, with LX forced to 0V, BST forced to 5V, and a 500pF capacitor from DH to LX to simulate external MOSFET gate capacitance. Actual in-circuit times may be different due to MOSFET switching speeds.

**Note 2:** Specifications to  $T_A = -40^{\circ}C$  are guaranteed by design and not production tested.

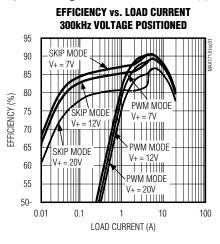

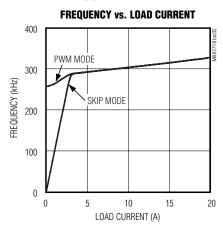

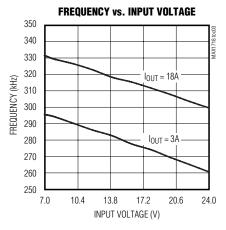

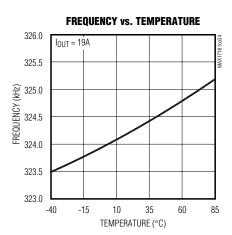

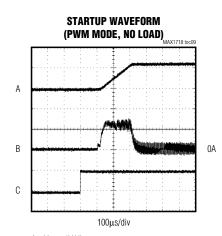

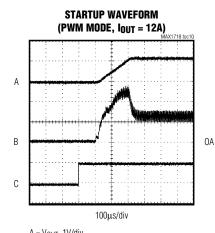

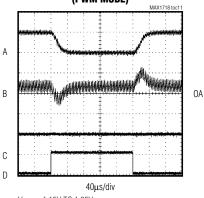

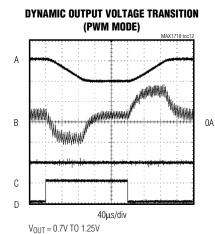

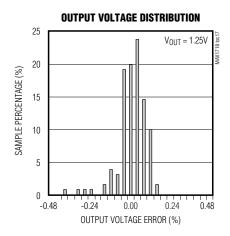

#### Typical Operating Characteristics

(Circuit of Figure 1, V+ = 12V, VDD = VCC = SKP/SDN = 5V, VOUT = 1.25V, TA = +25°C, unless otherwise noted.)

#### Typical Operating Characteristics (continued)

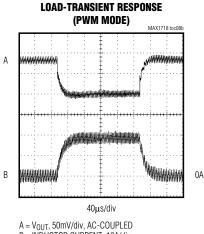

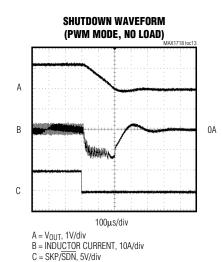

(Circuit of Figure 1, V+ = 12V, V<sub>DD</sub> = V<sub>CC</sub> = SKP/SDN = 5V, V<sub>OUT</sub> = 1.25V, T<sub>A</sub> = +25°C, unless otherwise noted.)

B = INDUCTOR CURRENT, 10A/div

B = INDUCTOR CURRENT, 10A/div

$$\begin{split} A &= V_{OUT}, \, 1V/div \\ B &= INDU\underline{CTO}R \,\, CURRENT, \, 10A/div \end{split}$$

$C = SKP/\overline{SDN}, 5V/div$

$$\begin{split} A &= V_{OUT}, \, 1V/div \\ B &= INDU\underline{CTO}R \,\, CURRENT, \, 10A/div \end{split}$$

$C = SKP/\overline{SDN}, 5V/div$

#### **DYNAMIC OUTPUT VOLTAGE TRANSITION** (PWM MODE)

V<sub>OUT</sub> = 1.15V TO 1.25V  $I_{OUT}=3A,\,R_{TIME}=62k\Omega$

$A = V_{OUT}$ , 100mV/div, AC-COUPLED B = INDUCTOR CURRENT, 10A/div

C = VGATE, 5V/div

D = ZMODE, 5V/div

#### Typical Operating Characteristics (continued)

(Circuit of Figure 1, V+ = 12V, V<sub>DD</sub> = V<sub>CC</sub> = SKP/SDN = 5V, V<sub>OUT</sub> = 1.25V, T<sub>A</sub> = +25°C, unless otherwise noted.)

$I_{OUT} = 3A$ ,  $R_{TIME} = 62k\Omega$  $A = V_{OUT}$ , 500mV/div, AC-COUPLED

B = INDUCTOR CURRENT, 10A/div

C = VGATE, 5V/div

$D = \overline{SUS}$ , 5V/div

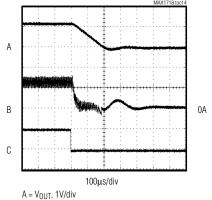

SHUTDOWN WAVEFORM

(PWM MODE, I<sub>OUT</sub> = 12A)

B = INDUCTOR CURRENT, 10A/div  $C = SKP/\overline{SDN}$ , 5V/div

#### Typical Operating Characteristics (continued)

(Circuit of Figure 1, V+ = 12V, V<sub>DD</sub> = V<sub>CC</sub> = SKP/SDN = 5V, V<sub>OUT</sub> = 1.25V, T<sub>A</sub> = +25°C, unless otherwise noted.)

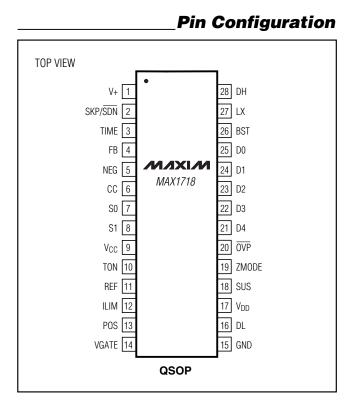

#### **Pin Description**

| PIN  | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | V+      | Battery Voltage Sense Connection. Connect V+ to input power source. V+ is used only for PWM one-shot timing. DH on-time is inversely proportional to input voltage over a range of 2V to 28V.                                                                                                                                                                                                                                                                                                                                            |

| 2    | SKP/SDN | Combined Shutdown and Skip-Mode Control. Drive SKP/SDN to GND for shutdown. Leave SKP/SDN open for low-noise forced-PWM mode, or drive to V <sub>CC</sub> for pulse-skipping operation. Low-noise forced-PWM mode causes inductor current recirculation at light loads and suppresses pulse-skipping operation. Forcing SKP/SDN to 12V to 15V disables both the overvoltage protection and undervoltage protection circuits and clears the fault latch, with otherwise normal pulse-skipping operation. Do not connect SKP/SDN to > 15V. |

| 3    | TIME    | Slew-Rate Adjustment Pin. Connect a resistor from TIME to GND to set the internal slew-rate clock. A 470k $\Omega$ to 47k $\Omega$ resistor sets the clock from 38kHz to 380kHz, f <sub>SLEW</sub> = 150kHz × 120k $\Omega$ / R <sub>TIME</sub> .                                                                                                                                                                                                                                                                                        |

| 4    | FB      | Feedback Input. Connect FB to the junction of the external inductor and the positioning resistor (Figure 1).                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5    | NEG     | Feedback Offset Adjust Negative Input. The output shifts by an amount equal to the difference between POS and NEG multiplied by a scale factor that depends on the DAC codes (see the <i>Integrator Amplifiers/Output Voltage Offsets</i> section). Connect both POS and NEG to REF if the offset function is not used.                                                                                                                                                                                                                  |

| 6    | CC      | Integrator Capacitor Connection. Connect a 47pF to 1000pF (47pF typ) capacitor from CC to GND to set the integration time constant (see the <i>Integrator Amplifiers/Output Voltage Offsets</i> section).                                                                                                                                                                                                                                                                                                                                |

| 7, 8 | S0, S1  | Suspend-Mode Voltage Select Input. S0 and S1 are four-level digital inputs that select the suspend-mode VID code for the suspend-mode multiplexer inputs. If SUS is high, the suspend-mode VID code is delivered to the DAC (see the <i>Internal Multiplexers (ZMODE/SUS)</i> section).                                                                                                                                                                                                                                                  |

| 9    | Vcc     | Analog Supply Voltage Input for PWM Core. Connect $V_{CC}$ to the system supply voltage (4.5V to 5.5V) with a series $20\Omega$ resistor. Bypass to GND with a 0.22µF (min) capacitor.                                                                                                                                                                                                                                                                                                                                                   |

#### Pin Description (continued)

| PIN   | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10    | TON             | On-Time Selection Control Input. This is a four-level input that sets the K factor (Table 2) to determine DH on-time. Connect TON to the following pins for the indicated operation:  GND = 1000kHz  REF = 550kHz  Open = 300kHz  VCC = 200kHz                                                                                                                                                                                                                                                                                       |

| 11    | REF             | 2V Reference Output. Bypass to GND with 0.22μF (min) capacitor. Can source 50μA for external loads. Loading REF degrades FB accuracy according to the REF load-regulation error.                                                                                                                                                                                                                                                                                                                                                     |

| 12    | ILIM            | Current-Limit Adjustment. The GND - LX current-limit threshold defaults to 100mV if ILIM is connected to $V_{CC}$ . In adjustable mode, the current-limit threshold voltage is 1/10th the voltage seen at ILIM over a 0.5V to 3V range. The logic threshold for switchover to the 100mV default value is approximately $V_{CC}$ - 1V. Connect ILIM to REF for a fixed 200mV threshold.                                                                                                                                               |

| 13    | POS             | Feedback Offset Adjust Negative Input. The output shifts by an amount equal to the difference between POS and NEG multiplied by a scale factor that depends on the DAC codes (see the <i>Integrator Amplifiers/Output Voltage Offsets</i> section). Connect both POS and NEG to REF if the offset function is not used.                                                                                                                                                                                                              |

| 14    | VGATE           | Open-Drain Power-Good Output. VGATE is normally high when the output is in regulation. If VFB is not within a ±10% window of the DAC setting, VGATE is asserted low. During DAC code transitions, VGATE is forced high until 1 clock period after the slew-rate controller finishes the transition. VGATE is low during shutdown.                                                                                                                                                                                                    |

| 15    | GND             | Analog and Power Ground. Also connects to the current-limit comparator.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 16    | DL              | Low-Side Gate Driver Output. DL swings GND to V <sub>DD</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 17    | V <sub>DD</sub> | Supply Voltage Input for the DL Gate Driver, 4.5V to 5.5V. Bypass to GND with a 1µF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 18    | SUS             | Suspend-Mode Control Input. When SUS is high, the suspend-mode VID code, as programmed by S0 and S1, is delivered to the DAC. Connect SUS to GND if the Suspend-mode multiplexer is not used (see the <i>Internal Multiplexers (ZMODE/SUS)</i> section).                                                                                                                                                                                                                                                                             |

| 19    | ZMODE           | Performance-Mode MUX Control Input. If SUS is low, ZMODE selects between two different VID DAC codes. If ZMODE is low, the VID DAC code is set by the logic-level voltages on D0–D4. On the rising edge of ZMODE, during power-up with ZMODE high, or on the falling edge of SUS when ZMODE is high, the VID DAC code is determined by the impedance at D0–D4 (see the <i>Internal Multiplexers (ZMODE/SUS)</i> section).                                                                                                            |

| 20    | OVP             | Overvoltage Protection Control Input. Connect $\overline{\text{OVP}}$ low to enable overvoltage protection. Connect $\overline{\text{OVP}}$ high to disable overvoltage protection. The overvoltage trip threshold is approximately 2V. The state of $\overline{\text{OVP}}$ does not affect output undervoltage fault protection or thermal shutdown.                                                                                                                                                                               |

| 21–25 | D4-D0           | VID DAC Code Inputs. D0 is the LSB, and D4 is the MSB of the internal 5-bit VID DAC (Table 3). If ZMODE is low, D0–D4 are high-impedance digital inputs, and the VID DAC code is set by the logic-level voltages on D0–D4. On the rising edge of ZMODE, during power-up with ZMODE high, or on the falling edge of SUS when ZMODE is high, the VID DAC code is determined by the impedance at D0–D4 as follows: Logic low = source impedance is $\leq 1 k\Omega + 5\%$ . Logic high = source impedance is $\geq 100 k\Omega - 5\%$ . |

| 26    | BST             | Boost Flying Capacitor Connection. Connect BST to the external boost diode and capacitor as shown in Figure 1. An optional resistor in series with BST allows the DH pullup current to be adjusted (Figure 8).                                                                                                                                                                                                                                                                                                                       |

| 27    | LX              | Inductor Connection. LX is the internal lower supply rail for the DH high-side gate driver. It also connects to the current-limit comparator and the skip-mode zero-crossing comparator.                                                                                                                                                                                                                                                                                                                                             |

| 28    | DH              | High-Side Gate-Driver Output. DH swings LX to BST.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

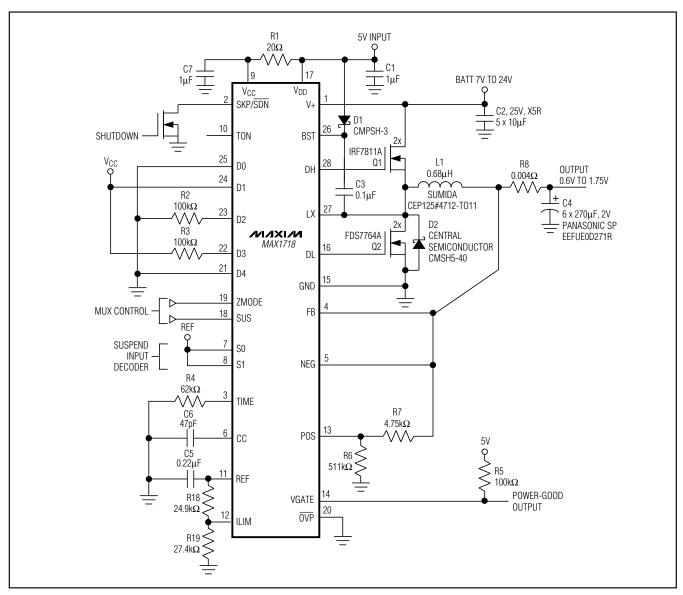

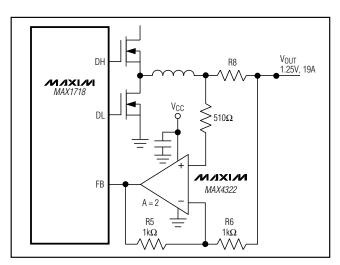

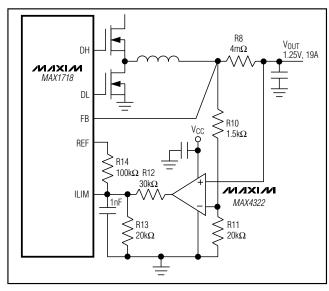

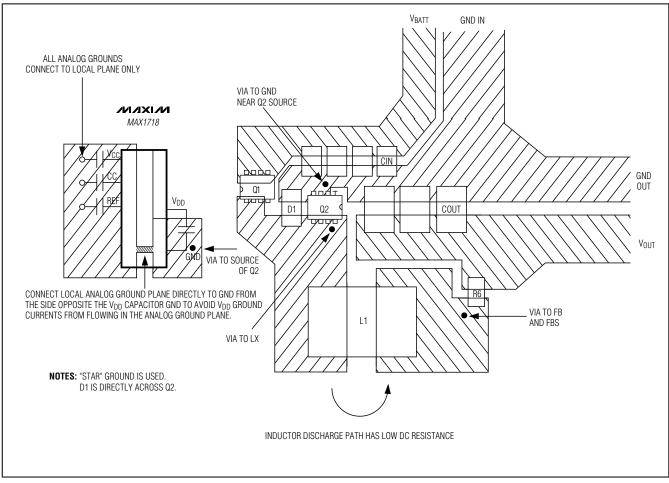

Figure 1. Standard Application Circuit

**Table 1. Component Suppliers**

| MANUFACTURER            | USA PHONE    | FACTORY FAX  |

|-------------------------|--------------|--------------|

| Central Semiconductor   | 516-435-1110 | 516-435-1824 |

| Dale-Vishay             | 402-564-3131 | 402-563-6418 |

| Fairchild               | 408-721-2181 | 408-721-1635 |

| International Rectifier | 310-322-3331 | 310-322-3332 |

| Kemet                   | 408-986-0424 | 408-986-1442 |

| Motorola                | 602-303-5454 | 602-994-6430 |

| Nihon                   | 847-843-7500 | 847-843-2798 |

| Panasonic               | 714-373-7939 | 714-373-7183 |

| Taiyo Yuden             | 408-573-4150 | 408-573-4159 |

| TDK                     | 847-390-4373 | 847-390-4428 |

| Toko                    | 800-745-8656 | 408-943-9790 |

| Sanyo                   | 619-661-6835 | 619-661-1055 |

| SGS-Thomson             | 617-259-0300 | 617-259-9442 |

| Sumida                  | 708-956-0666 | 708-956-0702 |

| Zetex                   | 516-543-7100 | 516-864-7630 |

#### **Detailed Description**

#### 5V Bias Supply (VCC and VDD)

The MAX1718 requires an external 5V bias supply in addition to the battery. Typically, this 5V bias supply is the notebook's 95% efficient 5V system supply. Keeping the bias supply external to the IC improves efficiency and eliminates the cost associated with the 5V linear regulator that would otherwise be needed to supply the PWM circuit and gate drivers. If stand-alone capability is needed, the 5V supply can be generated with an external linear regulator.

The 5V bias supply must provide  $V_{CC}$  (PWM controller) and  $V_{DD}$  (gate-drive power), so the maximum current drawn is:

$$I_{BIAS} = I_{CC} + f(Q_{G1} + Q_{G2}) = 10mA \text{ to } 40mA \text{ (typ)}$$

where I<sub>CC</sub> is 800 $\mu$ A (typ), f is the switching frequency, and Q<sub>G1</sub> and Q<sub>G2</sub> are the MOSFET data sheet total gate-charge specification limits at V<sub>GS</sub> = 5V.

V+ and V<sub>DD</sub> can be tied together if the input power source is a fixed 4.5V to 5.5V supply. If the 5V bias supply is powered up prior to the battery supply, the enable signal (SKP/SDN going from low to high or open) must be delayed until the battery voltage is present to ensure startup.

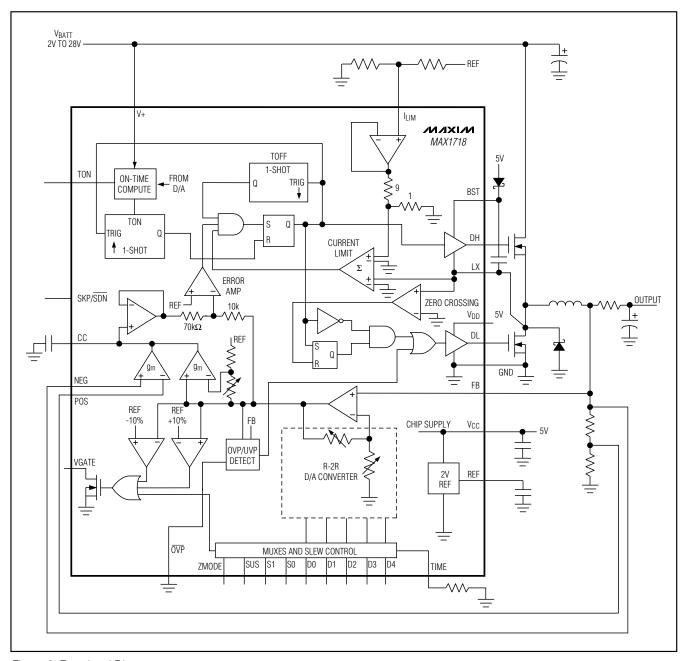

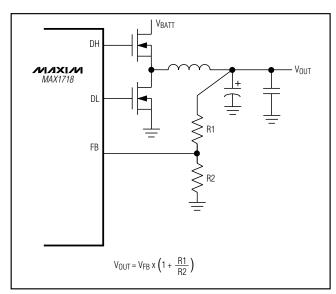

### Free-Running, Constant On-Time PWM Controller with Input Feed-Forward

The Quick-PWM control architecture is a pseudofixed-frequency, constant-on-time current-mode type with voltage feed-forward (Figure 2). This architecture relies on the output filter capacitor's ESR to act as the current-sense resistor, so the output ripple voltage provides the PWM ramp signal. The control algorithm is simple: the high-side switch on-time is determined solely by a one-shot whose period is inversely proportional to input voltage and directly proportional to output voltage. Another one-shot sets a minimum off-time (400ns typ). The on-time one-shot is triggered if the error comparator is low, the low-side switch current is below the current-limit threshold, and the minimum off-time one-shot has timed out.

#### **On-Time One-Shot (TON)**

The heart of the PWM core is the one-shot that sets the high-side switch on-time. This fast, low-jitter, adjustable one-shot includes circuitry that varies the on-time in response to battery and output voltage. The high-side switch on-time is inversely proportional to the battery voltage as measured by the V+ input, and proportional to the output voltage. This algorithm results in a nearly constant switching frequency despite the lack of a fixed-frequency clock generator. The benefits of a constant switching frequency are twofold: first, the frequency can be selected to avoid noise-sensitive regions such as the 455kHz IF band; second, the inductor ripple-current operating point remains relatively constant, resulting in easy design methodology and predictable output voltage ripple.

On-Time =

$$K (V_{OUT} + 0.075V) / V_{IN}$$

where K is set by the TON pin-strap connection and 0.075V is an approximation to accommodate the expected drop across the low-side MOSFET switch (Table 2).

The on-time one-shot has good accuracy at the operating points specified in the *Electrical Characteristics table* (±10% at 200kHz and 300kHz, ±12% at 550kHz and 1000kHz). On-times at operating points far removed from the conditions specified in the *Electrical Characteristics* table can vary over a wider range. For example, the 1000kHz setting will typically run about 10% slower with inputs much greater than +5V due to the very short ontimes required.

On-times translate only roughly to switching frequencies. The on-times guaranteed in the *Electrical Characteristics* table are influenced by switching delays in the

Figure 2. Functional Diagram

**Table 2. Approximate K-Factor Errors**

| TON             | TON<br>FREQUENCY | K-FACTOR | APPROXIMATE K-   | MIN RECOMMENDED V <sub>BATT</sub> AT  V <sub>OUT</sub> = 1.25V (V) V <sub>OUT</sub> = 1.75V |     |

|-----------------|------------------|----------|------------------|---------------------------------------------------------------------------------------------|-----|

| SETTING         | (kHZ)            | (µs)     | FACTOR ERROR (%) |                                                                                             |     |

| V <sub>CC</sub> | 200              | 5        | ±10              | 1.7                                                                                         | 2.3 |

| OPEN            | 300              | 3.3      | ±10              | 1.8                                                                                         | 2.5 |

| REF             | 550              | 1.8      | ±12.5            | 2.6                                                                                         | 3.5 |

| GND             | 1000             | 1.0      | ±12.5            | 3.6                                                                                         | 4.9 |

external high-side MOSFET. Resistive losses, including the inductor, both MOSFETs, output capacitor ESR, and PC board copper losses in the output and ground tend to raise the switching frequency at higher output currents. Also, the dead-time effect increases the effective on-time, reducing the switching frequency. It occurs only in PWM mode (SKP/SDN = open) and during dynamic output voltage transitions when the inductor current reverses at light or negative load currents. With reversed inductor current, the inductor's EMF causes LX to go high earlier than normal, extending the on-time by a period equal to the DH-rising dead time.

For loads above the critical conduction point, where the dead-time effect is no longer a factor, the actual switching frequency is:

$$f = \frac{(V_{OUT} + V_{DROP1})}{t_{ON}(V_{IN} + V_{DROP1} - V_{DROP2})}$$

where  $V_{DROP1}$  is the sum of the parasitic voltage drops in the inductor discharge path, including synchronous rectifier, inductor, and PC board resistances;  $V_{DROP2}$  is the sum of the parasitic voltage drops in the inductor charge path, including high-side switch, inductor, and PC board resistances; and  $t_{ON}$  is the on-time calculated by the MAX1718.

#### Integrator Amplifiers/Output Voltage Offsets

Two transconductance integrator amplifiers provide a fine adjustment to the output regulation point. One amplifier forces the DC average of the feedback voltage to equal the VID DAC setting. The second amplifier is used to create small positive or negative offsets from the VID DAC setting, using the POS and NEG pins.

The integrator block has the ability to lower the output voltage by 8% and raise it by 8%. For each amplifier, the differential input voltage range is at least ±80mV total, including DC offset and AC ripple. The two amplifiers' outputs are directly summed inside the chip, so the integration time constant can be set easily with one capacitor at the CC pin. Use a capacitor value of 47pF

to 1000pF (47pF typ). The  $g_m$  of each amplifier is 160µmho (typ).

The POS/NEG amplifier is used to add small offsets to the VID DAC setting or to correct for voltage drops. To create an output offset, bias POS and NEG to a voltage (typically Vout or REF) within their common-mode range, and offset them from one another with a resistive divider (Figures 3 and 4). If Vpos is higher than Vneg, then the output is shifted in the positive direction. If Vneg is higher than Vpos, then the output is shifted in the negative direction. The amount of output offset is less than the difference from POS to NEG by a scale factor that varies with the VID DAC setting as shown in Table 3. The common-mode range of POS and NEG is 0.4V to 2.5V.

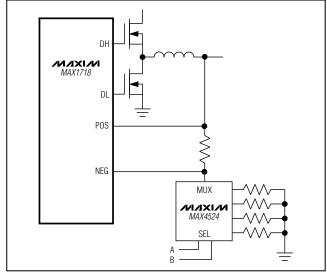

For applications that require multiple offsets, an external multiplexer can be used to select various resistor values (Figure 5).

Both the integrator amplifiers can be disabled by connecting NEG to  $\ensuremath{\text{V}_{\text{CC}}}.$

#### Forced-PWM Mode (SKP/SDN Open)

The low-noise forced-PWM mode (SKP/SDN open) disables the zero-crossing comparator, allowing the inductor current to reverse at light loads. This causes the low-side gate-drive waveform to become the complement of the high-side gate-drive waveform. The benefit of forced-PWM mode is to keep the switching frequency fairly constant, but it comes at a cost: the no-load battery current can be 10mA to 40mA, depending on the external MOSFETs and switching frequency.

Forced-PWM mode is required during downward output voltage transitions. The MAX1718 uses PWM mode during all transitions, but only while the slew-rate controller is active. Due to voltage positioning, when a transition uses high negative inductor current, the output voltage does not settle to its final intended value until well after the slew-rate controller terminates. Because of this it is possible, at very high negative slew currents, for the output to end up high enough to cause VGATE to go low.

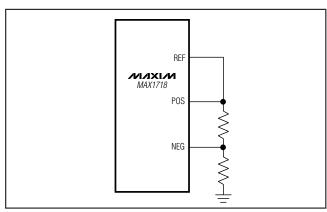

Figure 3. Resistive Divider from REF

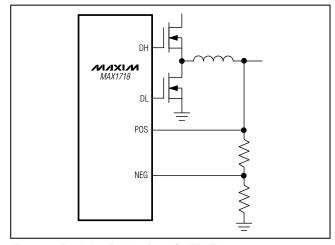

Figure 4. Resistive Divider from OUTPUT

Figure 5. Programmable Offset Voltage

Thus, it is necessary to use forced PWM mode during all negative transitions. Most applications should use PWM mode exclusively, although there is some benefit to using skip mode while in the low-power suspend state (see the *Using Skip Mode During Suspend (SKP/SDN = VCC)* section.)

#### **Automatic Pulse-Skipping Switchover**

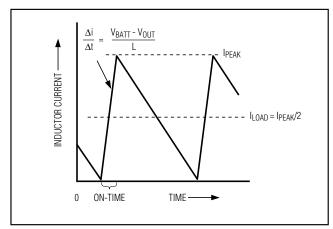

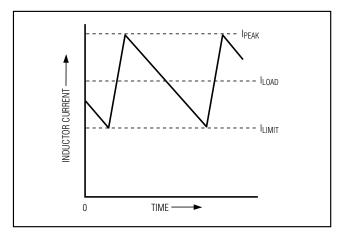

In skip mode (SKP/SDN high), an inherent automatic switchover to PFM takes place at light loads (Figure 6). This switchover is effected by a comparator that truncates the low-side switch on-time at the inductor current's zero crossing. This mechanism causes the threshold between pulse-skipping PFM and nonskipping PWM operation to coincide with the boundary between continuous and discontinuous inductor-current operation. The load-current level at which PFM/PWM crossover occurs, I<sub>LOAD</sub>(SKIP), is equal to 1/2 the peak-to-peak ripple current, which is a function of the inductor value (Figure 6). For a battery range of 7V to 24V, this threshold is relatively constant, with only a minor dependence on battery voltage:

$$I_{LOAD(SKIP)} \approx \frac{K \times V_{OUT}}{2 \times L} \times \frac{V_{BATT} - V_{OUT}}{V_{BATT}}$$

where K is the on-time scale factor (Table 2). For example, in the standard application circuit this becomes:

$$\frac{3.3\mu s \times 1.25V}{2 \times 0.68\mu H} \times \frac{12V - 1.25V}{12V} = 2.7A$$

The crossover point occurs at a lower value if a swinging (soft-saturation) inductor is used.

The switching waveforms may appear noisy and asynchronous when light loading causes pulse-skipping operation, but this is a normal operating condition that results in high light-load efficiency. Trade-offs in PFM noise vs. light-load efficiency are made by varying the inductor value. Generally, low inductor values produce a broader efficiency vs. load curve, while higher values result in higher full-load efficiency (assuming that the coil resistance remains fixed) and less output voltage ripple. Penalties for using higher inductor values include larger physical size and degraded load-transient response, especially at low input voltage levels.

#### **Current-Limit Circuit**

The current-limit circuit employs a unique "valley" current-sensing algorithm that uses the on-resistance of the low-side MOSFET as a current-sensing element. If the current-sense signal is above the current-limit threshold, the PWM is not allowed to initiate a new cycle

Figure 6. Pulse-Skipping/Discontinuous Crossover Point

(Figure 7). The actual peak current is greater than the current-limit threshold by an amount equal to the inductor ripple current. Therefore, the exact current-limit characteristic and maximum load capability are a function of the MOSFET on-resistance, inductor value, and battery voltage. The reward for this uncertainty is robust, lossless overcurrent sensing. When combined with the undervoltage protection circuit, this current-limit method is effective in almost every circumstance.

There is also a negative current limit that prevents excessive reverse inductor currents when V<sub>OUT</sub> is sinking current. The negative current-limit threshold is set to approximately 120% of the positive current limit, and therefore tracks the positive current limit when ILIM is adjusted.

The current-limit threshold is adjusted with an external resistor-divider at ILIM. The current-limit threshold voltage adjustment range is from 50mV to 300mV. In the adjustable mode, the current-limit threshold voltage is precisely 1/10th the voltage seen at ILIM. The threshold defaults to 100mV when ILIM is connected to VCC. The logic threshold for switchover to the 100mV default value is approximately VCC - 1V.

The adjustable current limit accommodates MOSFETs with a wide range of on-resistance characteristics (see the *Design Procedure* section). For a high-accuracy current-limit application, see Figure 16.

Carefully observe the PC board layout guidelines to ensure that noise and DC errors don't corrupt the current-sense signals seen by LX and GND. Place the IC close to the low-side MOSFET with short, direct traces, making a Kelvin sense connection to the source and drain terminals.

Figure 7. "Valley" Current-Limit Threshold Point

#### **MOSFET Gate Drivers (DH, DL)**

The DH and DL drivers are optimized for driving moderate-sized high-side and larger low-side power MOSFETs. This is consistent with the low duty factor seen in the notebook CPU environment, where a large VBATT - VOUT differential exists. An adaptive dead-time circuit monitors the DL output and prevents the high-side FET from turning on until DL is fully off. There must be a low-resistance, low-inductance path from the DL driver to the MOSFET gate for the adaptive dead-time circuit to work properly. Otherwise, the sense circuitry in the MAX1718 will interpret the MOSFET gate as "off" while there is actually still charge left on the gate. Use very short, wide traces measuring 10 to 20 squares (50 to 100 mils wide if the MOSFET is 1 inch from the MAX1718).

The dead time at the other edge (DH turning off) is determined by a fixed 35ns (typ) internal delay.

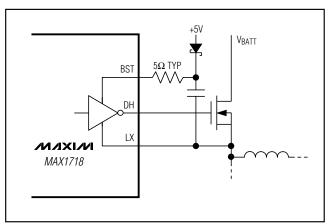

The internal pulldown transistor that drives DL low is robust, with a  $0.4\Omega$  (typ) on-resistance. This helps prevent DL from being pulled up during the fast rise-time of the inductor node, due to capacitive coupling from the drain to the gate of the low-side synchronous-rectifier MOSFET. However, for high-current applications, you might still encounter some combinations of high- and low-side FETs that will cause excessive gate-drain coupling, which can lead to efficiency-killing, EMI-producing shoot-through currents. This is often remedied by adding a resistor in series with BST, which increases the turn-on time of the high-side FET without degrading the turn-off time (Figure 8).

#### **POR**

Power-on reset (POR) occurs when V<sub>CC</sub> rises above approximately 2V, resetting the fault latch and preparing the PWM for operation. V<sub>CC</sub> undervoltage lockout

Figure 8. Reducing the Switching-Node Rise Time

(UVLO) circuitry inhibits switching, forces VGATE low, and forces the DL gate driver high (to enforce output overvoltage protection). When V<sub>CC</sub> rises above 4.2V, the DAC inputs are sampled and the output voltage begins to slew to the DAC setting.

For automatic startup, the battery voltage should be present before V<sub>CC</sub>. If the MAX1718 attempts to bring the output into regulation without the battery voltage present, the fault latch will trip. The SKP/SDN pin can be toggled to reset the fault latch.

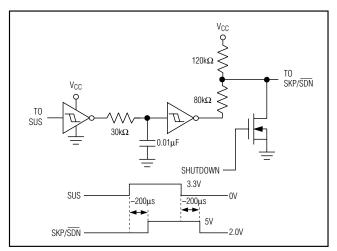

#### Shutdown

When SKP/ $\overline{\text{SDN}}$  goes low, the MAX1718 enters low-power shutdown mode. VGATE goes low immediately. The output voltage ramps down to 0V in 25mV steps at the clock rate set by R<sub>TIME</sub>. When the DAC reaches the 0V setting, DL goes high, DH goes low, the reference is turned off, and the supply current drops to about 2 $\mu$ A.

When SKP/SDN goes high or floats, the reference powers up, and after the reference UVLO is passed, the DAC target is evaluated and switching begins. The slew-rate controller ramps up from 0V in 25mV steps to the currently selected code value (based on ZMODE and SUS). There is no traditional soft-start (variable current limit) circuitry, so full output current is available immediately. VGATE goes high after the slew-rate controller has terminated and the output voltage is in regulation.

#### UVLO

If VCC drops low enough to trip the UVLO comparator, it is assumed that there is not enough supply voltage to make valid decisions. To protect the output from overvoltage faults, DL is forced high in this mode. This will force the output to GND, but it will not use the slew-rate controller. This results in large negative inductor current

and possibly small negative output voltages. If  $V_{\rm CC}$  is likely to drop in this fashion, the output can be clamped with a Schottky diode to GND to reduce the negative excursion.

#### **DAC Inputs D0-D4**

The digital-to-analog converter (DAC) programs the output voltage. It typically receives a preset digital code from the CPU pins, which are either hard-wired to GND or left open-circuit. They can also be driven by digital logic, general-purpose I/O, or an external mux. Do not leave D0-D4 floating-use  $1M\Omega$  or less pullups if the inputs may float. D0-D4 can be changed while the SMPS is active, initiating a transition to a new output voltage level. If this mode of DAC control is used, connect ZMODE and SUS low. Change D0-D4 together, avoiding greater than 1µs skew between bits. Otherwise, incorrect DAC readings may cause a partial transition to the wrong voltage level, followed by the intended transition to the correct voltage level, lengthening the overall transition time. The available DAC codes and resulting output voltages (Table 3) are compatible with IMVP-II specification.

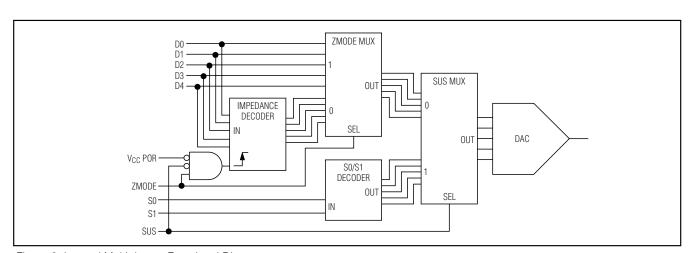

#### **Internal Multiplexers (ZMODE, SUS)**

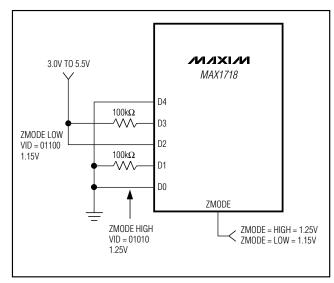

The MAX1718 has two unique internal VID input multiplexers (muxes) that can select one of three different VID DAC code settings for different processor states. Depending on the logic level at SUS, the Suspend (SUS) mode mux selects the VID DAC code settings from either the ZMODE mux or the S0/S1 input decoder. The ZMODE mux selects one of the two VID DAC code settings from the D0–D4 pins, based on either voltage on the pins or the output of the impedance decoder (Figure 9).

When SUS is high, the Suspend mode mux selects the VID DAC code settings from the S0/S1 input decoder. The outputs of the decoder are determined by inputs S0 and S1 (Table 4).

When SUS is low, the Suspend mode mux selects the output of the ZMODE mux. Depending on the logic level at ZMODE, the ZMODE mux selects the VID DAC code settings using either the voltage on D0–D4 or the output of the impedance decoder (Table 5).

If ZMODE is low, the logic-level voltages on D0–D4 set the VID DAC settings. This is called Logic mode. In this mode, the inputs are continuously active and can be dynamically changed by external logic. The Logic mode VID DAC code setting is typically used for the Battery mode state, and the source of this code is sometimes the VID pins of the CPU with suitable pullup resistors.

Table 3. Output Voltage vs. DAC Codes

| D4 | D3 | D2 | D1 | D0 | OUTPUT<br>VOLTAGE (V) | POS/NEG SCALE<br>FACTOR |

|----|----|----|----|----|-----------------------|-------------------------|

| 0  | 0  | 0  | 0  | 0  | 1.75                  | 0.90                    |

| 0  | 0  | 0  | 0  | 1  | 1.70                  | 0.90                    |

| 0  | 0  | 0  | 1  | 0  | 1.65                  | 0.90                    |

| 0  | 0  | 0  | 1  | 1  | 1.60                  | 0.89                    |

| 0  | 0  | 1  | 0  | 0  | 1.55                  | 0.89                    |

| 0  | 0  | 1  | 0  | 1  | 1.50                  | 0.89                    |

| 0  | 0  | 1  | 1  | 0  | 1.45                  | 0.88                    |

| 0  | 0  | 1  | 1  | 1  | 1.40                  | 0.88                    |

| 0  | 1  | 0  | 0  | 0  | 1.35                  | 0.88                    |

| 0  | 1  | 0  | 0  | 1  | 1.30                  | 0.87                    |

| 0  | 1  | 0  | 1  | 0  | 1.25                  | 0.87                    |

| 0  | 1  | 0  | 1  | 1  | 1.20                  | 0.86                    |

| 0  | 1  | 1  | 0  | 0  | 1.15                  | 0.86                    |

| 0  | 1  | 1  | 0  | 1  | 1.10                  | 0.85                    |

| 0  | 1  | 1  | 1  | 0  | 1.05                  | 0.85                    |

| 0  | 1  | 1  | 1  | 1  | 1.00                  | 0.84                    |

| 1  | 0  | 0  | 0  | 0  | 0.975                 | 0.84                    |

| 1  | 0  | 0  | 0  | 1  | 0.950                 | 0.83                    |

| 1  | 0  | 0  | 1  | 0  | 0.925                 | 0.83                    |

| 1  | 0  | 0  | 1  | 1  | 0.900                 | 0.82                    |

| 1  | 0  | 1  | 0  | 0  | 0.875                 | 0.82                    |

| 1  | 0  | 1  | 0  | 1  | 0.850                 | 0.82                    |

| 1  | 0  | 1  | 1  | 0  | 0.825                 | 0.81                    |

| 1  | 0  | 1  | 1  | 1  | 0.800                 | 0.81                    |

| 1  | 1  | 0  | 0  | 0  | 0.775                 | 0.80                    |

| 1  | 1  | 0  | 0  | 1  | 0.750                 | 0.80                    |

| 1  | 1  | 0  | 1  | 0  | 0.725                 | 0.79                    |

| 1  | 1  | 0  | 1  | 1  | 0.700                 | 0.78                    |

| 1  | 1  | 1  | 0  | 0  | 0.675                 | 0.78                    |

| 1  | 1  | 1  | 0  | 1  | 0.650                 | 0.77                    |

| 1  | 1  | 1  | 1  | 0  | 0.625                 | 0.76                    |

| 1  | 1  | 1  | 1  | 1  | 0.600                 | 0.76                    |

18 \_\_\_\_\_\_ NIXI/N

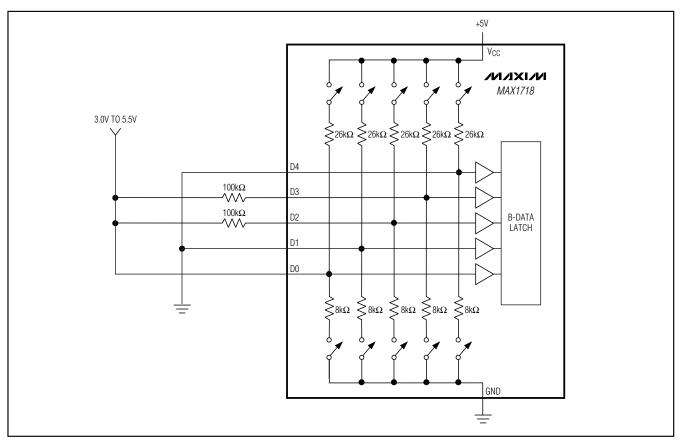

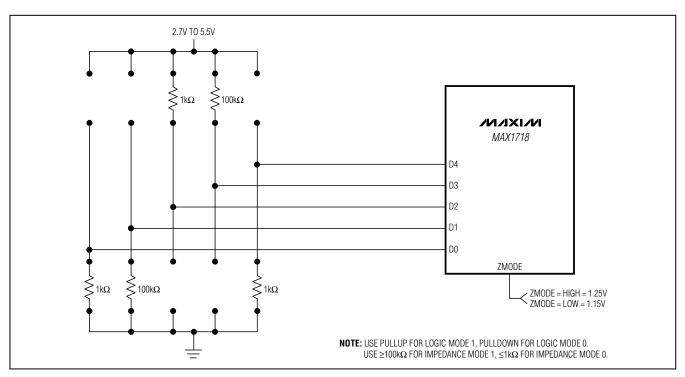

On the rising edge of ZMODE, during power-up with ZMODE high or on the falling edge of SUS when ZMODE is high, the impedances at D0-D4 are sampled by the impedance decoder to see if a large resistance is in series with the pin. This is called Impedance mode. If the voltage level on the pin is a logic low, an internal switch connects the pin to an internal  $26k\Omega$ pullup for about 4µs to see if the pin voltage can be forced high (Figure 10). If the pin voltage can be pulled to a logic high, the impedance is considered high and so is the Impedance mode logic state. Similarly, if the voltage level on the pin is a logic high, an internal switch connects the pin to an internal  $8k\Omega$  pulldown to see if the pin voltage can be forced low. If so, the pin is high impedance and its Impedance mode logic state is high. In either sampling condition, if the pin's logic level does not change, the pin is determined to be low impedance and the Impedance mode logic state is low.

A high pin impedance (and logic high) is  $100 k\Omega$  or greater, and a low impedance (and logic low) is  $1k\Omega$  or less. The *Electrical Characteristics* table guaranteed levels for these impedances are  $95k\Omega$  and  $1.05k\Omega$  to allow the use of standard  $100k\Omega$  and  $1k\Omega$  resistors with 5% tolerance.

#### Using the ZMODE Mux

There are many ways to use the versatile ZMODE mux. The preferred method will depend on when and how the VID DAC codes for the various states are determined. If the output voltage codes are fixed at PC board design time, program both codes with a simple combination of pin-strap connections and series resistors (Figure 11). If the output voltage codes are chosen during PC board assembly, both codes can be independently programmed with resistors (Figure 12). This

**Table 4. Suspend Mode DAC Codes**

| S1      | S0   | OUTPUT VOLTAGE (V) |

|---------|------|--------------------|

| GND     | GND  | 0.975              |

| GND     | REF  | 0.950              |

| GND     | OPEN | 0.925              |

| GND     | Vcc  | 0.900              |

| REF     | GND  | 0.875              |

| REF     | REF  | 0.850              |

| REF     | OPEN | 0.825              |

| REF     | Vcc  | 0.800              |

| OPEN    | GND  | 0.775              |

| OPEN    | REF  | 0.750              |

| OPEN    | OPEN | 0.725              |

| OPEN    | Vcc  | 0.700              |

| Vcc     | GND  | 0.675              |

| Vcc     | REF  | 0.650              |

| Vcc     | OPEN | 0.625              |

| Vcc Vcc |      | 0.600              |

matrix of 10 resistor-footprints can be programmed to all possible Logic mode and Impedance mode code combinations with only 5 resistors.

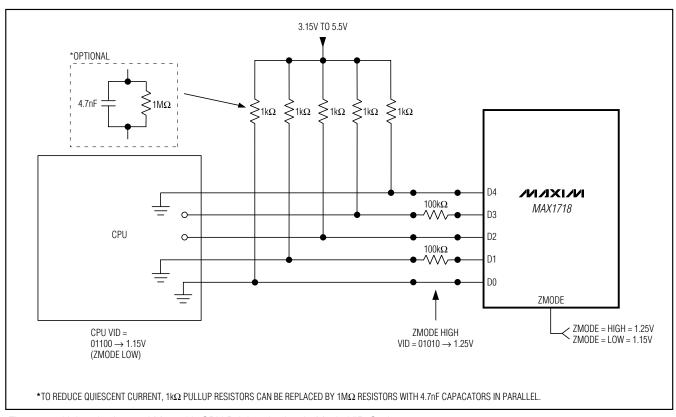

Often the CPU pins provide one set of codes that are typically used with pullup resistors to provide the Logic mode VID code, and resistors in series with D0–D4 set the Impedance mode code. Since some of the CPU's VID pins may float, the open-circuit pins can present a problem for the ZMODE mux's Impedance mode. For the Impedance mode to work, any pins intended to be

Figure 9. Internal Multiplexers Functional Diagram

Figure 10. Internal Mux Impedance-Mode Data Test and Latch

low during Impedance mode must appear to be low impedance, at least for the 4µs sampling interval.

This can be achieved in several ways, including the following two (Figure 13). By using low-impedance pullup resistors with the CPU's VID pins, each pin provides the low impedance needed for the mux to correctly interpret the Impedance mode setting. Unfortunately, the low resistances cause several mA quiescent currents for each of the CPU's grounded VID pins. This quiescent current can be avoided by taking advantage of the fact that D0-D4 need only appear low impedance briefly, not necessarily on a continuous DC basis. Highimpedance pullups can be used if they are bypassed with a large enough capacitance to make them appear low impedance for the 4us sampling interval. As noted in Figure 13, 4.7nF capacitors allow the inputs to appear low impedance even though they are pulled up with large-value resistors. Each sampling depletes some charge from the 4.7nF capacitors. A minimum

Figure 11. Using the Internal Mux with Hard-Wired Logic-Mode and Impedance-Mode DAC Codes

Figure 12. Using the Internal Mux with Both VID Codes Resistor Programmed

interval of 2  $\times$  R<sub>PULLUP</sub>  $\times$  4.7nF is recommended between ZMODE samples.

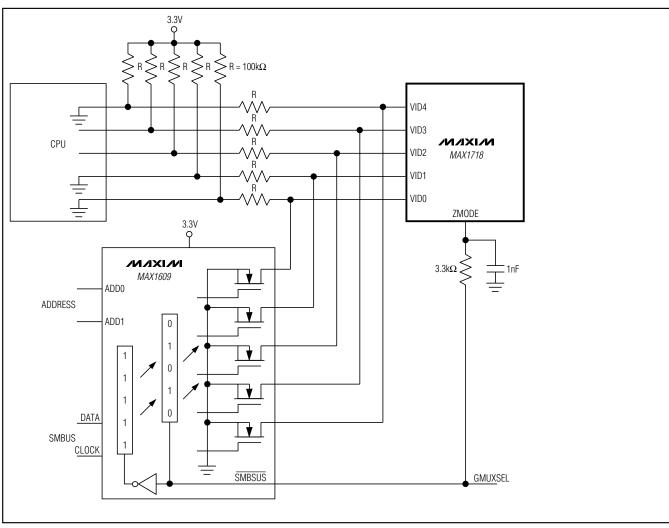

In some cases, it is desirable to determine the Impedance mode code during system boot so that several processor types can be used without hardware modifications. Figure 14 shows one way to implement this function. The desired code is determined by the system BIOS and programmed into one register of the MAX1609 using the SMBus™ serial interface. The MAX1609's other register is left in its power-up state (all outputs high impedance). When SMBSUS is low, the outputs are high impedance and do not affect the Logic-mode VID code setting. When SMBSUS is high, the programmed register is selected, and the MAX1609 forces a low impedance on the appropriate VID input pins. The ZMODE signal is delayed relative to the SMB-SUS pin because the VID pins that are pulled low by the MAX1609 take significant time to rise when they are released. One additional benefit of using the MAX1609 for this application is that the application uses only five of the MAX1609's high-voltage, open-drain outputs. The other three outputs can be used for other purposes.

**Table 5. DAC Mux Operation**

| ZMODE | sus | OUTPUT VOLTAGE<br>DETERMINED BY: |

|-------|-----|----------------------------------|

| GND   | GND | Logic Level of D0-D4             |

| Vcc   | GND | Impedance of D0-D4               |

| X     | Vcc | Logic Levels of S0, S1           |

#### **Output Voltage Transition Timing**

The MAX1718 is designed to perform output voltage transitions in a controlled manner, automatically minimizing input surge currents. This feature allows the circuit designer to achieve nearly ideal transitions, guaranteeing just-in-time arrival at the new output voltage level with the lowest possible peak currents for a given output capacitance. This makes the IC ideal for IMVP-II CPUs.

IMVP-II CPUs operate at two distinct clock frequencies and require three distinct VID settings. When transitioning from one clock frequency to the other, the CPU first goes into a low-power state, then the output voltage and clock frequency are changed. The change must be accomplished in 100µs or the system may halt.

SMBus™ is a trademark of Intel Corp.

Figure 13. Using the Internal Mux with CPU Driving the Logic-Mode VID Code

At the beginning of an output voltage transition, the MAX1718 blanks the VGATE output, preventing it from going low. VGATE remains blanked during the transition and is re-enabled when the slew-rate controller has set the internal DAC to the final value and one additional slew-rate clock period has passed. The slew-rate clock frequency (set by resistor RTIME) must be set fast enough to ensure that the longest required transition is completed within the allowed 100µs.

The output voltage transition is performed in 25mV steps, preceded by a delay and followed by one additional clock period. The total time for a transition depends on RTIME, the voltage difference, and the accuracy of the MAX1718's slew-rate clock, and is not dependent on the total output capacitance. The greater the output capacitance, the higher the surge current required for the transition. The MAX1718 will automatically control the current to the minimum level required to complete the transition in the calculated time, as long as the surge current is less than the current limit set by ILIM. The transition time is given by:

$$\leq \left\lceil \frac{1}{f_{SLEW}} \times \frac{V_{OLD} - V_{NEW}}{25mV} \right\rceil + T_{DELAY}$$

where  $f_{SLEW}=150 kHz \times 120 k\Omega$  / RTIME, VOLD is the original DAC setting, V<sub>NEW</sub> is the new DAC setting, and T<sub>DELAY</sub> ranges from zero to a maximum of 2/f<sub>SLEW</sub>. See Time Frequency Accuracy in the *Electrical Characteristics* table for f<sub>SLEW</sub> accuracy.

The practical range of R<sub>TIME</sub> is  $47k\Omega$  to  $470k\Omega$ , corresponding to 2.6µs to 26µs per 25mV step. Although the DAC takes discrete 25mV steps, the output filter makes the transitions relatively smooth. The average inductor current required to make an output voltage transition is:

$$I_L \cong C_{OUT} \times 25 \text{mV} \times f_{SLEW}$$

#### **Output Overvoltage Protection**

The overvoltage protection (OVP) circuit is designed to protect the CPU against a shorted high-side MOSFET by drawing high current and blowing the battery fuse. The output voltage is continuously monitored for over-

Figure 14. Using the ZMODE Multiplexer

voltage. If the output is more than 2V, OVP is triggered and the circuit shuts down. The DL low-side gate-driver output is then latched high until SKP/SDN is toggled or V<sub>CC</sub> power is cycled below 1V. This action turns on the synchronous-rectifier MOSFET with 100% duty and, in turn, rapidly discharges the output filter capacitor and forces the output to ground. If the condition that caused the overvoltage (such as a shorted high-side MOSFET) persists, the battery fuse will blow. DL is also kept high continuously when V<sub>CC</sub> UVLO is active, as well as in shutdown mode (Table 6).

Overvoltage protection can be defeated with a logic high on  $\overline{\text{OVP}}$  or through the NO FAULT test mode (see the NO FAULT Test Mode section).