#### **ABSOLUTE MAXIMUM RATINGS**

| ONA, ONB, AO, OUT to GND      | 0.3V, +6V                          | С  |

|-------------------------------|------------------------------------|----|

| PGND to GND                   |                                    |    |

| LX to PGND                    | 0.3V to (V <sub>POUT</sub> + 0.3V) |    |

| CLK/SEL, REF, FB, ISET, POUT, |                                    | 0  |

| AIN to GND                    | 0.3V to (V <sub>OUT</sub> + 0.3V)  | Ju |

| POUT to OUT                   | ±0.3V                              | St |

|                               |                                    |    |

| Continuous Power Dissipation         |                |

|--------------------------------------|----------------|

| 16-Pin QSOP (derate 8.7mW/°C above + | -70°C)667mW    |

| 16-Pin TSSOP-EP (derate 19mW/°C abov | e +70°C)1.5W   |

| Operating Temperature Range          | 40°C to +85°C  |

| Junction Temperature                 | +150°C         |

| Storage Temperature Range            | 65°C to +150°C |

| Lead Temperature (soldering, 10s)    | +300°C         |

| Soldering Temperature (reflow)       |                |

|                                      |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(CLK/SEL =  $\overline{\text{ONB}}$  = FB = PGND = GND, ISET = REF, OUT = POUT,  $V_{\text{ONA}} = V_{\text{AIN}} = V_{\text{OUT}} = 3.6 \text{V}$ ,  $T_{\text{A}} = 0^{\circ}\text{C}$  to +85°C, unless otherwise noted. Typical values are at  $T_{\text{A}} = +25^{\circ}\text{C}$ .)

| PARAMETER                                           | CONDITIONS                                                                         | MIN   | TYP   | MAX   | UNITS |

|-----------------------------------------------------|------------------------------------------------------------------------------------|-------|-------|-------|-------|

| DC-DC CONVERTER                                     |                                                                                    |       |       |       |       |

| Input Voltage Range (Note 1)                        |                                                                                    |       | 0.7   | 5.5   | V     |

| Minimum Startup Voltage (Note 2)                    | $I_{LOAD}$ < 1mA, $T_A$ = +25°C                                                    |       | 0.9   | 1.1   | V     |

| Temperature Coefficient of<br>Startup Voltage       | I <sub>LOAD</sub> < 1mA                                                            |       | -2    |       | mV/°C |

| Frequency in Startup Mode                           | $V_{OUT} = 1.5V$                                                                   | 125   | 500   | 1000  | kHz   |

| Internal Oscillator Frequency                       | CLK/SEL = OUT                                                                      | 0.8   | 1     | 1.2   | MHz   |

| Oscillator Maximum Duty Cycle (Note 3)              |                                                                                    | 80    | 86    | 90    | %     |

| External Clock Frequency Range                      |                                                                                    | 0.5   |       | 1.2   | MHz   |

| Output Voltage                                      | $V_{FB}$ < 0.1V, CLK/SEL = OUT, includes load regulation for 0 < $I_{LX}$ < 1.1A   | 3.17  | 3.3   | 3.38  | V     |

| FB Regulation Voltage                               | Adjustable output, CLK/SEL = OUT, includes load regulation for $0 < I_{LX} < 1.1A$ | 1.215 | 1.245 | 1.270 | V     |

| FB Input Current                                    | V <sub>FB</sub> = 1.35V                                                            |       | 0.01  | 100   | nA    |

| Load Regulation                                     | $CLK/SEL = OUT, 0 < I_{LX} < 1.1A$                                                 |       | -1.0  |       | %     |

| Output Voltage Adjust Range                         |                                                                                    | 2.5   |       | 5.5   | V     |

| Output Voltage Lockout<br>Threshold (Note 4)        | Rising edge                                                                        | 2.00  | 2.15  | 2.30  | V     |

| ISET Input Leakage Current                          | V <sub>ISET</sub> = 1.25V                                                          |       | 0.01  | 50    | nA    |

| Supply Current in Shutdown                          | $V_{\overline{ONB}} = 3.6V, V_{\overline{ONA}} = 0V$                               |       | 1     | 10    | μΑ    |

| No-Load Supply Current, Low-<br>Power Mode (Note 5) | CLK/SEL = GND, AIN = OUT                                                           |       | 110   | 200   | μΑ    |

| No-Load Supply Current, Low-<br>Noise Mode          | CLK/SEL = OUT                                                                      |       | 2.5   |       | mA    |

| Gain Block Supply Current                           | V <sub>AIN</sub> < (V <sub>OUT</sub> - 1.4V), gain block enabled                   |       | 25    | 50    | μΑ    |

### **ELECTRICAL CHARACTERISTICS (continued)**

(CLK/SEL =  $\overline{\text{ONB}}$  = FB = PGND = GND, ISET = REF, OUT = POUT,  $V_{\text{ONA}}$  =  $V_{\text{AIN}}$  =  $V_{\text{OUT}}$  = 3.6V,  $T_{\text{A}}$  = 0°C to +85°C, unless otherwise noted. Typical values are at  $T_{\text{A}}$  = +25°C.)

| PARAMETER                                                                       | CONDITIONS                                                                          | MIN                       | TYP   | MAX                       | UNITS    |

|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------|-------|---------------------------|----------|

| DC-DC SWITCHES                                                                  |                                                                                     |                           |       |                           |          |

| POUT Leakage Current                                                            | $V_{LX} = 0V$ , $V_{OUT} = 5.5V$                                                    |                           | 0.1   | 10                        | μΑ       |

| LX Leakage Current                                                              | V <sub>LX</sub> = V <sub>ONB</sub> = V <sub>OUT</sub> = 5.5V, V <sub>ONA</sub> = 0V |                           | 0.1   | 10                        | μΑ       |

| Outtole On Desistance                                                           | N channel                                                                           |                           | 0.075 | 0.13                      |          |

| Switch On-Resistance                                                            | P channel                                                                           |                           | 0.13  | 0.25                      | Ω        |

| N-Channel Current Limit                                                         |                                                                                     | 2.0                       | 2.5   | 3.4                       | Α        |

| P-Channel Turn-Off Current                                                      | CLK/SEL = GND                                                                       | 10                        | 120   | 240                       | mA       |

| REFERENCE                                                                       |                                                                                     |                           |       |                           |          |

| Reference Output Voltage                                                        | I <sub>REF</sub> = 0A                                                               | 1.230                     | 1.250 | 1.270                     | V        |

| Reference Load Regulation                                                       | -1μA < I <sub>REF</sub> < 50μA                                                      |                           | 5     | 15                        | mV       |

| Reference Supply Rejection                                                      | 2.5V < V <sub>OUT</sub> < 5V                                                        |                           | 0.2   | 5                         | mV       |

| GAIN BLOCK                                                                      |                                                                                     |                           |       |                           |          |

| AIN Reference Voltage                                                           | Ι <sub>ΑΟ</sub> = 20μΑ                                                              | 910                       | 938   | 970                       | mV       |

| AIN Input Current                                                               | V <sub>AIN</sub> = 1.5V                                                             |                           | ±0.01 | ±30                       | nA       |

| Transconductance                                                                | $V_{AO} = 1V$ , $10\mu A < I_{AO} < 100\mu A$                                       | 5                         | 10    | 16                        | mS       |

| AO Output Low Voltage                                                           | V <sub>AIN</sub> = 0.5V, I <sub>AO</sub> = 100μA                                    |                           | 0.1   | 0.4                       | V        |

| AO Output High Leakage                                                          | V <sub>AIN</sub> = 1.5V, V <sub>AO</sub> = 5.5V                                     |                           | 0.01  | 1                         | μΑ       |

| Gain-Block Enable Threshold<br>(V <sub>OUT</sub> - V <sub>AIN</sub> ) (Note 6)  |                                                                                     |                           |       | 1.4                       | V        |

| Gain-Block Disable Threshold<br>(V <sub>OUT</sub> - V <sub>AIN</sub> ) (Note 6) |                                                                                     | 0.2                       |       |                           | V        |

| LOGIC INPUTS                                                                    |                                                                                     | l                         |       |                           | <u> </u> |

| CLK/SEL Input Low Level                                                         | 2.5V ≤ V <sub>OUT</sub> ≤ 5.5V                                                      |                           |       | (0.2)<br>V <sub>OUT</sub> | V        |

| CLK/SEL Input High Level                                                        | 2.5 V ≤ V <sub>OUT</sub> ≤ 5.5V                                                     | (0.8)<br>V <sub>OUT</sub> |       |                           | V        |

| ONA and ONB Input Low Level                                                     | $1.1 \text{ V} \leq \text{V}_{\text{OUT}} \leq 1.8 \text{V}$                        |                           |       | 0.2                       | V        |

| (Note 7)                                                                        | 1.8 V ≤ V <sub>OUT</sub> ≤ 5.5V                                                     |                           |       | 0.4                       | V        |

| ONA and ONB Input High Level                                                    | 1.1 V ≤ V <sub>OUT</sub> ≤ 1.8V                                                     | V <sub>OUT</sub> - 0.2V   |       |                           | V        |

| (Note 7)                                                                        | 1.8 V ≤ V <sub>OUT</sub> ≤ 5.5V                                                     | 1.6                       |       |                           |          |

| Input Leakage Current                                                           | CLK/SEL, ONA, ONB                                                                   | İ                         | 0.01  | 1                         | μΑ       |

| Minimum CLK/SEL Pulse Width                                                     |                                                                                     |                           | 100   |                           | ns       |

| Maximum CLK/SEL<br>Rise/Fall Time                                               |                                                                                     |                           | 100   |                           | ns       |

### **ELECTRICAL CHARACTERISTICS**

(CLK/SEL =  $\overline{\text{ONB}}$  = FB = PGND = GND, ISET = REF, OUT = POUT,  $V_{ONA} = V_{AIN} = V_{OUT} = 3.6V$ ,  $T_A = -40^{\circ}\text{C}$  to +85°C, unless otherwise noted.) (Note 8)

| PARAMETER                                           | CONDITIONS                                                                         | MIN   | MAX   | UNITS |

|-----------------------------------------------------|------------------------------------------------------------------------------------|-------|-------|-------|

| DC-DC CONVERTER                                     |                                                                                    |       |       |       |

| Input Voltage Range (Note 1)                        |                                                                                    |       | 5.5   | V     |

| Minimum Startup Voltage (Note 2)                    | $I_{LOAD}$ < 1mA, $T_A$ = +25°C                                                    |       | 1.1   | V     |

| Frequency in Startup Mode                           | V <sub>OUT</sub> = 1.5V                                                            | 125   | 1000  | kHz   |

| Internal Oscillator Frequency                       | CLK/SEL = OUT                                                                      | 0.75  | 1.25  | MHz   |

| Oscillator Maximum Duty Cycle (Note 3)              |                                                                                    | 80    | 91    | %     |

| External Clock Frequency Range                      |                                                                                    | 0.6   | 1.2   | MHz   |

| Output Voltage                                      | $V_{FB} < 0.1V$ , CLK/SEL = OUT, includes load regulation for $0 < I_{LX} < 1.1A$  | 3.17  | 3.38  | V     |

| FB Regulation Voltage                               | Adjustable output, CLK/SEL = OUT, includes load regulation for $0 < I_{LX} < 1.1A$ | 1.215 | 1.270 | V     |

| FB Input Current                                    | V <sub>FB</sub> = 1.35V                                                            |       | 100   | nA    |

| Output Voltage Adjust Range                         |                                                                                    | 2.5   | 5.5   | V     |

| Output Voltage Lockout<br>Threshold (Note 4)        | Rising edge                                                                        | 2.00  | 2.30  | V     |

| ISET Input Leakage Current                          | V <sub>ISET</sub> = 1.25V                                                          |       | 50    | nA    |

| Supply Current in Shutdown                          | $V\overline{ONB} = 3.6V, VONA = 0V$                                                |       | 10    | μΑ    |

| No-Load Supply Current, Low-<br>Power Mode (Note 5) | CLK/SEL = GND, AIN = OUT                                                           |       | 200   | μΑ    |

| Gain Block Supply Current                           | V <sub>AIN</sub> < (V <sub>OUT</sub> - 1.4V), gain block enabled                   |       | 50    | μΑ    |

| DC-DC SWITCHES                                      | ·                                                                                  | •     |       |       |

| POUT Leakage Current                                | $V_{LX} = 0V, V_{OUT} = 5.5V$                                                      |       | 10    | μA    |

| LX Leakage Current                                  | $V_{LX} = V_{\overline{ONB}} = V_{OUT} = 5.5V, V_{ONA} = 0V$                       |       | 10    | μA    |

| Outtale On Desistance                               | N-channel                                                                          |       | 0.13  |       |

| Switch On-Resistance                                | P-channel                                                                          |       | 0.25  | Ω     |

| N-Channel Current Limit                             |                                                                                    | 2.0   | 3.4   | А     |

| P-Channel Turn-Off Current                          | CLK/SEL = GND                                                                      | 10    | 240   | mA    |

| REFERENCE                                           |                                                                                    |       |       |       |

| Reference Output Voltage                            | I <sub>REF</sub> = 0A                                                              | 1.220 | 1.270 | V     |

| Reference Load Regulation                           | -1μA < I <sub>REF</sub> < 50μA                                                     |       | 15    | mV    |

| Reference Supply Rejection                          | 2.5V < V <sub>OUT</sub> < 5V                                                       |       | 5     | mV    |

| GAIN BLOCK                                          |                                                                                    |       |       |       |

| AIN Reference Voltage                               | Ι <sub>ΑΟ</sub> = 20μΑ                                                             | 910   | 970   | mV    |

| AIN Input Current                                   | V <sub>AIN</sub> = 1.5V                                                            |       | ±30   | nA    |

| Transconductance                                    | V <sub>AO</sub> = 1V, 10μA < I <sub>AO</sub> < 100μA                               | 5     | 16    | mS    |

| AO Output Low Voltage                               | V <sub>AIN</sub> = 0.5V, I <sub>AO</sub> = 100μA                                   |       | 0.4   | V     |

| AO Output High Leakage                              | V <sub>AIN</sub> = 1.5V, V <sub>AO</sub> = 5.5V                                    |       | 1     | μΑ    |

\_\_\_ /VI/XI/VI

### **ELECTRICAL CHARACTERISTICS (continued)**

(CLK/SEL =  $\overline{\text{ONB}}$  = FB = PGND = GND, ISET = REF, OUT = POUT,  $V_{ONA} = V_{AIN} = V_{OUT} = 3.6V$ ,  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 8)

| PARAMETER                                                                       | CONDITIONS                      | MIN                       | MAX                       | UNITS |

|---------------------------------------------------------------------------------|---------------------------------|---------------------------|---------------------------|-------|

| LOGIC INPUTS                                                                    |                                 | ·                         |                           |       |

| Gain-Block Enable Threshold<br>(V <sub>OUT</sub> - V <sub>AIN</sub> ) (Note 6)  |                                 |                           | 1.4                       | V     |

| Gain-Block Disable Threshold<br>(V <sub>OUT</sub> - V <sub>AIN</sub> ) (Note 6) |                                 | 0.2                       |                           | V     |

| CLK/SEL Input Low Level                                                         | 2.5 V ≤ V <sub>OUT</sub> ≤ 5.5V |                           | (0.2)<br>V <sub>OUT</sub> | V     |

| CLK/SEL Input High Level                                                        | 2.5 V ≤ V <sub>OUT</sub> ≤ 5.5V | (0.8)<br>V <sub>OUT</sub> |                           | V     |

| ONA and ONB Input Low Level                                                     | 1.1 V ≤ V <sub>OUT</sub> ≤ 1.8V |                           | 0.2                       | V     |

| (Note 7)                                                                        | 1.8 V ≤ V <sub>OUT</sub> ≤ 5.5V |                           | 0.4                       | V     |

| ONA and ONB Input High Level (Note 7)                                           | 1.1 V ≤ V <sub>OUT</sub> ≤ 1.8V | Vout<br>- 0.2V            |                           | V     |

| (NOTE 1)                                                                        | 1.8V ≤ V <sub>OUT</sub> ≤ 5.5V  | 1.6                       |                           |       |

| Input Leakage Current                                                           | CLK/SEL, ONA, ONB               |                           | 1                         | μΑ    |

- Note 1: Operating voltage. Because the regulator is bootstrapped to the output, once started, the MAX1763 will operate down to 0.7V input. For conditions where V<sub>IN</sub> might exceed the set V<sub>OUT</sub>, or where V<sub>OUT</sub> is set above 4V, an external Schottky diode must be connected from LX to POUT.

- Note 2: Startup is tested with the circuit of Figure 2.

- Note 3: Defines low-noise mode maximum step-up ratio.

- Note 4: The regulator is in startup mode until this voltage is reached. Do not apply full load current until the output exceeds 2.3V.

- **Note 5:** Supply current from the 3.3V output is measured between the 3.3V output and the OUT pin. This current correlates directly to the actual battery-supply current, but is reduced in value according to the step-up ratio and efficiency. The gain block is disabled.

- Note 6: Connect AIN to OUT to disable gain block.

- **Note 7:** ONA and  $\overline{ONB}$  have hysteresis of approximately 0.15  $\times$  VOLIT.

- **Note 8:** Specifications to -40°C are guaranteed by design and not production tested.

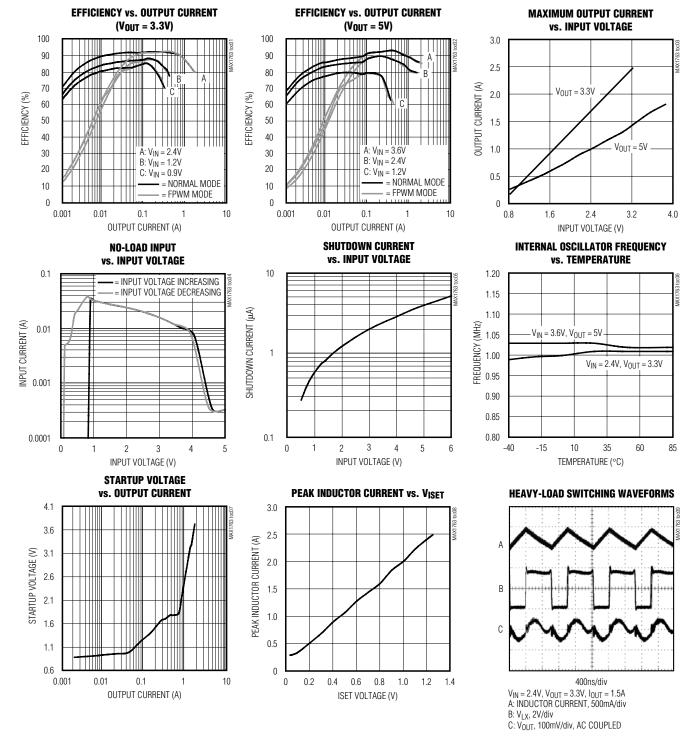

### Typical Operating Characteristics

(Circuit of Figure 2,  $V_{IN} = +3.6V$ ,  $V_{OUT} = +5V$ ,  $T_A = +25$ °C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

(Circuit of Figure 2,  $V_{IN}$  = +3.6V,  $V_{OUT}$  = +5V,  $T_A$  = +25°C, unless otherwise noted.)

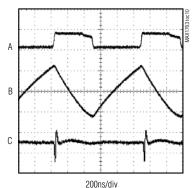

#### LIGHT-LOAD SWITCHING WAVEFORMS

$V_{IN}$  = 1.1V,  $V_{OUT}$  = 3.3V,  $I_{OUT}$  = 20mA A: LX NODE, 5V/div B: INDUCTOR CURRENT, 0.1A/div, AC COUPLED

C: OUTPUT RIPPLE, 0.1V/div, AC COUPLED

### LOAD-TRANSIENT RESPONSE

V<sub>IN</sub> = 2.4V, V<sub>OUT</sub> = 3.3V, I<sub>OUT</sub> = 0.2A TO 1.35A A: I<sub>OUT</sub>, 0.5A/div B: V<sub>OUT</sub>, 100mV/div, AC-COUPLED

LINE-TRANSIENT RESPONSE

V<sub>IN</sub> = 2.4V TO 1.4V, I<sub>OUT</sub> = 70mA A: V<sub>IN</sub>, 1V/div

B: V<sub>OUT</sub>, 5mV/div, AC-COUPLED

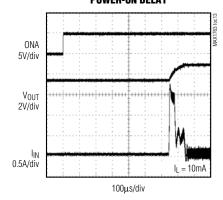

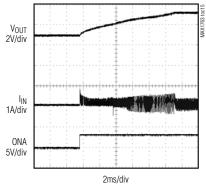

#### **POWER-ON DELAY**

#### STARTUP WAVEFORMS NO SOFT-START

## STARTUP WAVEFORMS USING SOFT-START

$V_{IN} = 1.2V$ ,  $V_{OUT} = 3.3V$ ,  $R_{SS} = 510k\Omega$ ,  $C_{SS} = 0.1\mu F$ ,  $R_{LOAD} = 3k\Omega$

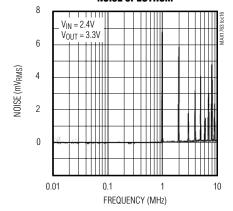

#### NOISE SPECTRUM

### **Pin Description**

| PIN    | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | ONA     | On Control Input. When ONA = high or $\overline{\text{ONB}}$ = low, the IC turns on. Connect ONA to OUT for normal operation (Table 3).                                                                                                                                                                                                                                                                                                        |

| 2      | ISET    | N-Channel Current Limit Control. For maximum current limit, connect to REF. To reduce current, supply a voltage between REF and GND by means of a resistive voltage-divider. If soft-start is desired, connect a capacitor from ISET to GND. When ONA = low and $\overline{\text{ONB}}$ = high, or V <sub>REF</sub> < 80% of nominal value, an on-chip switched resistor (100k $\Omega$ typ) discharges this pin to GND.                       |

| 3      | REF     | 1.250V Voltage Reference Bypass Pin. Connect a 0.22µF ceramic bypass capacitor to GND. Up to 50µA of external REF load current is allowed.                                                                                                                                                                                                                                                                                                     |

| 4      | GND     | Ground. Connect to PGND with short trace.                                                                                                                                                                                                                                                                                                                                                                                                      |

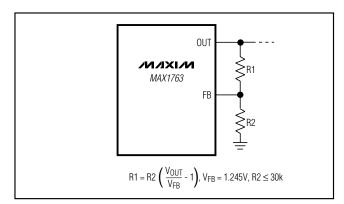

| 5      | FB      | DC-DC Converter Feedback Input. To set fixed output voltage of +3.3V, connect FB to ground. For adjustable output of 2.5V to 5.5V, connect to a resistive divider placed from OUT to GND. FB set point is 1.245V (Figure 6).                                                                                                                                                                                                                   |

| 6      | OUT     | IC Power, Supplied from the Output. Bypass to GND with a 1.0 $\mu$ F ceramic capacitor, and connect to POUT with a series 4.7 $\Omega$ resistor (Figure 2).                                                                                                                                                                                                                                                                                    |

| 7      | AIN     | Gain-Block Input. The nominal transconductance from AIN to AO is 10mS. An external P-channel pass device can be used to build a linear regulator. The gain block can also be used as a low-battery comparator with a threshold of 0.938V. The gain block and its associated quiescent current are disabled by connecting AIN to OUT.                                                                                                           |

| 8      | AO      | Gain-Block Output. This open-drain N-channel output sinks current when $V_{AIN} < (0.75)(V_{REF})$ . AO is high-Z when the device is shut down, or when AIN = OUT.                                                                                                                                                                                                                                                                             |

| 9      | CLK/SEL | Clock Input for the DC-DC Converter. Also serves to program the operating mode of the switcher as follows:  CLK/SEL = LO: Normal; operates at a fixed frequency, automatically switching to low-power mode if load is minimized.  CLK/SEL = HI: Forced PWM mode; operates in low-noise, constant-frequency mode at all loads.  CLK/SEL = Clocked: Forced PWM mode with the internal oscillator synchronized to CLK in 500kHz to 1200kHz range. |

| 10, 12 | PGND    | Source of N-Channel Power MOSFET Switch. Connect both PGND pins together close to the device.                                                                                                                                                                                                                                                                                                                                                  |

| 11, 14 | LX      | Inductor Connection. Connect the LX pins together close to the device.                                                                                                                                                                                                                                                                                                                                                                         |

| 13, 15 | POUT    | Power Output. P-channel synchronous rectifier source.                                                                                                                                                                                                                                                                                                                                                                                          |

| 16     | ONB     | Off Control Input. When $\overline{\text{ONB}}$ = high and ONA = low, the IC is off. Connect $\overline{\text{ONB}}$ to GND for normal operation (Table 3).                                                                                                                                                                                                                                                                                    |

| _      | EP      | Exposed Pad (TSSOP Only). Connect EP to a large ground plane to maximize thermal performance.                                                                                                                                                                                                                                                                                                                                                  |

### **Detailed Description**

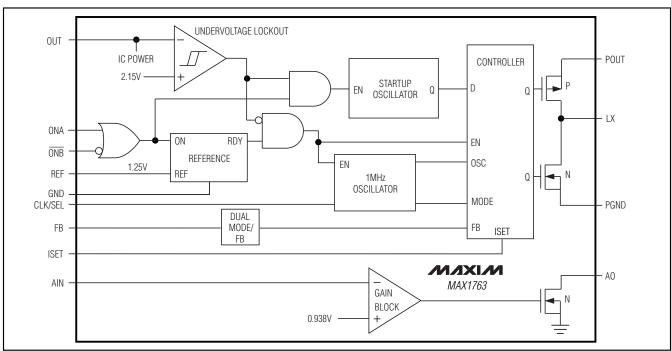

The MAX1763 is a highly-efficient, low-noise power supply for portable RF and hand-held instruments. It combines a boost switching regulator, N-channel power MOSFET, P-channel synchronous rectifier, precision reference, shutdown control, and a versatile gain block (Figure 1).

The DC-DC converter boosts a one-cell to three-cell battery voltage input to a fixed 3.3V or adjustable voltage between 2.5V and 5.5V. An external Schottky diode is

required for output voltages greater than 4V. The MAX1763 guarantees startup with an input voltage as low as 1.1V and remains operational down to an input of just 0.7V. It is optimized for use in cellular phones and other applications requiring low noise and low quiescent current for maximum battery life. It features constant-frequency (1MHz), low-noise PWM operation with up to 1.5A output capability. A CLK input allows frequency synchronization to control the output noise spectrum. See Table 1 for typical available output current.

\_\_ /N/XI/N

Figure 1. Functional Diagram

**Table 1. Typical Available Output Current**

| -                  |                         |                          |                           |

|--------------------|-------------------------|--------------------------|---------------------------|

| NUMBER<br>OF CELLS | INPUT<br>VOLTAGE<br>(V) | OUTPUT<br>VOLTAGE<br>(V) | OUTPUT<br>CURRENT<br>(mA) |

| 1 NiCd/NiMH        | 1.2                     | 3.3                      | 675                       |

| O NI:O 4/NI:MILI   | 2.4                     | 3.3                      | 1500                      |

| 2 NiCd/NiMH        | 2.4                     | 5.0                      | 950                       |

| 1 Li+              | 2.7 (min)               | 3.3                      | 1300                      |

| 1 Li+              | 2.7 (min)               | 5.0                      | 1100                      |

| 3 NiCd/NiMH        | 3.6                     | 5.0                      | 1600                      |

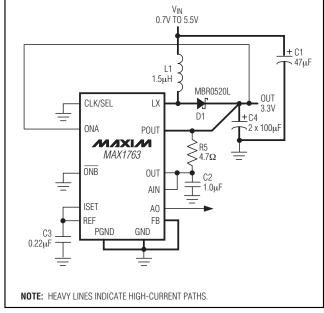

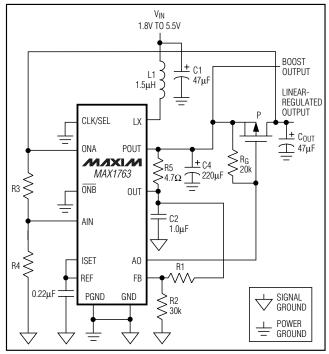

In its normal mode of operation (CLK/SEL = low), the MAX1763 offers fixed-frequency PWM operation through most of its load range. At light loads (less than 25% of full load), the device automatically optimizes efficiency by switching only as needed to supply the load. Shutdown reduces quiescent current to just 1 $\mu$ A. Figure 2 shows the standard application circuit for the MAX1763. (An external Schottky diode is needed for output voltages greater than 4V, or to assist low-voltage startup.)

Additional features include synchronous rectification for high efficiency and increased battery life, and a gain block that can be used to build a linear regulator using an external P-channel MOSFET pass device. This gain

Figure 2. PFM/PWM Automode Connection

block can also function as a voltage-monitoring comparator. The MAX1763 is available in a 16-pin QSOP package or a 1.5W 16-pin TSSOP-EP package for high-temperature or high-dissipation applications.

**Table 2. Selecting the Operating Mode**

| CLK/SEL                            | MODE                | FEATURES                                                              |

|------------------------------------|---------------------|-----------------------------------------------------------------------|

| 0                                  | Normal operation    | High efficiency at all loads. Fixed frequency at all but light loads. |

| 1                                  | Forced PWM          | Low noise, fixed frequency at all loads.                              |

| External clock<br>500kHz to 1.2MHz | Synchronized<br>PWM | Low noise, fixed frequency at all loads.                              |

### Step-Up Converter

During DC-DC converter operation, the internal N-channel MOSFET switch turns on for the first part of each cycle, allowing current to ramp up in the inductor and store energy in a magnetic field. During the second part of each cycle, the MOSFET turns off and inductor current flows through the synchronous rectifier to the output filter capacitor and the load. As the energy stored in the inductor is depleted, the current ramps down and the synchronous rectifier turns off, the N-channel FET turns on, and the cycle repeats. At light loads, depending on the CLK/SEL pin setting, output voltage is regulated using either PWM or by switching only as needed to service the load (Table 2).

#### **Normal Operation**

Pulling CLK/SEL low selects the MAX1763's normal operating mode. In this mode, the device operates in PWM when driving medium to heavy loads, and at light loads only, switches as needed. This optimizes efficiency over the widest range of load conditions. In normal operation mode, the output voltage regulates 1% higher than in forced-PWM mode. See Efficiency vs. Load Current in the *Typical Operating Characteristics* section.

#### **Forced-PWM Operation**

When CLK/SEL is high, the MAX1763 operates in a low-noise forced-PWM mode. During forced-PWM operation, the MAX1763 switches at a constant frequency (1MHz) and modulates the MOSFET switch pulse width to control the power transferred per cycle and regulate the output voltage. Switching harmonics generated by fixed-frequency operation are consistent and easily filtered. See the Noise Spectrum plot in the *Typical Operating Characteristics*.

#### **Synchronized-PWM Operation**

In a variation of forced-PWM mode, the MAX1763 can be synchronized to an external frequency by applying a clock signal to CLK/SEL. This allows the user to choose an operating frequency (from 500kHz to 1.2MHz) to avoid interference in sensitive applications. For the most noise-sensitive applications, limit the external synchronization signal duty cycle to less than 10% or greater than 90%. This eliminates the possibility that noise from the power switching will coincide with the synchronization signal. If the synchronization signal edge falls on the power switching edge, a slight frequency jitter may occur.

#### **Synchronous Rectifier**

The MAX1763 features an internal  $130m\Omega$  P-channel synchronous rectifier to enhance efficiency. Synchronous rectification provides a 5% efficiency improvement over similar boost regulators that rely on diode rectifiers. In PWM mode, the synchronous rectifier is turned on during the second half of each switching cycle. In low-power mode, an internal comparator turns on the synchronous rectifier when the voltage at LX exceeds the boost regulator output and turns it off when the inductor current drops below 120mA. When setting output voltages greater than 4V, an external 0.5A Schottky diode must be connected in parallel with the on-chip synchronous rectifier.

#### Low-Voltage Startup Oscillator

The MAX1763 uses a CMOS low-voltage startup oscillator for a 1.1V guaranteed minimum startup input voltage. At startup, the low-voltage oscillator switches the N-channel MOSFET until the output voltage reaches 2.15V. Above this level, the normal feedback and control circuitry take over. Once the device is in regulation, it can operate down to 0.7V input because internal power for the IC is derived from the output through the OUT pin. Do not apply full system load until the output exceeds 2.3V.

#### Shutdown, ONA, ONB

ONA and  $\overline{\text{ONB}}$  turn the MAX1763 on or off. When ONA = 1 or  $\overline{\text{ONB}}$  = 0, the device is on. When ONA = 0 and  $\overline{\text{ONB}}$  = 1, the device is off (Table 3). Logic high ON control can be implemented by connecting  $\overline{\text{ONB}}$  high and using ONA for the control input. Momentary one-pushbutton ON/OFF control is described in the Applications Information section. Both ONA and  $\overline{\text{ONB}}$  have approximately (0.15 × VOUT)V of hysteresis.

#### Reference

The MAX1763 has an internal 1.250V reference. Connect a 0.22 $\mu$ F ceramic bypass capacitor to GND within 0.2in (5mm) of the REF pin. REF can source up to 50 $\mu$ A of external load current.

#### **Gain Block**

The MAX1763 gain block can function as a power-OK comparator or can be used to build a linear regulator

Table 3. On/Off Logic Control

| ONA | ONB | MAX1763 |

|-----|-----|---------|

| 0   | 0   | On      |

| 0   | 1   | Off     |

| 1   | 0   | On      |

| 1   | 1   | On      |

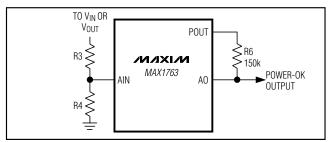

Figure 3. Using the Gain Block as a Power-OK Comparator

Figure 4. Using the Gain Block as a Linear Regulator from the Boosted Output Voltage

using an external P-channel MOSFET pass device. The gain-block output is a single-stage transconductance amplifier that drives an open-drain N-channel MOSFET. The transconductance (G<sub>M</sub>) of the entire gain-block

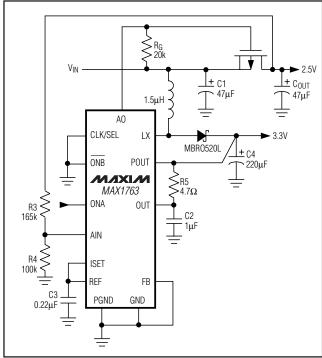

Figure 5. Powering a Gain-Block Linear Regulator from the Input Voltage

stage is 10mS. The internal gain block amplifies the difference between AIN and the internal 0.938V reference.

To provide a power-OK signal, connect the gain-block input, AIN, to an external resistor-divider (Figure 3). The input bias current into AIN is less than 30nA, allowing large-value divider resistors without sacrificing accuracy. Connect the resistor voltage-divider as close to the IC as possible, within 0.2in (5mm) of AIN. Choose an R4 value of  $270k\Omega$  or less, then calculate R3 using:

$$R3 = R4((VTRIP / VAIN) - 1)$$

where VAIN is 0.938V.

Figures 4 and 5 show the gain block used in a linear-regulator application. The output of an external P-channel pass element is compared to an internal 0.938V reference. The difference is amplified and drives the gate of the pass element. Use a logic-level PFET, such as Fairchild's NDS336P (RDS(ON) = 270m $\Omega$ ). When the linear-regulator output voltage is in regulation, the MOSFET will not be full on; thus, the on-resistance will not be important. However, if the linear regulator is used in dropout, the MOSFET on-resistance will determine the dropout voltage (VDROPOUT = IOUT × RDS(ON)). If a lower RDS(ON) PFET is used, increase the linear-regulator output filter capacitance to maintain stability.

The output capacitance can be determined by the function:

$C_{OUT} \ge [ (V_{REF} / V_{OUT}) \times G_{M} \times G_{FS} \times C_{G} \times (R_{G} \times 2) ]$  and

Cout ≥ 10 × [ (V<sub>REF</sub> / [V<sub>OUT</sub> × GBP]) × G<sub>M</sub> × G<sub>FS</sub> × R<sub>G</sub> ] where V<sub>REF</sub> is the 0.983V reference voltage, G<sub>M</sub> is the 10mS internal amplifier transconductance, G<sub>FS</sub> is the external MOSFET transconductance, R<sub>G</sub> is the gate-source resistor, and GBP is the gain-bandwidth product of the internal gain block, 63Mrad/s.

### **Design Procedure**

#### **Setting the Output Voltage**

For a fixed 3.3V output, connect FB to GND. To set the output voltage between 2.5V and 5.5V, connect a resistor voltage-divider to FB from OUT to GND (Figure 6). The input bias current into FB is less than 100nA, allowing large-value divider resistors without sacrificing accuracy. Connect the resistor voltage-divider as close to the IC as possible, within 0.2in (5mm) of FB. Choose R2 of  $30k\Omega$  or less, then calculate R1 using:

$$R1 = R2((V_{OUT} / V_{FB}) - 1)$$

where  $V_{FB}$ , the boost-regulator feedback set point, is 1.245V.

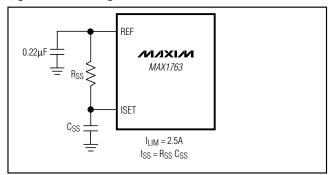

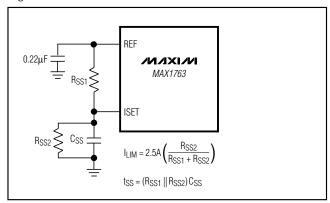

## Setting the Switch Current Limit and Soft-Start

The ISET pin adjusts the inductor peak current and can also be used to implement soft-start. With ISET connected to REF, the inductor current limits at 2.5A. With ISET connected to a resistive divider set from REF to GND, the current limit is reduced according to:

$$I_{LIM} = 2.5(V_{ISET} / 1.25) [A]$$

Implement soft-start by placing a resistor from ISET to REF (>300k $\Omega$ ) and a capacitor from ISET to GND. In shutdown, ISET is discharged to GND through an internal  $100k\Omega$  resistor. As the capacitor voltage rises, the output current is allowed to increase, and the output voltage rises. The speed at which the output rises is determined by the soft-start time constant:

where Rss ≥ 300k.

Both features may be implemented simultaneously by placing a capacitor across the lower resistor of the current-limiting resistive divider (Figures 7 and 8).

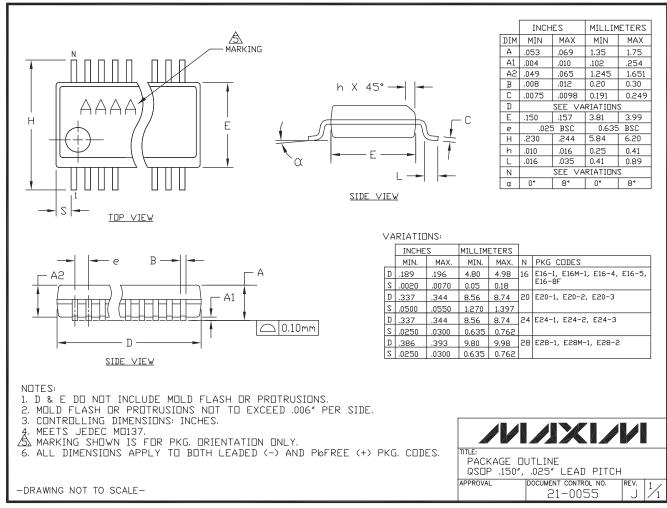

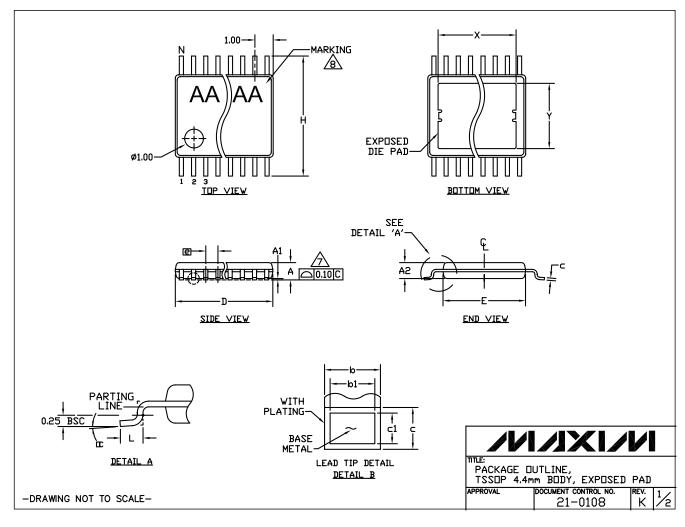

#### **Package Selection**

The MAX1763 is available in two packages, a 16-pin QSOP and a 16-pin TSSOP-EP. Since the MAX1763

Figure 6. Connecting Resistors for External Feedback

Figure 7. Soft-Start with Maximum Switch Limit Current

Figure 8. Soft-Start with Reduced Switch Limit Current

has excellent efficiency, most applications are well served by the QSOP package. If the application requires high power dissipation, or operation in a high ambient temperature, choose the TSSOP-EP package. The TSSOP-EP is equipped with an exposed metal pad on its underside for soldering to grounded circuit board copper. This reduces the junction-to-case thermal resistance of the package from +115°C/W for QSOP to +53°C/W for the TSSOP-EP.

**Table 4. Component Selection Guide**

| INDUCTORS         | CAPACITORS          | DIODES               |

|-------------------|---------------------|----------------------|

|                   | AVX TPS series      |                      |

| Coilcraft LPT3305 | Kemet T510 series   | Motorola<br>MBR0520L |

|                   | Sanyo POSCAP series | WIBITOSZOL           |

| Sumida            | Panasonic SP/CB     | Nihon<br>EP10QY03    |

At an ambient temperature of +70°C, continuous power dissipation for the QSSOP package is 667mW, while the TSSOP-EP can dissipate 1.5W. A first-order estimate of power dissipation can be determined by calculating the output power delivered to the load (e.g., 3.3V  $\times$  1A = 3.3W). At the input voltage used, find the efficiency from the Typical Operating Characteristics graphs (e.g., 87%). The estimated power dissipation in the MAX1763 is then: (100% - %Efficiency) × Output Power. The example would have:  $13\% \times 3.3W = 0.43W$ , allowing the QSOP package (667mW) to be used. For higher ambient temperature, higher output power, or a lower-efficiency operating point, the TSSOP-EP package (1.5W) may be necessary. For detailed package mechanical information, see the package outline drawings at the end of this data sheet.

#### **Inductor Selection**

The MAX1763's high switching frequency allows the use of a small 1.5µH surface-mount inductor. The chosen inductor should generally have a saturation current rating exceeding the N-channel switch current limit; however, it is acceptable to bias the inductor current into saturation by as much as 20% if a slight reduction in efficiency is acceptable. Inductors rated for lower peak current may be used if ISET is employed to reduce the peak inductor current (see Setting the Switch Current Limit and Soft-Start). For high efficiency, choose an inductor with a high-frequency ferrite core material to reduce core losses. To minimize radiated noise, use a toroid or shielded inductor. See Table 4 for suggested components and Table 5 for a list of component suppliers. Connect the inductor from the battery to the LX pins as close to the IC as possible.

#### **External Diode**

For conditions where V<sub>IN</sub> might exceed the set V<sub>OUT</sub>, or where V<sub>OUT</sub> is set above 4V, an external Schottky diode must be connected from LX to POUT in parallel with the on-chip synchronous rectifier. See D1 in Figure 2. The diode should be rated for 0.5A. Representative devices are Motorola MBR0520L, Nihon EP05Q03L, or generic 1N5817. This external diode is also recommended for applications that must start with input voltages at or

**Table 5. Component Suppliers**

| SUPPLIER  | PHONE                                          |

|-----------|------------------------------------------------|

| AVX       | USA: 843-448-9411                              |

| Coilcraft | USA: 847-639-6400                              |

| Kemet     | USA: 810-287-2536                              |

| Motorola  | USA: 408-629-4789<br>Japan: 81-45-474-7030     |

| Sumida    | USA: 847-956-0666<br>Japan: 011-81-3-3667-3302 |

**Note:** Please indicate that you are using the MAX1763 when contacting these component suppliers.

below 1.8V. The Schottky diode carries current during both startup and after the synchronous rectifier turns off. Thus, its current rating only needs to be 500mA even if the inductor current is higher. Connect the diode as close to the IC as possible. Do not use ordinary rectifier diodes; their slow switching speeds and long reverse-recovery times render them unacceptable. For circuits that do not require startup with inputs below 1.8V, and have an output of 4V or less, no external diode is needed.

#### **Input and Output Capacitors**

Choose input and output capacitors that will service the input and output peak currents with acceptable voltage ripple. Choose input capacitors with working voltage ratings over the maximum input voltage, and output capacitors with working voltage ratings higher than the output. A 220µF, low equivalent-series-resistance (ESR) (less than  $100m\Omega$ ) capacitor is recommended for most applications. Alternatively, two  $100\mu$ F capacitors in parallel will reduce the effective ESR for even better performance.

The input capacitor reduces peak currents drawn from the input source and also reduces input switching noise. The input voltage source impedance determines the required size of the input capacitor. When operating directly from one or two NiMH cells placed close to the MAX1763, use a single 47µF low-ESR input filter capacitor. With higher impedance batteries, such as alkaline and Li+, a higher value input capacitor may improve efficiency.

Sanyo POSCAP, Panasonic SP/CB, and Kemet T510 are good low-ESR capacitors (Tables 4 and 5). Low-ESR tantalum capacitors offer a good trade-off between price and performance. Do not exceed the ripple current ratings of tantalum capacitors. Avoid aluminum electrolytic capacitors; their high ESR typically results in higher output ripple voltage.

#### **Bypass Components**

A few ceramic bypass capacitors are required for proper operation. Bypass REF to GND with 0.22 $\mu$ F. Also, bypass OUT to GND with a 1 $\mu$ F ceramic capacitor, and connect OUT to POUT with a 4.7 $\Omega$  resistor. Each of these components should be placed as close to their respective IC pins as possible, within 0.2in (5mm). Table 5 lists suggested suppliers.

#### **Layout Considerations**

High switching frequencies and large peak currents make PC board layout a critical part of design. Poor design will cause excessive EMI and ground bounce, both of which can cause instability or regulation errors by corrupting the voltage and current feedback signals.

Power components, such as the inductor, converter IC, and filter capacitors, should be placed as close together as possible, and their traces should be kept short, direct, and wide. Keep the voltage feedback network very close to the IC, within 0.2in (5mm) of the FB pins. Keep noisy traces, such as those from the LX pin, away from the voltage feedback networks and guarded from them using grounded copper. If an external rectifier is used, its traces must be kept especially short and use an absolute minimum of copper area to avoid excess capacitance that can slow the operation of the on-chip synchronous rectifier and actually reduce efficiency. Refer to the MAX1763 EV kit for a full PC board example.

The MAX1763 TSSOP-EP package features an exposed thermal pad on its underside. This pad lowers the package's thermal resistance by providing a direct thermal heat path from the die to the PC board. Additionally, the ground pin (GND) also channels heat. Connect the exposed thermal pad and GND to circuit ground by using a large pad or multiple vias to the ground plane.

#### **Step-Up/Step-Down Applications**

In some battery-powered applications, the battery voltage range overlaps the output voltage. In this case, depending on the battery voltage, the regulator will have to step the voltage up or down. To make a step-up/step-down regulator, use the gain block to make a linear regulator that follows the step-up converter. In this case, if the battery voltage is low, then the circuit will step up, and when the battery voltage is high, the linear regulator will drop the voltage. See the *Gain Block* section on how to use the gain block to make a linear regulator. When the output voltage is greater than the regulation voltage, then the synchronous rectifier will be held on, reducing the dropout, and thus increasing the efficiency when the battery voltage is close to, but slightly above, the regulation voltage.

### **Chip Information**

SUBSTRATE CONNECTED TO GND

\_\_ /VI/IXI/VI

### Package Information

For the latest package outline information and land patterns (footprints), go to <a href="www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | OUTLINE NO.    | LAND PATTERN NO. |

|--------------|--------------|----------------|------------------|

| 16 QSOP      | E16+1        | <u>21-0055</u> | <u>90-0167</u>   |

| 16 TSSOP-EP  | U16E+3       | <u>21-0108</u> | <u>90-0120</u>   |

Note: The MAX1763EEE is a 16-pin QSOP and does not have a heat slug. Use the MAX1763EUE for higher power dissipation.

### Package Information (continued)

For the latest package outline information and land patterns (footprints), go to <a href="www.maxim-ic.com/package">www.maxim-ic.com/package</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

### Package Information (continued)

For the latest package outline information and land patterns (footprints), go to www.maxim-ic.com/packages. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| S.               | COMMON DIMENSIONS |          |                |        |  |

|------------------|-------------------|----------|----------------|--------|--|

| S<br>Y<br>B<br>D | MILLIM            | ETERS    | INCHES         |        |  |

| <u> </u>         | MIN.              | MAX.     | MIN.           | MAX.   |  |

| Α                |                   | 1.10     |                | 0.043  |  |

| A1               | 0.05              | 0.15     | 0.002          | 0.006  |  |

| A2               | 0.85              | 0.95     | 0.033          | 0.037  |  |

| b                | 0.19              | 0.30     | 0.007          | 0.012  |  |

| b1               | 0.19              | 0.25     | 0.007          | 0.010  |  |

| С                | 0.090             | 0.20     | 0.004          | 0.008  |  |

| c1               | 0.090             | 0.135    | 0.004          | 0.0053 |  |

| D                | SEE VAF           | RIATIONS | SEE VARIATIONS |        |  |

| E                | 4.30              | 4.50     | 0.169          | 0.177  |  |

| e                | 0.65              | BSC      | 0.026 BSC      |        |  |

| Н                | 6.25              | 6.50     | 0.246          | 0.256  |  |

| L                | 0.50              | 0.70     | 0.020          | 0.028  |  |

| N                | SEE VAR           | RIATIONS | SEE VARIATIONS |        |  |

| Υ                | 2.60              | 3.10     | 0.102          | 0.122  |  |

| OC               | 0*                | 8•       | 0*             | 8•     |  |

| JEDEC  |    |          |   | VARIATI□NS |       |       |       |

|--------|----|----------|---|------------|-------|-------|-------|

| MD-153 | N  | Pkg.Code |   | MILLIM     | ETERS | INC   | HES   |

| MD-123 |    |          |   | MIN.       | MAX.  | MIN.  | MAX.  |

| ABT-1  | 14 | U14E-3   | D | 4.90       | 5.10  | 0.193 | 0.201 |

|        |    |          | Х | 2.80       | 3.10  | 0.110 | 0.122 |

| ABT    | 16 | U16E-3   | D | 4.90       | 5.10  | 0.193 | 0.201 |

|        |    |          | Х | 2.60       | 3.10  | 0.102 | 0.122 |

| ACT    | 20 | U20E-1   | D | 6.40       | 6.60  | 0.252 | 0.260 |

|        |    |          | Х | 3.80       | 4.20  | 0.150 | 0.165 |

| ACT    | 20 | U20E-4   | D | 6.40       | 6.60  | 0.252 | 0.260 |

|        |    |          | Х | 4.50       | 4.90  | 0.177 | 0.193 |

| AET    | 28 | U28E-4   | D | 9.60       | 9.80  | 0.378 | 0.386 |

|        |    |          | Х | 5.20       | 5.60  | 0.205 | 0.221 |

| AET    | 28 | U28E-5   | D | 9.60       | 9.80  | 0.378 | 0.386 |

|        |    |          | Х | 6.50       | 6.90  | 0.256 | 0.272 |

| AET    | 28 | U28ME-1  | D | 9.60       | 9.80  | 0.378 | 0.386 |

|        |    |          | Х | 6.50       | 6.90  | 0.256 | 0.272 |

| JEDEC N |    | Pkg.Code |   | VARIATIONS  |      |        |       |  |

|---------|----|----------|---|-------------|------|--------|-------|--|

|         | N  |          |   | MILLIMETERS |      | INCHES |       |  |

| MU-123  |    |          |   | MIN.        | MAX. | MIN.   | MAX.  |  |

| ADT     | 24 | U24E-1   | D | 7.70        | 7.90 | 0.303  | 0.311 |  |

|         |    |          | X | 4.44        | 4.64 | 0.175  | 0.183 |  |

|         |    |          | Υ | 2.64        | 2.84 | 0.104  | 0.112 |  |

#### NUTES:

- 1. DIMENSIONS D AND E DO NOT INCLUDE FLASH.

- 1. DIMENSIONS D AND E DO NOT INCLUDE FLASH.

2. MOLD FLASH OR PROTRUSIONS NOT TO EXCEED 0.15mm PER SIDE.

3. CONTROLLING DIMENSION; MILLIMETERS.

4. MEETS JEDEC OUTLINE MO-153. SEE JEDEC VARIATIONS TABLE.

5. 'N' REFERS TO NUMBER OF LEADS.

6. EXPOSED PAD FLUSH WITH BOTTOM OF PACKAGE WITHIN .002'.

- 6. EXPUSED PAD FLUSH WITH BUTTOM OF PACKAGE WITHIN JUE?

THE LEAD TIPS MUST LIE WITHIN A SPECIFIED ZONE. THIS TOLERANCE ZONE IS DEFINED BY TWO PARALLEL PLANES. DNE PLANE IS THE SEATING PLANE, DATUM (-C-); THE OTHER PLANE IS AT THE SPECIFIED DISTANCE FROM (-C-) IN THE DIRECTION INDICATED.

MARKING SHOWN IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

9. NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY.

10. ALL DIMENSIONS ADDITIONS ADDITIONAL PARENCE (-) AND DEFREE (+) PKG. CODES

- 10. ALL DIMENSIONS APPLY TO BOTH LEADED (-) AND PhFREE (+) PKG. CODES.

-DRAWING NOT TO SCALE-

### **Revision History**

| REVISION | REVISION | DESCRIPTION                                                                                                                            | PAGES       |

|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------|-------------|

| NUMBER   | DATE     |                                                                                                                                        | CHANGED     |

| 2        | 4/11     | Added lead-free designation, added conditions for use when V <sub>IN</sub> > V <sub>OUT</sub> , updated <i>Pin Description</i> section | 1, 5, 8, 13 |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

### Maxim Integrated:

MAX1763EEE+T MAX1763EEE+ MAX1763EUE+ MAX1763EUE+T MAX1763EUE-T MAX1763EEE

MAX1763EEE-T MAX1763EUE