#### FUNCTIONAL DESCRIPTION

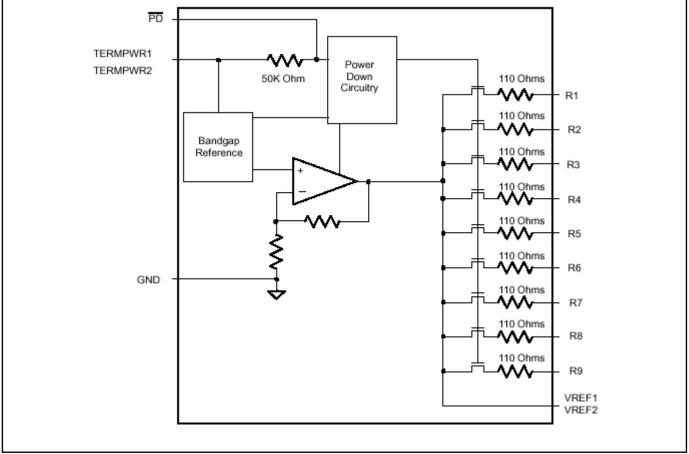

The DS21S07A consists of a bandgap reference, buffer amplifier, and nine termination resistors (Figure 1). The bandgap reference circuit produces a precise 2.55V level that is fed to a buffer amplifier. The buffer produces a 2.85V level and can source at least 24mA into each of the termination resistors when the signal line is low (active). When the driver for a given signal line turns off, the terminator pulls the signal line to 2.85V (quiescent state). To handle actively negated SCSI signals, the buffer can sink at least 200mA, and VREF will move less than 60mV. When all lines settle in the quiescent state, the regulator consumes about 2.5mA. When the DS21S07A is put into power-down mode by bringing  $\overline{PD}$  low, the power-down circuitry turns off the transistors on each signal line. This isolates the DS21S07A from the signal lines and effectively removes it from the circuit. The power-down pin  $(\overline{PD})$  has an internal  $50k\Omega$  pullup resistor. To place the DS21S07A into an active state, the  $\overline{PD}$  pin should be left open circuited. When installed on disk drives or RAID system components, the DS21S07A will not affect the SCSI bus during a hot plug operation.

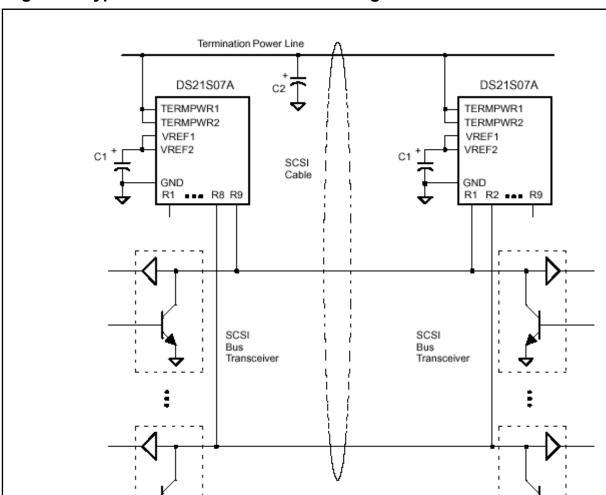

To ensure proper operation, both the TERMPWR1 and TERMPWR2 pins must be connected to the SCSI bus TERMPWR line and both the VREF1 and VREF2 pins must be tied together externally. Each DS21S07A requires a 4.7μF capacitor connected between the VREF pins and ground. Figure 2 details a typical SCSI bus configuration. In an 8-bit-wide SCSI bus arrangement ("A" Cable), two DS21S07A's would be needed at each end of the SCSI cable to terminate the 18 active signal lines. In a 16-bit-wide SCSI bus arrangement ("P" Cable), three DS21S07A's would be needed at each end of the SCSI cable to terminate the 27 active signal lines.

Figure 1. DS21S087A Block Diagram

SCSI

Bus

Transceiver

Figure 2. Typical Differential SCSI Bus Configuration

**NOTE 1:** C1 =  $4.7\mu$ F TANTALUM CAPACITOR; C2 =  $2.2\mu$ F TANTALUM OR  $4.7\mu$ F ALUMINUM CAPACITOR. **NOTE 2:** IF THE DS21S07A IS TO BE EMBEDDED INTO A PERIPHERAL THAT WILL ACT AS A TARGET ON A SCSI BUS, IT IS RECOMMENDED THAT TERMPWR BE DERIVED FROM THE SCSI CABLE, NOT GENERATED LOCALLY. IN THIS CONFIGURATION, IF A POWER FAILURE OCCURS IN THE PERIPHERAL, IT WILL NOT AFFECT THE BUS.

SCSI

Transceiver

Bus

NOTE 3: A HIGH-FREQUENCY BYPASS CAPACITOR (0.1 $\mu$ F RECOMMENDED) CAN BE ADDED IN PARALLEL TO C1 FOR APPLICATIONS USING FAST RISE/FALL TIME DRIVERS.

**Table 1. Pin Description**

| PIN             |               | NIADATE  | THINOTION                                                                                                                                                                                                          |  |  |  |  |

|-----------------|---------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| TSSOP           | SO            | NAME     | FUNCTION                                                                                                                                                                                                           |  |  |  |  |

| 1               | 1             | TERMPWR1 | <b>Termination Power 1.</b> Should be connected to the SCSI TERMPWR line. Must be decoupled with either a 2.2μF capacitor or 4.7μF capacitor. See Figure 2.                                                        |  |  |  |  |

| 2, 8, 12,<br>18 | _             | HS-GND   | <b>Heat Sink Ground.</b> Internally connected to the mounting pad. Should be either grounded or electrically isolated from other circuitry.                                                                        |  |  |  |  |

| 3–7,<br>13–16   | 2–6,<br>10–13 | R1–R9    | Signal Termination 1–9. 110Ω termination.                                                                                                                                                                          |  |  |  |  |

| 9               | 7             | VREF1    | <b>Reference Voltage 1.</b> Must be externally connected directly to the VREF2 pin. Must be decoupled with a 4.7μF capacitor as shown in Figure 2.                                                                 |  |  |  |  |

| 10              | 8             | GND      | Ground. 0V, signal ground.                                                                                                                                                                                         |  |  |  |  |

| 11              | 9             | TERMPWR2 | <b>Termination Power 2.</b> Should be connected to the SCSI TERMPWR line. Must be decoupled with either a 2.2μF capacitor or 4.7μF capacitor. See Figure 2.                                                        |  |  |  |  |

| 17              | 14            | NC       | <b>No Connection.</b> Do not connect any signal to this pin.                                                                                                                                                       |  |  |  |  |

| 19              | 15            | VREF2    | <b>Reference Voltage 2.</b> Must be externally connected directly to the VREF1 pin. Must be decoupled with a 4.7μF capacitor as shown in Figure 2.                                                                 |  |  |  |  |

| 20              | 16            | PD       | <b>Active-Low Power-Down.</b> When tied low, the DS21S07A enters a power-down mode. Contains an internal 50kΩ pullup resistor. Strap low to deactivate the DS21S07A; leave open circuited to activate the DS21S07A |  |  |  |  |

# **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range on Any Pin Relative to Ground | 1.0V to +7.0V                         |

|---------------------------------------------|---------------------------------------|

| Operating Temperature Range                 | 0°C to +70°C                          |

| Storage Temperature Range                   | 55°C to +125°C                        |

| Soldering Temperature                       | See IPC/JEDEC J-STD-020 Specification |

This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.

# RECOMMENDED OPERATING CONDITIONS

$(T_A = 0^{\circ}C \text{ to } +70^{\circ}C)$

| PARAMETER       | SYM          | MIN  | TYP | MAX            | UNITS | NOTES |

|-----------------|--------------|------|-----|----------------|-------|-------|

| TERMPWR Voltage | $ m V_{TP}$  | 4.00 |     | 5.50           | V     |       |

| PD Active       | $V_{PDA}$    | -0.3 |     | +0.8           | V     |       |

| PD Inactive     | $ m V_{PDI}$ | 2.0  |     | $V_{TP} + 0.3$ | V     |       |

# DC CHARACTERISTICS

$(T_A = 0^{\circ}C \text{ to } +70^{\circ}C)$

| PARAMETER              | SYMBOL      | MIN  | TYP                                       | MAX | UNITS | NOTES      |

|------------------------|-------------|------|-------------------------------------------|-----|-------|------------|

| TERMPWR Current        | Ţ           |      |                                           | 250 | mA    | 1, 3       |

| TERMI WR Cullent       | $I_{TP}$    |      | 250 2.5 5 100 150 108 110 112 150 3.0 5.0 | 5   | mA    | 1, 4       |

| Power-Down Current     | $I_{PD}$    |      | 100                                       | 150 | μA    | 1, 2, 5    |

| Termination Resistance | $R_{TERM}$  | 108  | 110                                       | 112 | Ω     | 1, 2       |

| Die Thermal Shutdown   | $T_{SD}$    | 150  |                                           |     | °C    | 1, 6       |

| Power-Down Termination | $C_{PD}$    |      | 2.0                                       | 5.0 | nΕ    | 1 2 5 6    |

| Capacitance            | CPD         |      | 3.0                                       | 3.0 | pF    | 1, 2, 5, 6 |

| Input Leakage High     | $ m I_{IH}$ | -1.0 |                                           |     | μA    | 1, 8       |

| Input Leakage Low      | $ m I_{IL}$ |      |                                           | 1.0 | μΑ    | 1, 7       |

# **REGULATOR CHARACTERISTICS**

$(T_A = 0^{\circ}C \text{ to } +70^{\circ}C)$

| PARAMETER        | SYMBOL        | MIN  | TYP  | MAX  | UNITS | NOTES |

|------------------|---------------|------|------|------|-------|-------|

| Output Voltage   | $ m V_{REF}$  | 2.79 | 2.85 | 2.93 | V     | 1, 2  |

| Drop-Out Voltage | $ m V_{DROP}$ |      | 0.50 | 0.75 | V     | 3, 6  |

| Line Regulation  | $LI_{REG}$    |      | 1.0  | 2.0  | %     | 1, 4  |

| Load Regulation  | $LO_{REG}$    |      | 1.3  | 3.0  | %     | 1, 3  |

| Current Limit    | $I_{LIM}$     |      | 350  |      | mA    | 1     |

| Sink Current     | $I_{SINK}$    | 200  |      |      | mA    | 1     |

# **NOTES:**

- 1) 4.00V < TERMPWR < 5.50V.

- 2) 0.0V < signal lines < TERMPWR.

- 3) All signal lines = 0V.

- 4) All signal lines open.

- 5)  $\overline{PD} = 0V$ .

- 6) Guaranteed by design; not production tested.

- 7) R1 to R9 only.

- 8) R1 to R9 and  $\overline{PD}$ .

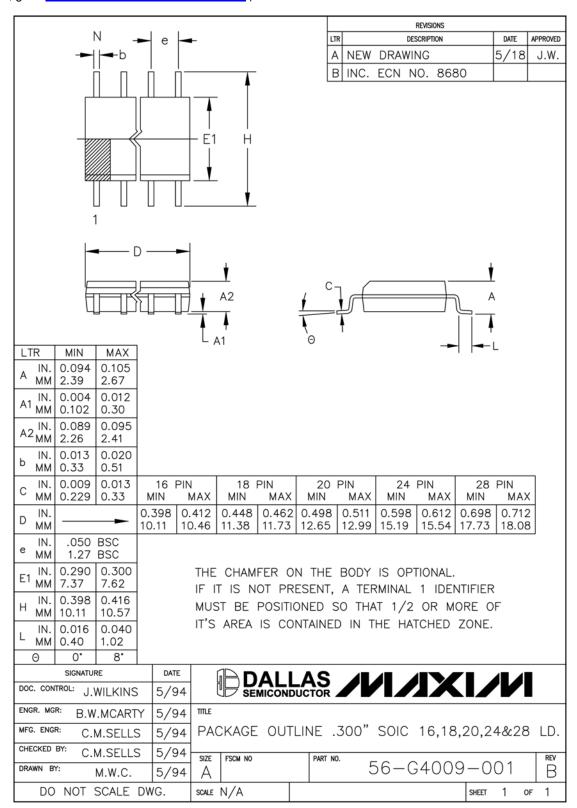

#### PACKAGE INFORMATION

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/DallasPackInfo">www.maxim-ic.com/DallasPackInfo</a>.)

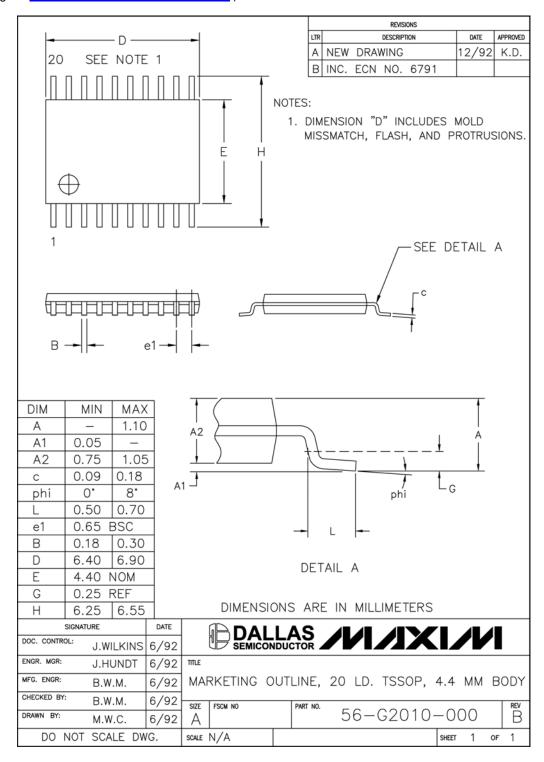

# **PACKAGE INFORMATION (continued)**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/DallasPackInfo">www.maxim-ic.com/DallasPackInfo</a>.)

8 of 8

Maxim/Dallas Semiconductor cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim/Dallas Semiconductor product. No circuit patent licenses are implied. Maxim/Dallas Semiconductor reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 © 2006 Maxim Integrated Products • Printed USA

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# Maxim Integrated:

DS21S07AE DS21S07AS DS21S07AE+ DS21S07AE+T&R DS21S07AS+