## **Electrical Characteristics**

$(V_{DD} = 10V, +V_{IN} = 48V, Discharge = -V_{IN} = 0V, R_{BIAS} = 820K\Omega, R_{OSC} = 910K\Omega, T_{\Delta} = 25^{\circ}C, unless otherwise specified)$

| Symbol               | Parameters                                               | Min     | Тур            | Max  | Unit | Conditions |                                      |

|----------------------|----------------------------------------------------------|---------|----------------|------|------|------------|--------------------------------------|

| Refere               | nce                                                      |         | •              |      |      |            |                                      |

| V <sub>REF</sub>     | Output Voltage                                           |         | 3.92           | 4.00 | 4.08 | V          | $R_L = 10M\Omega$                    |

| Z <sub>OUT</sub>     | Output Impedance <sup>1</sup>                            |         | 15             | 30   | 45   | ΚΩ         | L                                    |

| I <sub>SHORT</sub>   | Short Circuit Current                                    |         |                | 100  | 130  | μΑ         | $V_{REF} = -V_{IN}$                  |

| $\Delta V_{REF}$     | Change in V <sub>REF</sub> with Temp                     | erature |                | 0.25 |      | mV/°C      | INC. IIV                             |

| Oscilla <sup>.</sup> | '                                                        |         |                |      |      |            |                                      |

| f <sub>MAX</sub>     | Maximum Oscillator Freque                                | encv    | 1.0            | 3.0  |      | MHz        | $R_{OSC} = 0\Omega$                  |

| f <sub>OSC</sub>     | Initial Accuracy <sup>2</sup>                            | ,       | 32             | 40   | 48   | KHz        | Tosc Maria                           |

| ·0sc                 | Voltage Stability <sup>1</sup>                           |         | 02             |      | 15   | %          | 9.5V < V <sub>DD</sub> < 13.5V       |

|                      | Temperature Coefficient <sup>1</sup>                     |         |                | 170  |      | ppm/°C     | Jeres C DD C Leve C                  |

| PWM                  | Tomporature Coemoloni                                    |         |                |      |      | pp         |                                      |

| D <sub>MAX</sub>     | Maximum Duty Cycle <sup>1</sup>                          | HV9105  | 49.0           | 49.4 | 49.6 | %          |                                      |

| DMAX                 |                                                          | HV9108  | 99.0           | 99.4 | 99.6 | /0         |                                      |

|                      | Deadtime <sup>1</sup>                                    | HV9108  |                | 100  |      | nsec       |                                      |

| D <sub>MIN</sub>     | Minimum Duty Cycle                                       | I       |                |      | 0    | %          |                                      |

|                      | Minimum Pulse Width Before Pulse Drops Out <sup>1</sup>  |         |                | 110  | 175  | nsec       |                                      |

| Error A              | mplifier                                                 |         |                |      |      |            |                                      |

| V <sub>FB</sub>      | Feedback Voltage                                         |         | 3.96           | 4.00 | 4.04 | V          | V <sub>FB</sub> Shorted to Comp      |

| I <sub>IN</sub>      | Input Bias Current                                       |         |                | 25   | 500  | nA         | V <sub>FB</sub> = 4.0V               |

| V <sub>OS</sub>      | Input Offset Voltage                                     |         | nulled at trim |      |      | mV         |                                      |

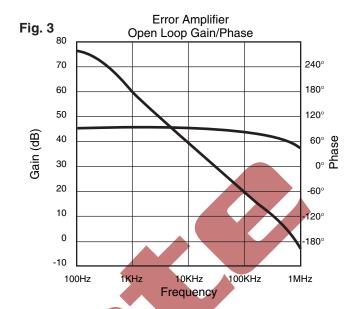

| A <sub>VOL</sub>     | Open Loop Voltage Gain <sup>1</sup>                      |         | 60             | 80   |      | dB         |                                      |

| gbw                  | Unity Gain Bandwidth <sup>1</sup>                        |         | 0.5            | 0.8  |      | MHz        |                                      |

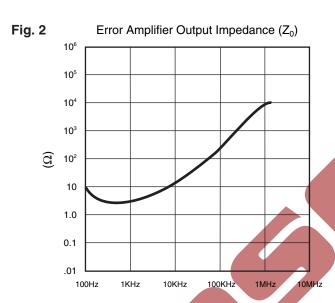

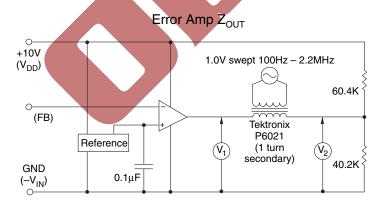

| Z <sub>OUT</sub>     | Output Impedance <sup>1</sup>                            |         | See Fig. 2     |      |      | Ω          |                                      |

| I <sub>SOURCE</sub>  | Output Source Current                                    |         |                | -1.3 | -1.0 | mA         | V <sub>FB</sub> = 3.4V               |

| I <sub>SINK</sub>    | Output Sink Current                                      |         | 50             | 80   |      | μΑ         | V <sub>FB</sub> = 4.5V               |

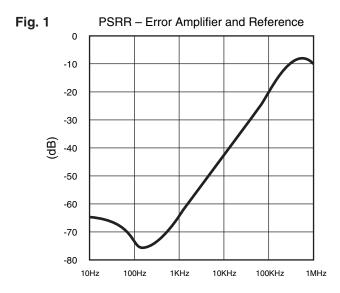

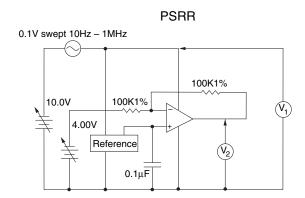

| PSRR                 | Power Supply Rejection <sup>1</sup>                      |         |                |      |      |            |                                      |

| Curren               | t Limit                                                  |         |                |      |      |            |                                      |

| V <sub>SOURCE</sub>  | Threshold Voltage                                        |         | 1.0            | 1.2  | 1.4  | V          | $V_{FB} = 0V, R_L = 100\Omega$       |

| t <sub>d</sub>       | Delay to Output <sup>1</sup>                             |         |                | 150  | 200  | ns         | $V_{SOURCE} = 1.5V, R_L = 100\Omega$ |

| re-Re                | gulator/Startup                                          |         |                |      |      |            |                                      |

| +V <sub>IN</sub>     | Allowable Input Voltage                                  |         |                |      | 120  | V          | $I_{IN} = 10\mu A$                   |

|                      | Input Leakage Current                                    |         |                |      | 10   | μΑ         | V <sub>DD</sub> > 9.4V               |

| V <sub>TH</sub>      | V <sub>DD</sub> Pre-regulator Turn-off Threshold Voltage |         | 7.8            | 8.6  | 9.4  | V          | I <sub>PREREG</sub> = 10μA           |

|                      | Undervoltage Lockout                                     |         | 1              |      | ı    | 1          | T.                                   |

### Notes:

$<sup>{\</sup>it 1. } \ {\it Guaranteed by design. Not subject to production test.}$

<sup>2.</sup> Stray capacitance on OSC IN pin ≤5pF.

# **Electrical Characteristics** (Continued)

$(V_{DD}=10V, +V_{IN}=48V, Discharge=-V_{IN}=0V, R_{BIAS}=820K\Omega, R_{OSC}=910K\Omega, T_{A}=25^{\circ}C, unless otherwise specified)$

| Symbol Parameters | Min | Тур | Max | Unit | Conditions |

|-------------------|-----|-----|-----|------|------------|

| Supply            |     |     |     |      |            |

| I <sub>DD</sub>   | Supply Current  |     |      | 0.6  | mA |                             |

|-------------------|-----------------|-----|------|------|----|-----------------------------|

|                   |                 |     | 0.35 |      | mA | Shutdown = -V <sub>IN</sub> |

| I <sub>BIAS</sub> | Bias Current    |     | 7.5  |      | μΑ |                             |

| V <sub>DD</sub>   | Operating Range | 9.0 |      | 13.5 | V  |                             |

## Logic

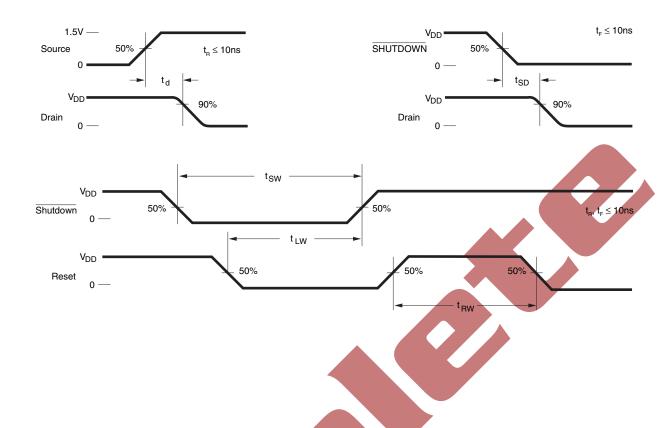

| t <sub>SD</sub> | Shutdown Delay Time <sup>1</sup>  |     | 50  | 100 | ns V <sub>SOURCE</sub> = -V <sub>IN</sub> |

|-----------------|-----------------------------------|-----|-----|-----|-------------------------------------------|

| t <sub>SW</sub> | Shutdown Pulse Width <sup>1</sup> | 50  |     |     | ns                                        |

| t <sub>RW</sub> | RESET Pulse Width <sup>1</sup>    | 50  |     |     | ns                                        |

| t <sub>LW</sub> | Latching Pulse Width <sup>1</sup> | 25  |     |     | ns                                        |

| V <sub>IL</sub> | Input Low Voltage                 |     |     | 2.0 | V                                         |

| V <sub>IH</sub> | Input High Voltage                | 7.0 |     |     | V                                         |

| I <sub>IH</sub> | Input High Current                |     | 1.0 | 5.0 | $\mu A$ $V_{IN} = 10V$                    |

| I <sub>IL</sub> | Input Low Current                 |     | -25 | -35 | $\mu A$ $V_{IN} = 0V$                     |

## **MOSFET Switch**

| BV <sub>DSS</sub>   | Breakdown Voltage               | 200 | 240 |     | V  | $V_{SOURCE} = \overline{Shutdown} = 0V,$                       |

|---------------------|---------------------------------|-----|-----|-----|----|----------------------------------------------------------------|

|                     |                                 |     |     |     |    | $I_D = 100\mu A$                                               |

| R <sub>DS(ON)</sub> | Drain-to-Source On-resistance   |     | 3.5 | 5.0 | Ω  | $V_{SOURCE} = 0V, I_D = 100mA$                                 |

| I <sub>DSS</sub>    | OFF State Drain Leakage Current |     |     | 10  | μΑ | $V_{SOURCE} = \overline{Shutdown} = 0V,$<br>$V_{DRAIN} = 100V$ |

| C <sub>DS</sub>     | Drain Capacitance               |     | 35  |     | pF | $V_{DS} = 25V, \overline{Shutdown} = 0V$                       |

#### Note:

## **Truth Table**

| Shutdown          | Reset             | Output                      |  |  |  |  |  |

|-------------------|-------------------|-----------------------------|--|--|--|--|--|

| Н                 | H                 | Normal Operation            |  |  |  |  |  |

| Н                 | $H \rightarrow L$ | Normal Operation, No Change |  |  |  |  |  |

| L                 | Н                 | Off, Not Latched            |  |  |  |  |  |

| L                 | L                 | Off, Latched                |  |  |  |  |  |

| $L \rightarrow H$ | L                 | Off, Latched, No Change     |  |  |  |  |  |

<sup>1.</sup> Guaranteed by design. Not subject to production test.

# **Switching Waveforms**

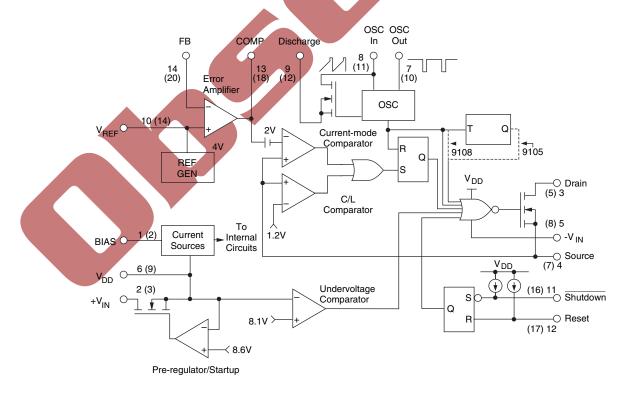

# **Functional Block Diagram**

Pin numbers in parentheses are for PLCC package.

# **Typical Performance Curves**

## **Test Circuits**

NOTE: Set Feedback Voltage so that  $V_{COMP} = V_{DIVIDE} \pm 1mV$  before connecting transformer

## **Technical Description**

## **Preregulator**

The preregulator/startup circuit for the HV9105/08 consists of a high-voltage N-channel depletion-mode DMOS transistor driven by an error amplifier to form a controlled current path between the  $V_{IN}$  terminal and the  $V_{DD}$  terminal of the HV9105/08. Maximum current (about 20 mA) occurs when  $V_{DD} = 0$ , with current reducing as  $V_{DD}$  rises. This path shuts off altogether when  $V_{DD}$  rises to somewhere between 7.8 and 9.4V, so that if  $V_{DD}$  is held at 10 or 12V by an external source (generally the supply the chip is controlling) no current other than leakage is drawn through the high voltage transistor. This minimizes dissipation.

An external capacitor between  $V_{DD}$  and  $V_{SS}$  is generally required to store energy used by the chip during the time between shutoff of the high voltage path and the  $V_{DD}$  supply's output rising enough to take over the powering of the chip. This capacitor generally also serves as the output filter capacitor for that output from the supply.  $1.0\mu F$  is generally sufficient to assure against double-starting. Capacitors as small as  $0.1\mu F$  can work when faster response from the  $V_{DD}$  line is required. The chosen capacitor should have very good high frequency characteristics and be mounted so that the sum of the lead length between capacitor and IC for both leads is less than 2.5 cm. Stacked polyester or ceramic capacitors work well. Electrolytic capacitors are generally not suitable.

A common resistor divider string is used to monitor  $V_{DD}$  for both the undervoltage lockout circuit and the shutoff circuit of the high voltage FET. Setting the undervoltage sense point about 0.6V lower on the string than the FET shutoff point guarantees that the undervoltage lockout always releases before the FET shuts off.

#### **Bias Circuit**

An external bias resistor, connected between the bias pin and  $V_{SS}$  is required by the HV9105/08 to set currents in a series of current mirrors used by the analog sections of the chip. Nominal external bias current requirement is 7.5µA, which can be set by a 820K $\Omega$  to 1.3M $\Omega$  resistor if a 10V  $V_{DD}$  is used, or a 1.2M $\Omega$  to 2.0M $\Omega$  resistor if a 12V  $V_{DD}$  is used. A precision resistor is NOT required;  $\pm$  5% is fine.

For extremely low power operation, the value of bias current can be reduced to as low as  $4.0\mu A$  by further increases in the value of the bias resistor.

### **Clock Oscillator**

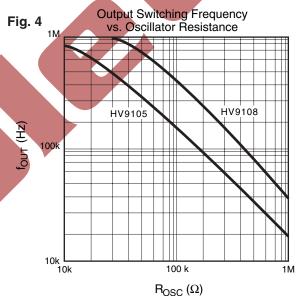

The clock oscillator of the HV9105/08 consists of a ring of CMOS inverters, timing capacitors, a capacitor discharge FET, and, in the 50% maximum duty cycle version, a frequency dividing flipflop. A single external resistor between the OSC In and OSC Out pins is required to set oscillator frequency (see Fig. 4). For the 50% maximum duty cycle versions the 'Discharge' pin is internally connected to GND. For the 99% duty cycle version, 'Discharge' can either be connected to  $\rm V_{SS}$  directly or connected to  $\rm V_{SS}$  through a resistor used to set a deadtime.

One difference exists between the Supertex HV9105/08 and competitive 9105 parts. The oscillator of the Supertex HV9105/08 is shut off when a shutoff command is received. This saves about  $100\mu A$  of quiescent current, which aids in the construction of power supplies to meet CCITT specification I.430, and in other situations where an absolute minimum of quiescent power dissipation is required.

### Reference

The reference section of the HV9105/08 consists of a stable bandgap reference followed by a buffer amplifier which scales the voltage up to approximately 4.0V. The scaling resistors of the reference buffer amplifier are trimmed during manufacture so that the output of the error amplifier when connected in a gain of -1 configuration is as close to 4.000V as possible. This nulls out any input offset of the error amplifier. As a consequence, even though the observed reference voltage of a specific part may not be exactly 4.0V, the feedback voltage required for proper regulation will be 4.0V.

A resistor of approximately  $50 \mathrm{K}\Omega$  is placed internally between the output of the reference buffer amplifier and the circuitry it feeds (reference output pin and non-inverting input to the error amplifier). This allows overriding the internal reference with a low-impedance voltage source  $\leq 6.0 \mathrm{V}$ . In general, because the reference voltage of the Supertex HV9105/08 is not noisy, as some previous devices have been, overriding the reference should seldom be necessary.

Because the reference is a high impedance node, and usually there will be significant electrical noise near it, a bypass capacitor between the reference pin and  $V_{\rm SS}$  is strongly recommended. The reference buffer amplifier is intentionally compensated to be stable with a capacitive load of 0.01 to 0.1 $\mu$ F.

## **Error Amplifier**

The error amplifier is a true low-power differential input operational amplifier intended for around-the-amplifier compensation. It is of mixed CMOS-bipolar construction: a PMOS input stage is used so the common-mode range includes ground and the input impedance is very high. This is followed by bipolar gain stages which provide high gain without the electrical noise of all-MOS amplifiers. The amplifier is unity-gain stable.

### **Current Sense Comparators**

The HV9105/08 uses a true dual comparator system with independent comparators for modulation and current limiting. This allows the designer greater latitude in compensation design, as there are no clamps (except ESD protection) on the compensation pin. Like the error amplifier, the comparators are of low-noise BiCMOS construction.

#### Remote Shutdown

The shutdown and reset pins can be used to perform either latching or non-latching shutdown of a converter as required. These pins have internal current source pull-ups so they can be driven from open-drain logic. When not used, they should be left open, or connected to  $V_{\rm DD}$ .

#### Main Switch

The main switch is a normal N-channel power MOSFET. Unlike the situation with competitive devices, the body diode can be used if desired without destroying the chip.

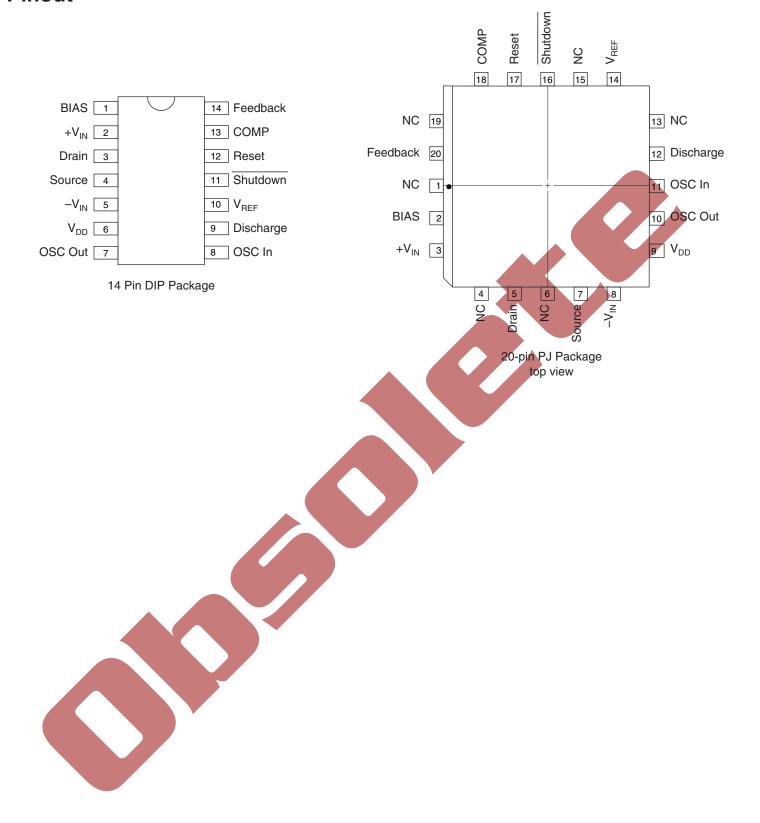

## **Pinout**

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# Microchip:

HV9108PJ HV9108PJ-M910 HV9108P