# **TABLE OF CONTENTS**

| Features                                    | 1  |

|---------------------------------------------|----|

| Applications                                | 1  |

| General Description                         | 1  |

| Revision History                            | 2  |

| Functional Block Diagram                    | 3  |

| Specifications                              | 4  |

| Digital Input/Output Specifications         | 5  |

| Absolute Maximum Ratings                    | 6  |

| Thermal Resistance                          | 6  |

| ESD Caution                                 | 6  |

| Pin Configuration and Function Descriptions | 7  |

| Typical Performance Characteristics         | 8  |

| Theory of Operation                         | 14 |

| Overview                                    | 14 |

| Power-Down Operation                        | 14 |

| Gain Selection                              | 14 |

| Pop-and-Click Suppression                   | 14 |

| Output Modulation Description               | 14 |

| EMI Noise                                   | 15 |

| Output Current Sensing                                     | 15 |

|------------------------------------------------------------|----|

| Output Voltage Sensing                                     | 15 |

| PVDD Sensing                                               | 15 |

| Serial Data Input/Output                                   | 16 |

| TDM Operating Mode                                         | 16 |

| I <sup>2</sup> S and Left Justified Operating Mode         | 16 |

| Multichip I <sup>2</sup> S Operating Mode                  | 17 |

| PDM Output Mode                                            | 17 |

| Timing Diagrams, TDM Mode                                  | 18 |

| Timing Diagrams, I <sup>2</sup> S and Left Justified Modes | 18 |

| Timing Diagrams, Multichip I <sup>2</sup> S Mode           | 19 |

| Timing Diagrams, PDM Mode                                  | 20 |

| Applications Information                                   | 21 |

| Layout                                                     | 21 |

| Input Capacitor Selection                                  | 21 |

| Power Supply Decoupling                                    | 21 |

| Outline Dimensions                                         | 22 |

| Ordering Guide                                             | 22 |

### **REVISION HISTORY**

10/12—Revision 0: Initial Version

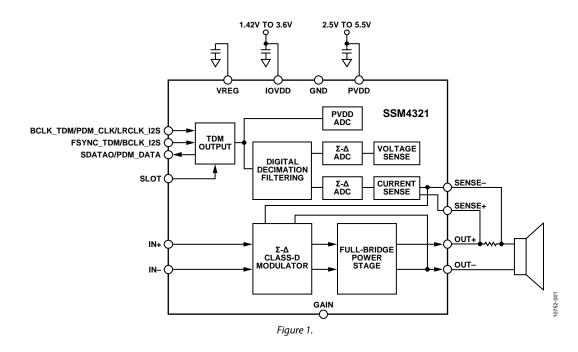

# **FUNCTIONAL BLOCK DIAGRAM**

# **SPECIFICATIONS**

$PVDD = 5.0 \text{ V}, IOVDD = 1.8 \text{ V}, f_S = 24 \text{ kHz with } I^2S \text{ output}, T_A = 25^{\circ}C, R_L = 8 \Omega + 33 \mu\text{H}, unless otherwise noted. For } R_L = 8 \Omega, use a 200 \text{ m}\Omega \text{ V/I sense resistor}; for } R_L = 4 \Omega, use a 100 \text{ m}\Omega \text{ V/I sense resistor}; for } R_L = 3 \Omega, use a 75 \text{ m}\Omega \text{ V/I sense resistor}.$

Table 1.

| Parameter                            | Symbol               | Test Conditions/Comments                                                              | Min  | Тур  | Max      | Unit |

|--------------------------------------|----------------------|---------------------------------------------------------------------------------------|------|------|----------|------|

| DEVICE CHARACTERISTICS               |                      |                                                                                       |      |      |          |      |

| Output Power, RMS                    | P <sub>OUT</sub>     | f = 1 kHz, 20 kHz bandwidth                                                           |      |      |          |      |

|                                      |                      | $R_L = 8 \Omega$ , THD = 1%, PVDD = 5.0 V                                             |      | 1.35 |          | W    |

|                                      |                      | $R_L = 8 \Omega$ , THD = 1%, PVDD = 3.6 V                                             |      | 0.70 |          | W    |

|                                      |                      | $R_L = 8 \Omega$ , THD = 1%, PVDD = 2.5 V                                             |      | 0.32 |          | W    |

|                                      |                      | $R_L = 8 \Omega$ , THD = 10%, PVDD = 5.0 V                                            |      | 1.70 |          | W    |

|                                      |                      | $R_L = 8 \Omega$ , THD = 10%, PVDD = 3.6 V                                            |      | 0.86 |          | W    |

|                                      |                      | $R_L = 8 \Omega$ , THD = 10%, PVDD = 2.5 V                                            |      | 0.4  |          | W    |

|                                      |                      | $R_L = 4 \Omega$ , THD = 1%, PVDD = 5.0 V                                             |      | 2.22 |          | W    |

|                                      |                      | $R_L = 4 \Omega$ , THD = 1%, PVDD = 3.6 V                                             |      | 1.12 |          | W    |

|                                      |                      | $R_L = 4 \Omega$ , THD = 1%, PVDD = 2.5 V                                             |      | 0.51 |          | W    |

|                                      |                      | $R_L = 4 \Omega$ , THD = 10%, PVDD = 5.0 V                                            |      | 2.8  |          | W    |

|                                      |                      | $R_L = 4 \Omega$ , THD = 10%, PVDD = 3.6 V                                            |      | 1.42 |          | W    |

|                                      |                      | $R_L = 4 \Omega$ , THD = 10%, PVDD = 2.5 V                                            |      | 0.64 |          | W    |

|                                      |                      | $R_L = 3 \Omega$ , THD = 1%, PVDD = 5.0 V                                             |      | 3.00 |          | W    |

|                                      |                      | $R_1 = 3 \Omega$ , THD = 1%, PVDD = 3.6 V                                             |      | 1.51 |          | W    |

|                                      |                      | $R_L = 3 \Omega$ , THD = 1%, PVDD = 2.5 V                                             |      | 0.68 |          | W    |

|                                      |                      | $R_1 = 3 \Omega$ , THD = 10%, PVDD = 5.0 V                                            |      | 3.77 |          | W    |

|                                      |                      | $R_1 = 3 \Omega$ , THD = 10%, PVDD = 3.6 V                                            |      | 1.90 |          | W    |

|                                      |                      | $R_1 = 3 \Omega$ , THD = 10%, PVDD = 2.5 V                                            |      | 0.86 |          | W    |

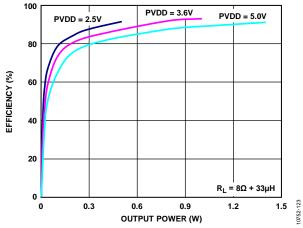

| Efficiency                           | η                    | $P_{OUT} = 1.4 \text{ W into } 8 \Omega, \text{ PVDD} = 5.0 \text{ V}$                |      | 89   |          | %    |

| ,                                    | '                    | $P_{OUT} = 2.8 \text{ W into } 3 \Omega, \text{ PVDD} = 5.0 \text{ V}$                |      | 82   |          | %    |

| Total Harmonic Distortion Plus Noise | THD + N              | $P_{OUT} = 1$ W into 8 Ω, $f = 1$ kHz,<br>PVDD = 5.0 V                                |      | 0.01 |          | %    |

|                                      |                      | $P_{OUT} = 0.5 \text{ W into } 8 \Omega, f = 1 \text{ kHz}, PVDD = 3.6 V$             |      | 0.01 |          | %    |

| Input Common-Mode Voltage<br>Range   | V <sub>CM</sub>      |                                                                                       | 1.0  |      | PVDD – 1 | V    |

| Common-Mode Rejection Ratio          | CMRR <sub>GSM</sub>  | $V_{CM} = 100 \text{ mV rms at } 1 \text{ kHz}$                                       |      | 50   |          | dB   |

| Average Switching Frequency          | f <sub>sw</sub>      |                                                                                       |      | 256  |          | kHz  |

| Clock Frequency                      | f <sub>osc</sub>     |                                                                                       |      | 6.2  |          | MHz  |

| Differential Output Offset Voltage   | V <sub>oos</sub>     | Gain = 6 dB                                                                           |      | 0.3  | 5.0      | mV   |

| POWER SUPPLY                         |                      |                                                                                       |      |      |          |      |

| Supply Voltage Range                 | PVDD                 | Guaranteed from PSRR test                                                             | 2.5  |      | 5.5      | ٧    |

|                                      | IOVDD                |                                                                                       | 1.42 |      | 3.6      | ٧    |

| Power Supply Rejection Ratio         | PSRR <sub>GSM</sub>  | $V_{RIPPLE} = 100 \text{ mV}$ at 217 Hz, inputs are ac-grounded, $C_{IN} = 0.1 \mu F$ |      | 86   |          | dB   |

| Supply Current, PVDD                 | I <sub>SYPVDD</sub>  | $V_{IN} = 0 V$                                                                        |      |      |          |      |

|                                      | 311 100              | No load, PVDD = 5.0 V                                                                 |      | 3.7  |          | mA   |

|                                      |                      | No load, PVDD = 3.6 V                                                                 |      | 3.1  |          | mA   |

|                                      |                      | No load, PVDD = 2.5 V                                                                 |      | 2.9  |          | mA   |

|                                      |                      | $R_1 = 8 \Omega$ , PVDD = 5.0 V                                                       |      | 3.8  |          | mA   |

|                                      |                      | $R_1 = 8 \Omega, PVDD = 3.6 V$                                                        |      | 3.2  |          | mA   |

|                                      |                      | $R_1 = 8 \Omega, PVDD = 2.5 V$                                                        |      | 2.9  |          | mA   |

| Supply Current, IOVDD                | I <sub>SYIOVDD</sub> | IOVDD = 1.8 V                                                                         |      | 0.41 |          | mA   |

| Shutdown Current, PVDD               | I <sub>SDPVDD</sub>  | No BCLK, PVDD = 5.0 V                                                                 |      | 0.1  |          | μΑ   |

| Shutdown Current, IOVDD              | I <sub>SDIOVDD</sub> | No BCLK, IOVDD = 1.8 V                                                                |      | 0.77 |          | μΑ   |

| Parameter                                  | Symbol           | Test Conditions/Comments                                             | Min   | Тур   | Max   | Unit    |

|--------------------------------------------|------------------|----------------------------------------------------------------------|-------|-------|-------|---------|

| GAIN CONTROL                               |                  |                                                                      |       | ·     |       |         |

| Closed-Loop Gain                           | Gain             |                                                                      | 0     |       | 12    | dB      |

| Input Impedance                            | Z <sub>IN</sub>  | BCLK enabled, fixed input impedance (0 dB to 12 dB)                  |       | 80    |       | kΩ      |

| SHUTDOWN CONTROL                           |                  |                                                                      |       |       |       |         |

| Turn-On Time                               | t <sub>wu</sub>  | From BCLK start                                                      |       | 12.5  |       | ms      |

| Turn-Off Time                              | t <sub>SD</sub>  | From BCLK removal                                                    |       | 5     |       | μs      |

| Output Impedance                           | Z <sub>out</sub> | No BCLK                                                              |       | >100  |       | kΩ      |

| AMPLIFIER NOISE PERFORMANCE                |                  |                                                                      |       |       |       |         |

| Output Voltage Noise                       | e <sub>n</sub>   | f = 20 Hz to 20 kHz, inputs are ac-grounded, gain = 6 dB, A-weighted |       |       |       |         |

|                                            |                  | PVDD = 5.0 V                                                         |       | 30    |       | μV      |

|                                            |                  | PVDD = 3.6 V                                                         |       | 30    |       | μV      |

| Signal-to-Noise Ratio                      | SNR              | $P_{OUT} = 1.3 \text{ W}, R_L = 8 \Omega, A\text{-weighted}$         |       | 101   |       | dB      |

| OUTPUT SENSING                             |                  |                                                                      |       |       |       |         |

| Output Sampling Rate, TDM                  | f <sub>s</sub>   | LRCLK/FSYNC pulse rate                                               | 8     |       | 48    | kHz     |

| BCLK Frequency, TDM                        | $f_{BCLK}$       | 1 to 4 slots used                                                    | 0.512 |       | 6.144 | MHz     |

| Voltage Sense Signal-to-Noise<br>Ratio     | SNRV             | A-weighted                                                           |       | 77    |       | dB      |

| Voltage Sense Full-Scale Output<br>Voltage | $V_{FS}$         | Amplifier voltage with 0 dBFS ADC output                             |       | 6     |       | $V_{P}$ |

| Voltage Sense Absolute Accuracy            |                  |                                                                      |       | 1.5   |       | %       |

| Voltage Sense Gain Drift                   |                  | $T_A = 10^{\circ}C$ to $60^{\circ}C$                                 |       | 1     |       | %       |

| Current Sense Signal-to-Noise<br>Ratio     | SNRI             | A-weighted                                                           |       | 72    |       | dB      |

| Current Sense Full-Scale Input<br>Voltage  | V <sub>IS</sub>  | I <sub>SENSE</sub> converter voltage with 0 dBFS ADC output          |       | 0.150 |       | $V_P$   |

| Current Sense Absolute Accuracy            |                  | ·                                                                    |       | 3     |       | %       |

| Current Sense Gain Drift                   |                  | $T_A = 10^{\circ}\text{C}$ to 60°C, ideal $R_{\text{SENSE}}$         |       | 1     |       | %       |

| PVDD Sense Full-Scale Range                | $PV_{FS}$        | PVDD with full-scale ADC output                                      | 2     |       | 6     | V       |

| PVDD Sense Absolute Accuracy               | 13               | · ·                                                                  |       | 3     |       | %       |

| Current and Voltage Sense<br>Linearity     |                  | From –80 dBr to 0 dBr                                                |       |       | 1     | dB      |

| ADC –3 dB Corner Frequency                 | $f_{C}$          | Digital high-pass filter                                             |       |       |       |         |

|                                            |                  | Output $f_s = 48 \text{ kHz}$                                        |       | 3.75  |       | Hz      |

|                                            |                  | Output f <sub>s</sub> = 24 kHz                                       |       | 1.875 |       | Hz      |

## **DIGITAL INPUT/OUTPUT SPECIFICATIONS**

Table 2.

| Parameter                  | Symbol          | Test Conditions/Comments | Min         | Тур | Max                | Unit |

|----------------------------|-----------------|--------------------------|-------------|-----|--------------------|------|

| BCLK, FSYNC PINS           |                 | Ball D2 and Ball D3      |             |     |                    |      |

| Input Voltage High         | V <sub>IH</sub> |                          | 0.7 × IOVDD |     | 3.6                | ٧    |

| Input Voltage Low          | V <sub>IL</sub> |                          | -0.3        |     | $0.3 \times IOVDD$ | ٧    |

| Input Leakage Current High | I <sub>IH</sub> |                          |             |     | 1                  | μΑ   |

| Input Leakage Current Low  | I <sub>IL</sub> |                          |             |     | 1                  | μΑ   |

| Input Capacitance          | C <sub>IN</sub> |                          |             |     | 5                  | рF   |

| SDATAO/PDM_DATA PIN        |                 | Ball D1                  |             |     |                    |      |

| Output Drive Strength      |                 | IOVDD = 1.5 V            |             | 3.5 |                    | mA   |

|                            |                 | IOVDD = 1.8 V            |             | 4.5 |                    | mA   |

## **ABSOLUTE MAXIMUM RATINGS**

Absolute maximum ratings apply at 25°C, unless otherwise noted.

Table 3.

| Parameter                            | Rating          |

|--------------------------------------|-----------------|

| PVDD Supply Voltage                  | 6 V             |

| IOVDD Supply Voltage                 | 3.6 V           |

| Input Voltage                        | PVDD            |

| Common-Mode Input Voltage            | PVDD            |

| Storage Temperature Range            | −65°C to +150°C |

| Operating Temperature Range          | -40°C to +85°C  |

| Junction Temperature Range           | −65°C to +165°C |

| Lead Temperature (Soldering, 60 sec) | 300°C           |

| ESD Susceptibility                   | 4 kV            |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

Junction-to-air thermal resistance  $(\theta_{JA})$  is specified for the worst-case conditions, that is, a device soldered in a printed circuit board (PCB) for surface-mount packages.

**Table 4. Thermal Resistance**

| Package Type                     | $\theta_{JA}^{1}$ | Unit |

|----------------------------------|-------------------|------|

| 16-Ball, 1.74 mm × 1.74 mm WLCSP | 665               | °C/W |

$<sup>^{1}\,\</sup>text{The}\,\theta_{JA}\,\text{specification}$  is measured on a JEDEC standard 4-layer PCB.

#### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.**Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

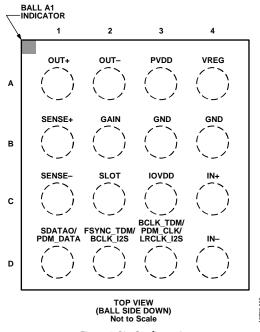

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

**Table 5. Pin Function Descriptions**

| Pin No. | Mnemonic                       | Description                                                       |

|---------|--------------------------------|-------------------------------------------------------------------|

| A1      | OUT+                           | Noninverting Output.                                              |

| A2      | OUT-                           | Inverting Output.                                                 |

| A3      | PVDD                           | Amplifier Power Supply.                                           |

| A4      | VREG                           | Internal LDO Regulator Output.                                    |

| B1      | SENSE+                         | Current Sense Positive Input.                                     |

| B2      | GAIN                           | Gain Control Pin.                                                 |

| B3, B4  | GND                            | Ground.                                                           |

| C1      | SENSE-                         | Current Sense Negative Input.                                     |

| C2      | SLOT                           | TDM Slot Selection Input.                                         |

| C3      | IOVDD                          | Input/Output Digital Power Supply.                                |

| C4      | IN+                            | Noninverting Input.                                               |

| D1      | SDATAO/PDM_DATA                | TDM Serial Data Output/PDM Data Output.                           |

| D2      | FSYNC_TDM/BCLK_I2S             | TDM Frame Synchronization Input/I <sup>2</sup> S Bit Clock Input. |

| D3      | BCLK_TDM/PDM_CLK/<br>LRCLK_I2S | TDM Bit Clock Input/PDM Clock Input/I <sup>2</sup> S LRCLK Input. |

| D4      | IN-                            | Inverting Input.                                                  |

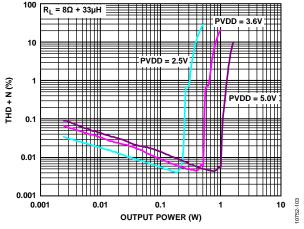

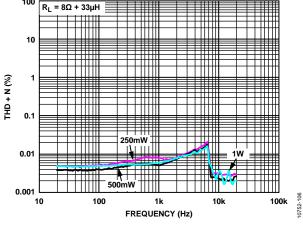

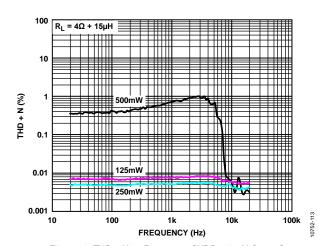

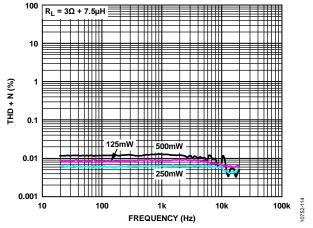

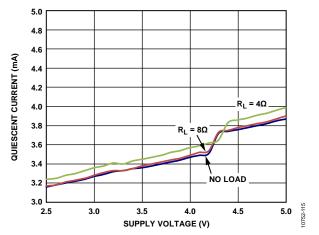

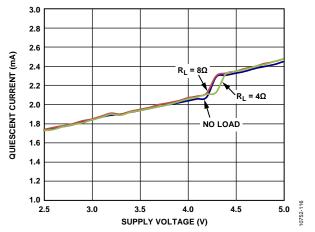

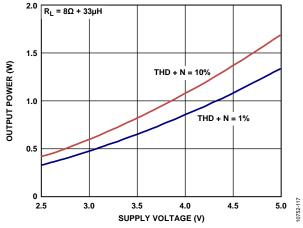

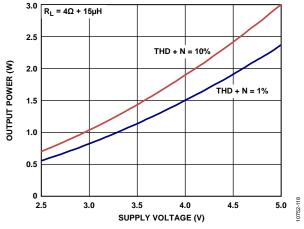

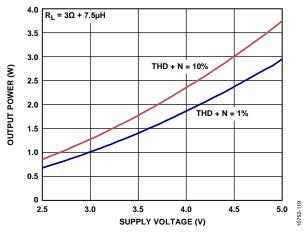

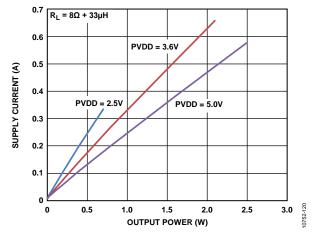

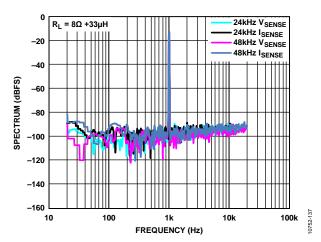

## TYPICAL PERFORMANCE CHARACTERISTICS

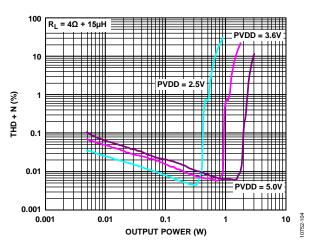

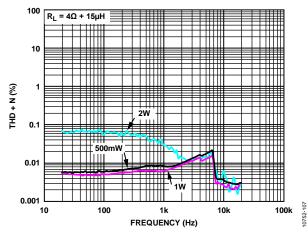

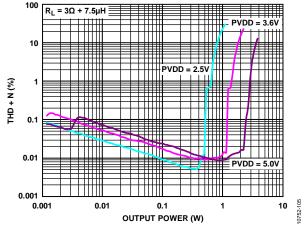

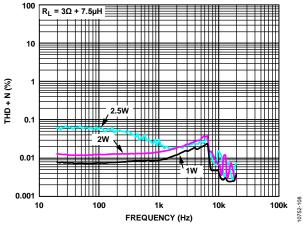

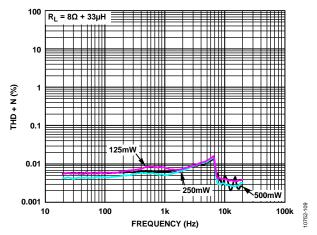

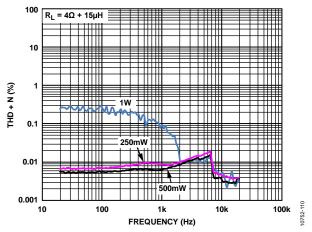

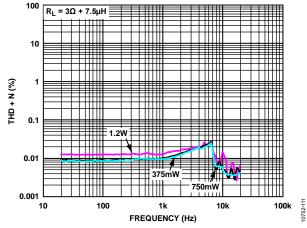

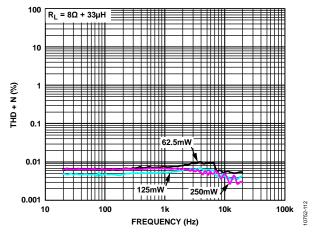

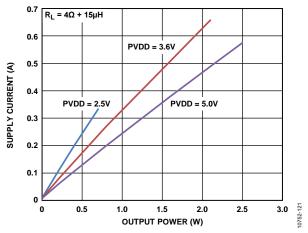

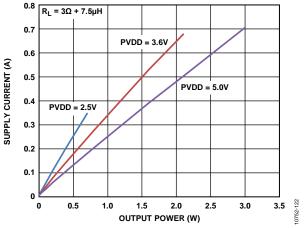

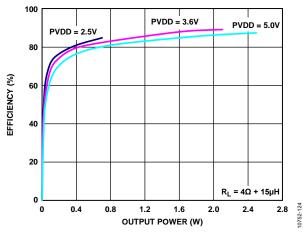

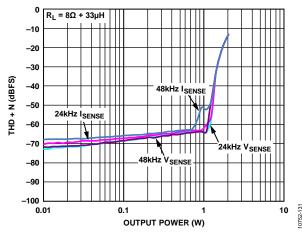

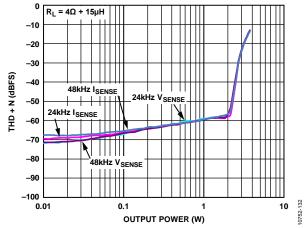

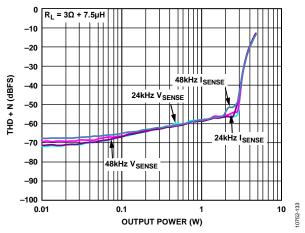

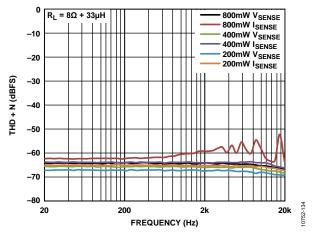

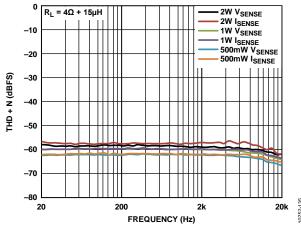

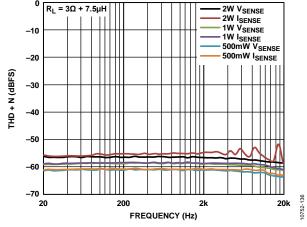

PVDD = 5.0 V, IOVDD = 1.8 V,  $f_s$  = 24 kHz with I<sup>2</sup>S output, gain = 6 dB,  $T_A$  = 25°C, unless otherwise noted. For  $R_L$  = 8  $\Omega$ , use a 200 m $\Omega$  V/I sense resistor; for  $R_L$  = 4  $\Omega$ , use a 100 m $\Omega$  V/I sense resistor; for  $R_L$  = 3  $\Omega$ , use a 75 m $\Omega$  V/I sense resistor.

Figure 3. THD + N vs. Output Power into 8  $\Omega$

Figure 6. THD + N vs. Frequency, PVDD = 5 V,  $R_L = 8 \Omega$

Figure 4. THD + N vs. Output Power into 4  $\Omega$

Figure 7. THD + N vs. Frequency, PVDD = 5 V,  $R_L$  = 4  $\Omega$

Figure 5. THD + N vs. Output Power into 3  $\Omega$

Figure 8. THD + N vs. Frequency, PVDD = 5 V,  $R_L = 3 \Omega$

Figure 9. THD + N vs. Frequency, PVDD = 3.6 V,  $R_L = 8 \Omega$

Figure 10. THD + N vs. Frequency, PVDD = 3.6 V,  $R_1 = 4 \Omega$

Figure 11. THD + N vs. Frequency, PVDD = 3.6 V,  $R_L$  = 3  $\Omega$

Figure 12. THD + N vs. Frequency, PVDD = 2.5 V,  $R_L = 8 \Omega$

Figure 13. THD + N vs. Frequency, PVDD = 2.5 V,  $R_L$  = 4  $\Omega$

Figure 14. THD + N vs. Frequency, PVDD = 2.5 V,  $R_L$  = 3  $\Omega$

Figure 15. Quiescent Current vs. PVDD Supply Voltage, ADC Sense Enabled

Figure 16. Quiescent Current vs. PVDD Supply Voltage, ADC Sense Disabled

Figure 17. Maximum Output Power vs. PVDD Supply Voltage,  $R_L = 8 \Omega$

Figure 18. Maximum Output Power vs. PVDD Supply Voltage,  $R_L = 4 \Omega$

Figure 19. Maximum Output Power vs. PVDD Supply Voltage,  $R_1 = 3 \Omega$

Figure 20. Supply Current vs. Output Power into 8  $\Omega$

Figure 21. Supply Current vs. Output Power into 4  $\Omega$

Figure 22. Supply Current vs. Output Power into 3  $\Omega$

Figure 23. Efficiency vs. Output Power into 8  $\Omega$

Figure 24. Efficiency vs. Output Power into 4  $\Omega$

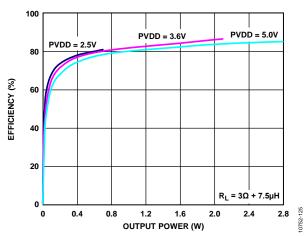

Figure 25. Efficiency vs. Output Power into 3  $\Omega$

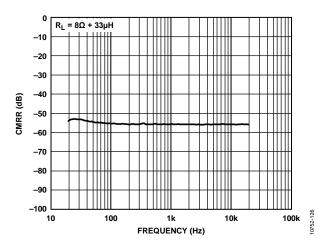

Figure 26. Common-Mode Rejection Ratio (CMRR) vs. Frequency, PVDD = 5 V,  $R_{\rm L}$  = 8  $\Omega$

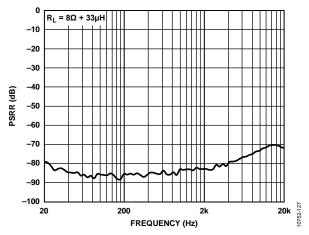

Figure 27. Power Supply Rejection Ratio (PSRR) vs. Frequency,  $PVDD = 5 \text{ V}, R_L = 8 \Omega$

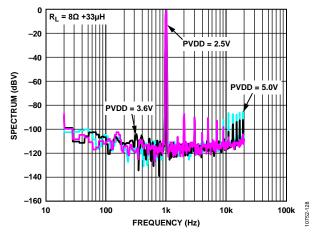

Figure 28. Output Spectrum vs. Frequency (FFT),  $P_{OUT} = 100$  mW,  $R_L = 8 \Omega$

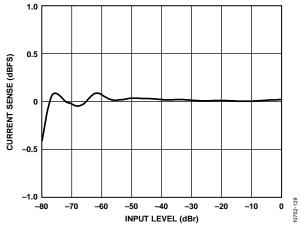

Figure 29. Current Sense Linearity

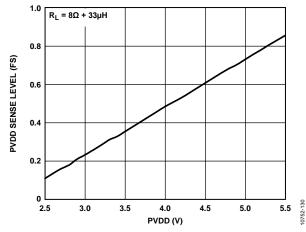

Figure 30. PVDD ADC Sense Level vs. PVDD Range,  $R_{\rm L}$  = 8  $\Omega$

Figure 31. Sense ADC THD + N vs. Output Power into 8  $\Omega$

Figure 32. Sense ADC THD + N vs. Output Power into 4  $\Omega$

Figure 33. Sense ADC THD + N vs. Output Power into 3  $\Omega$

Figure 34. Sense ADC THD + N vs. Frequency, PVDD = 5 V,  $R_L$  = 8  $\Omega$

Figure 35. Sense ADC THD + N vs. Frequency, PVDD = 5 V,  $R_L = 4 \Omega$

Figure 36. Sense ADC THD + N vs. Frequency, PVDD = 5 V,  $R_L = 3 \Omega$

Figure 37. Output Spectrum of Sense ADC vs. Frequency (FFT),  $P_{\rm OUT}$  = 100 mW,  $R_{\rm L}$  = 8  $\Omega$

# THEORY OF OPERATION OVERVIEW

The SSM4321 mono Class-D audio amplifier features a filterless modulation scheme that greatly reduces the external component count, conserving board space and, thus, reducing system cost. The SSM4321 does not require an output filter but, instead, relies on the inherent inductance of the speaker coil and the natural filtering of the speaker and human ear to fully recover the audio component of the square wave output.

Most Class-D amplifiers use some variation of pulse-width modulation (PWM), but the SSM4321 uses  $\Sigma$ - $\Delta$  modulation to determine the switching pattern of the output devices, resulting in a number of important benefits.

- Σ-Δ modulators do not produce a sharp peak with many harmonics in the AM frequency band, as pulse-width modulators often do.

- Σ-Δ modulation reduces the amplitude of spectral components at high frequencies, thus reducing EMI emissions that might otherwise be radiated by speakers and long cable traces.

- Due to the inherent spread-spectrum nature of Σ-Δ modulation, the need for oscillator synchronization is eliminated for designs that incorporate multiple SSM4321 amplifiers.

The SSM4321 also integrates overcurrent and overtemperature protection.

#### **POWER-DOWN OPERATION**

The SSM4321 contains a clock loss detect circuit that works with the BCLK input clock. When no BCLK is present, the part automatically powers down all internal circuitry to its lowest power state. When a BCLK is returned, the part automatically powers up.

If BCLK is active but FSYNC or LRCLK is not present, the amplifier continues to operate, but the ADC, sense blocks, and digital processing are shut down, reducing quiescent current when the output sense data is not needed. The ADC shutdown feature is not available in PDM operating mode.

#### **GAIN SELECTION**

The gain of the SSM4321 can be set from 0 dB to 12 dB in 3 dB steps using the GAIN pin and one (optional) external resistor. The external resistor is used to select the 9 dB or 12 dB gain setting (see Table 6).

Table 6. Setting the Gain of the SSM4321 with the GAIN Pin

| Gain Setting (dB) | GAIN Pin Configuration                       |

|-------------------|----------------------------------------------|

| 0                 | Tie to GND                                   |

| 3                 | Open                                         |

| 6                 | Tie to PVDD                                  |

| 9                 | Tie to GND through a 47 kΩ resistor          |

| 12                | Tie to PVDD through a 47 k $\Omega$ resistor |

#### **POP-AND-CLICK SUPPRESSION**

Voltage transients at the output of audio amplifiers can occur when shutdown is activated or deactivated. Voltage transients as low as 10 mV can be heard as an audible pop in the speaker. Pops and clicks can also be classified as undesirable audible transients generated by the amplifier system and, therefore, as not coming from the system input signal.

The SSM4321 has a pop-and-click suppression architecture that reduces these output transients, resulting in noiseless activation and deactivation.

#### **OUTPUT MODULATION DESCRIPTION**

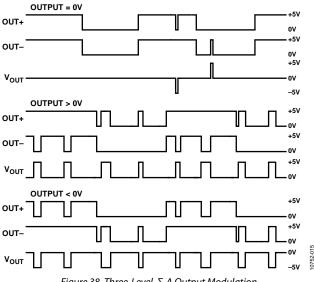

The SSM4321 uses three-level,  $\Sigma$ - $\Delta$  output modulation. Each output can swing from GND to PVDD and vice versa. Ideally, when no input signal is present, the output differential voltage is 0 V because there is no need to generate a pulse. In a real-world situation, noise sources are always present.

Due to the constant presence of noise, a differential pulse is generated, when required, in response to this stimulus. A small amount of current flows into the inductive load when the differential pulse is generated.

Most of the time, however, the output differential voltage is 0 V, due to the Analog Devices, Inc., three-level,  $\Sigma$ - $\Delta$  output modulation. This feature ensures that the current flowing through the inductive load is small.

When the user wants to send an input signal, an output pulse (OUT+ and OUT–) is generated to follow the input voltage. The differential pulse density (V $_{\rm OUT}$ ) is increased by raising the input signal level. Figure 38 depicts three-level,  $\Sigma\text{-}\Delta$  output modulation with and without input stimulus.

Figure 38. Three-Level, Σ-Δ Output Modulation With and Without Input Stimulus

#### **EMI NOISE**

The SSM4321 uses a proprietary modulation and spread-spectrum technology to minimize EMI emissions from the device. For applications that have difficulty passing FCC Class B emission tests or experience antenna and RF sensitivity problems, the ultralow EMI architecture of the SSM4321 significantly reduces the radiated emissions at the Class-D outputs, particularly above 100 MHz.

EMI emission tests on the SSM4321 were performed in an FCC-certified EMI laboratory with a 1 kHz input signal, producing 0.5 W of output power into an 8  $\Omega$  load from a 5.0 V supply. The SSM4321 passed FCC Class B limits with 50 cm of unshielded twisted pair speaker cable. Note that reducing the power supply voltage greatly reduces radiated emissions.

#### **OUTPUT CURRENT SENSING**

The SSM4321 uses an external sense resistor to determine the output current flowing to the load. As shown in Figure 1, one end of the sense resistor is tied to one amplifier output pin (OUT+); the other end of the sense resistor is tied to the load, which is also connected to one sense input pin (SENSE-).

The voltage across the sense resistor is proportional to the load current and is sent to an analog-to-digital converter (ADC) running nominally at 128  $f_s$ . The output of this ADC is downsampled using digital filtering. The downsampled signal is output at a rate of 8 kHz to 48 kHz on Slot 1 of the TDM bus. The 16-bit data is in signed fractional format.

The current sense output is scaled so that an output current of 0.75 A (6 V/8  $\Omega$ ) with a 200 m $\Omega$  sense resistor results in full-scale output from the ADC. Table 7 lists the optimal sense resistor values for commonly used output loads.

Table 7. Optimal Sense Resistor for Typical Loads

| Load Value (Ω) | Peak Current (A) | Sense Resistor (mΩ) |

|----------------|------------------|---------------------|

| 8              | 0.75             | 200                 |

| 4              | 1.5              | 100                 |

| 3              | 2                | 75                  |

#### **OUTPUT VOLTAGE SENSING**

The output voltage level is monitored and sent to an ADC running nominally at 128  $f_s$ . The output of this ADC is downsampled using digital filtering. The downsampled signal is output at a rate of 8 kHz to 48 kHz on Slot 2 of the TDM bus. The 16-bit data is in signed fractional format.

#### **PVDD SENSING**

The SSM4321 contains an 8-bit ADC that measures the voltage of the PVDD supply in real time. The output of the ADC is in 8-bit unsigned format and is presented on the 8 MSBs of Slot 3 on the TDM bus. The eight LSBs are driven low.

## SERIAL DATA INPUT/OUTPUT

The SSM4321 includes circuitry to sense output current, output voltage, and the PVDD supply voltage. The output current, output voltage, and PVDD voltage are sent to ADCs. The output of these ADCs is available on the TDM or I²S output serial port. A direct PDM bit stream of voltage and current data (or current and PVDD data) can also be selected.

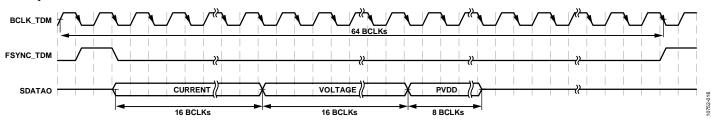

#### **TDM OPERATING MODE**

The digitized output current, output voltage, and PVDD sense signals can be output on a TDM serial port. This serial port is always a slave and requires a bit clock (BCLK) and a frame synchronization signal (FSYNC) to operate. The output data is driven on the SDATAO/PDM\_DATA pin at the IOVDD voltage. (See the Timing Diagrams, TDM Mode section.)

The FSYNC signal operates at the desired sample rate. A rising edge of the FSYNC signal indicates the start of a new frame. For proper operation, this signal should be one BCLK cycle wide, transitioning on a falling BCLK edge. The MSB of the Slot 1 data is output on the SDATAO/PDM\_DATA pin one BCLK cycle later. The SDATAO signal should be latched on a rising edge of BCLK. Each slot is 64 BCLK cycles wide.

The SSM4321 can drive only four slots on its output, but it can work with 8 slots, 12 slots, or 16 slots. In this way, up to four SSM4321 devices can use the same TDM bus. At startup, the number of slots used is recognized automatically by the number of BCLK cycles between FSYNC pulses. Internal clocking is automatically generated from BCLK based on the determined BCLK rate.

The set of four TDM slots to be driven is determined by the configuration of the SLOT pin on the SSM4321 (see Table 8). The value of the SLOT pin must be stable at startup.

**Table 8. TDM Slot Selection**

| Device Setting              | SLOT Pin Configuration                        |

|-----------------------------|-----------------------------------------------|

| TDM Slot 1 to Slot 4 used   | Tie to IOVDD                                  |

| TDM Slot 5 to Slot 8 used   | Open                                          |

| TDM Slot 9 to Slot 12 used  | Tie to GND                                    |

| TDM Slot 13 to Slot 16 used | Tie to IOVDD through a 47 k $\Omega$ resistor |

The SSM4321 sets the SDATAO/PDM\_DATA pin to a high impedance state when a slot is present that is not being driven. Connect a pull-down resistor to the SDATAO/PDM\_DATA pin so that it is always in a known state.

With a single SSM4321 operating with four slots, Slot 1 is for the output current, Slot 2 is for the output voltage, Slot 3 is for the PVDD supply, and Slot 4 is not driven. With more than four slots, this pattern is repeated. Table 9 shows an example with three SSM4321 devices and 12 TDM slots.

Table 9. TDM Output Slot Example—Three SSM4321 Devices

|   |          | I I                      |

|---|----------|--------------------------|

| • | TDM Slot | Data Present             |

|   | 1        | Output current, Device 1 |

|   | 2        | Output voltage, Device 1 |

|   | 3        | PVDD voltage, Device 1   |

|   | 4        | High-Z                   |

|   | 5        | Output current, Device 2 |

|   | 6        | Output voltage, Device 2 |

|   | 7        | PVDD voltage, Device 2   |

|   | 8        | High-Z                   |

| ٠ | 9        | Output current, Device 3 |

|   | 10       | Output voltage, Device 3 |

|   | 11       | PVDD voltage, Device 3   |

| _ | 12       | High-Z                   |

#### I<sup>2</sup>S AND LEFT JUSTIFIED OPERATING MODE

An I<sup>2</sup>S or left justified output interface can be selected by reversing the pin connections for BCLK and FSYNC; that is, the I<sup>2</sup>S LRCLK is connected to Ball D3 (BCLK\_TDM/PDM\_CLK/LRCLK\_I2S), and the I<sup>2</sup>S BCLK is connected to Ball D2 (FSYNC\_TDM/BCLK\_I2S).

The I<sup>2</sup>S interface requires 64 BCLK cycles per LRCLK cycle. The voltage information is sent when LRCLK is low, and the current information is sent when LRCLK is high. (See the Timing Diagrams, I<sup>2</sup>S and Left Justified Modes section.)

The SLOT pin configures the I<sup>2</sup>S or left justified output as follows (see Table 10).

- Selection of I<sup>2</sup>S or left justified mode.

- Output of PVDD sense information. When PVDD data is output, eight bits are appended to the 16-bit voltage sense data to create a 24-bit output. The 16 MSBs represent the voltage data; the eight LSBs represent the PVDD data.

- Sample rate range. The sample rate ranges from 16 kHz to 48 kHz. A range of 32 kHz to 48 kHz is also allowed in low power I<sup>2</sup>S mode.

Table 10. I<sup>2</sup>S and Left Justified Slot Selection

| Device Setting                                                                     | BCLK Setting                       | SLOT Pin Configuration                |

|------------------------------------------------------------------------------------|------------------------------------|---------------------------------------|

| I <sup>2</sup> S mode at 16 kHz to 48 kHz; voltage and current data only           | $64 \times f_s$                    | Tie to IOVDD                          |

| Left justified mode at 16 kHz to 48 kHz; voltage and current data only             | $64 \times f_s$                    | Open                                  |

| I <sup>2</sup> S mode at 16 kHz to 48 kHz; PVDD data appended to voltage data      | $64 \times f_s$                    | Tie to GND                            |

| Left justified mode at 16 kHz to 48 kHz; PVDD data appended to voltage data        | $64 \times f_s$                    | Tie to IOVDD through a 47 kΩ resistor |

| Low power I <sup>2</sup> S mode at 32 kHz to 48 kHz; voltage and current data only | $32 \times f_s$ or $64 \times f_s$ | Tie to GND through a 47 kΩ resistor   |

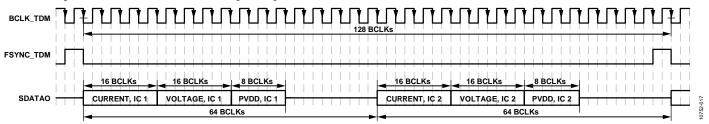

#### MULTICHIP I<sup>2</sup>S OPERATING MODE

A special multichip I<sup>2</sup>S mode is enabled when the part is wired for TDM mode (BCLK and FSYNC not reversed) but the FSYNC signal has a 50% duty cycle. If the FSYNC signal consists of one-clock-cycle pulses, TDM operating mode is active instead.

The multichip  $1^2$ S interface allows multiple chips to drive a single  $1^2$ S bus. Each chip takes control of the bus every two or four frames (depending on the number of chips placed on the bus), allowing a maximum of four chips on the bus. The SLOT pin assignments determine the order of control. (See the Timing Diagrams, Multichip  $1^2$ S Mode section.)

Each frame also contains a 1-bit ID code, which is appended to the current data in the frame. This code indicates the chip that sent the data for that frame. Table 11 provides the mapping of SLOT pin assignments to ID code.

Table 11. Multichip I<sup>2</sup>S Slot Selection

| Chip No. | ID Code | SLOT Pin Configuration                       |

|----------|---------|----------------------------------------------|

| 1        | 0001    | Tie to IOVDD                                 |

| 2        | 0010    | Open                                         |

| 3        | 0100    | Tie to GND                                   |

| 4        | 1000    | Tie to IOVDD through a 47 $k\Omega$ resistor |

The part is automatically configured for two-chip or four-chip operation, depending on the number of chips detected on the bus. The part starts up in four-chip operation, but after it detects that Slot 3 and Slot 4 are unused, the part switches to two-chip operation. For two-chip operation, the first and second slots must be used. If there are three chips on the bus, Slot 1 must be used along with any two other slots.

Table 12 lists the FSYNC and BCLK rates that are supported in multichip I<sup>2</sup>S mode.

Table 12. FSYNC and BCLK Rates in Multichip  $I^2S$  Mode,  $f_s = 16$  kHz to 48 kHz

| Valid Slots | FSYNC Rate          | BCLK Rate                 |

|-------------|---------------------|---------------------------|

| 1 and 2     | $2 \times f_s$      | $128 \times f_s$          |

|             | (32 kHz to 96 kHz)  | (2.048 MHz to 6.144 MHz)  |

| 1, 2, 3, 4  | $4 \times f_s$      | $256 \times f_s$          |

|             | (64 kHz to 128 kHz) | (4.096 MHz to 12.288 MHz) |

#### PDM OUTPUT MODE

By connecting the SLOT pin to GND through a 47  $k\Omega$  resistor, the 1-bit PDM data from the ADCs can be output directly. In PDM mode, a 1 MHz to 6.144 MHz clock must be provided on Ball D3 (BCLK\_TDM/PDM\_CLK/LRCLK\_I2S). PDM data is sent on both edges of the clock and is output on Ball D1 (SDATAO/PDM\_DATA). (See the Timing Diagrams, PDM Mode section.)

In PDM mode, Ball D2 (FSYNC\_TDM/BCLK\_I2S) is used to select the information that is output on the two possible channels (see Table 13).

Table 13. FSYNC\_TDM Pin Settings for PDM Mode

| Output Data                                                  | FSYNC_TDM Pin |

|--------------------------------------------------------------|---------------|

| Current data on rising edge;<br>voltage data on falling edge | Tie to IOVDD  |

| Current data on rising edge;<br>PVDD data on falling edge    | Tie to GND    |

#### **TIMING DIAGRAMS, TDM MODE**

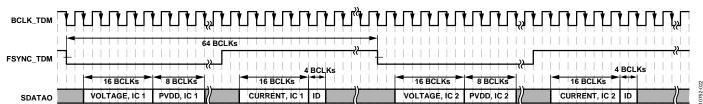

#### TDM Mode, One Device

SLOT pin is tied to IOVDD.

Figure 39. TDM Mode, One Device

#### **TDM Mode, Two Devices**

IC 1: SLOT pin is tied to IOVDD; IC 2: SLOT pin is open.

Figure 40. TDM Mode, Two Devices

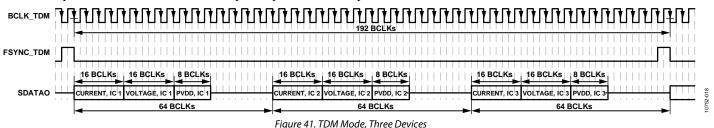

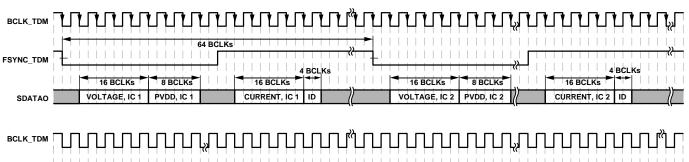

#### **TDM Mode, Three Devices**

IC 1: SLOT pin is tied to IOVDD; IC 2: SLOT pin is open; IC 3: SLOT pin is tied to GND.

#### TIMING DIAGRAMS, I2S AND LEFT JUSTIFIED MODES

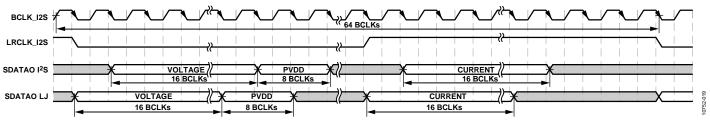

#### $I^2S$ and Left Justified Modes with Voltage, Current, and PVDD Output, $64 \times f_S$

${\rm I^2S}$  output mode: SLOT pin is tied to GND.

Left justified output mode: SLOT pin is tied to IOVDD through a 47 k $\Omega$  resistor.

Figure 42.  $l^2S$  and Left Justified Modes with Voltage, Current, and PVDD Output,  $64 \times f_S$

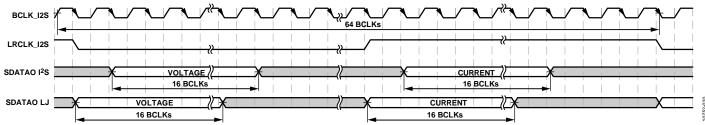

#### $I^2S$ and Left Justified Modes with Voltage and Current Output Only, 64 × $f_S$

I<sup>2</sup>S output mode: SLOT pin is tied to IOVDD (or tied to GND through a 47 kΩ resistor for low power operation at  $64 \times f_s$ ). Left justified output mode: SLOT pin is open.

Figure 43.  $I^2S$  and Left Justified Modes with Voltage and Current Output Only,  $64 \times f_S$

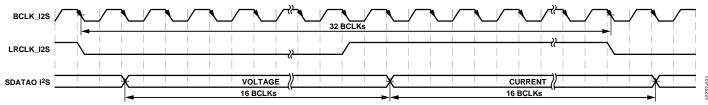

#### $I^2S$ Low Power Mode with Voltage and Current Output Only, $32 \times f_S$

SLOT pin is tied to GND through a 47 k $\Omega$  resistor for low power operation at 32  $\times$  fs.

Figure 44.  $I^2S$  Low Power Mode with Voltage and Current Output Only,  $32 \times f_S$

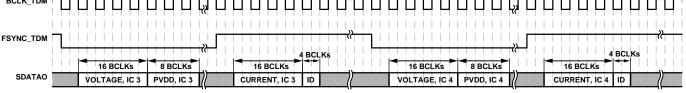

#### TIMING DIAGRAMS, MULTICHIP I2S MODE

#### Multichip I<sup>2</sup>S Mode with Two Devices on the Bus

IC 1: SLOT pin is tied to IOVDD; IC 2: SLOT pin is open.

Figure 45. Multichip I<sup>2</sup>S Mode with Two Devices on the Bus

#### Multichip I<sup>2</sup>S Mode with Three or Four Devices on the Bus

IC 1: SLOT pin is tied to IOVDD; IC 2: SLOT pin is open; IC 3: SLOT pin is tied to GND; IC 4: SLOT pin is tied to IOVDD through a  $47 \text{ k}\Omega$  resistor.

Figure 46. Multichip I<sup>2</sup>S Mode with Three or Four Devices on the Bus

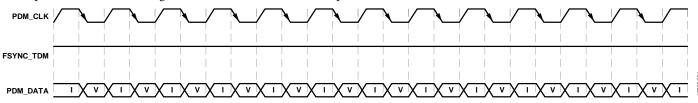

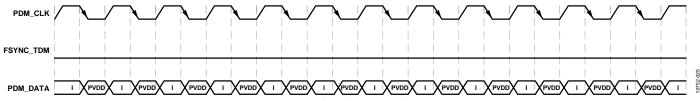

## **TIMING DIAGRAMS, PDM MODE**

#### PDM Mode with Current and Voltage Output

SLOT pin is tied to GND through a 47 k $\Omega$  resistor; FSYNC\_TDM pin is tied to IOVDD.

Figure 47. PDM Mode with Current and Voltage Output

### PDM Mode with Current and PVDD Output

SLOT pin is tied to GND through a 47 k $\!\Omega$  resistor; FSYNC\_TDM pin is tied to GND.

Figure 48. PDM Mode with Current and PVDD Output

# APPLICATIONS INFORMATION LAYOUT

As output power increases, care must be taken to lay out PCB traces and wires properly between the amplifier, load, and power supply. A good practice is to use short, wide PCB tracks to decrease voltage drops and minimize inductance. Ensure that track widths are at least 200 mil for every inch of track length for lowest DCR, and use 1 oz or 2 oz copper PCB traces to further reduce IR drops and inductance. A poor layout increases voltage drops, consequently affecting efficiency. Use large traces for the power supply inputs and amplifier outputs to minimize losses due to parasitic trace resistance.

Proper grounding helps to improve audio performance, minimize crosstalk between channels, and prevent switching noise from coupling into the audio signal. To maintain high output swing and high peak output power, the PCB traces that connect the output pins to the load, as well as the PCB traces to the supply pins, should be as wide as possible to maintain the minimum trace resistances. It is also recommended that a large ground plane be used for minimum impedances.

In addition, good PCB layout isolates critical analog paths from sources of high interference. Separate high frequency circuits (analog and digital) from low frequency circuits.

Properly designed multilayer PCBs can reduce EMI emissions and increase immunity to the RF field by a factor of 10 or more compared with double-sided boards. A multilayer board allows a complete layer to be used for the ground plane, whereas the ground plane side of a double-sided board is often disrupted by signal crossover.

If the system has separate analog and digital ground and power planes, the analog ground plane should be directly beneath the analog power plane, and, similarly, the digital ground plane should be directly beneath the digital power plane. There should be no overlap between the analog and digital ground planes or between the analog and digital power planes.

#### INPUT CAPACITOR SELECTION

The SSM4321 does not require input coupling capacitors if the input signal is biased from 1.0 V to PVDD - 1.0 V. Input capacitors are required if the input signal is not biased within this recommended input dc common-mode voltage range, if high-pass filtering is needed, or if a single-ended source is used. If high-pass filtering is needed at the input, the input capacitor  $(C_{\rm IN})$  and the input impedance of the SSM4321 (80 k $\Omega$ ) form a high-pass filter with a corner frequency determined by the following equation:

$$f_C = 1/(2\pi \times 80 \text{ k}\Omega \times C_{IN})$$

The input capacitor value and the dielectric material can significantly affect the performance of the circuit. Not using input capacitors degrades both the output offset voltage of the amplifier and the dc PSRR performance.

#### **POWER SUPPLY DECOUPLING**

To ensure high efficiency, low total harmonic distortion (THD), and high PSRR, proper power supply decoupling is necessary. Noise transients on the power supply lines are short-duration voltage spikes. These spikes can contain frequency components that extend into the hundreds of megahertz. The power supply input must be decoupled with a good quality, low ESL, low ESR capacitor, with a minimum value of 4.7  $\mu F$ . This capacitor bypasses low frequency noises to the ground plane. For high frequency transient noises, use a 0.1  $\mu F$  capacitor as close as possible to the PVDD pin of the device. Placing the decoupling capacitors as close as possible to the SSM4321 helps to maintain efficient performance.

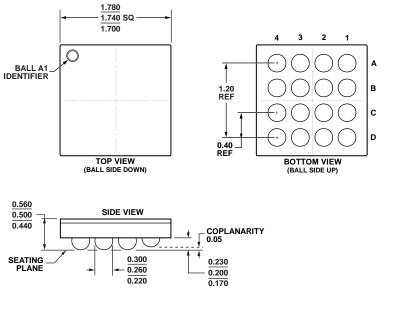

# **OUTLINE DIMENSIONS**

Figure 49. 16-Ball Wafer Level Chip Scale Package [WLCSP] (CB-16-15) Dimensions shown in millimeters

07-13-2011-A

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                            | Package Option <sup>2</sup> | Branding |

|--------------------|-------------------|------------------------------------------------|-----------------------------|----------|

| SSM4321ACBZ-R7     | -40°C to +85°C    | 16-Ball Wafer Level Chip Scale Package [WLCSP] | CB-16-15                    | Y4E      |

| SSM4321ACBZ-RL     | −40°C to +85°C    | 16-Ball Wafer Level Chip Scale Package [WLCSP] | CB-16-15                    | Y4E      |

| EVAL-SSM4321Z      |                   | Evaluation Board                               |                             |          |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

<sup>&</sup>lt;sup>2</sup> This package option is halide free.

# **NOTES**

**NOTES**

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.:

EVAL-SSM4321Z SSM4321ACBZ-R7 SSM4321ACBZ-RL