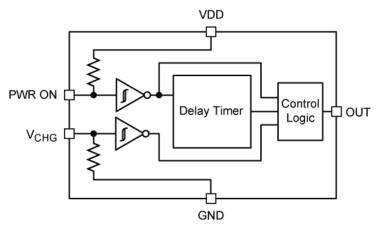

Figure 2. Functional Block Diagram

**Table 1. PIN FUNCTION DESCRIPTION**

| Pin No. | Pin Name         | Description                                                                                              |  |  |

|---------|------------------|----------------------------------------------------------------------------------------------------------|--|--|

| 1       | PWR_ON           | Power ON, CMOS input.                                                                                    |  |  |

| 2       | V <sub>CHG</sub> | Charger IN, CMOS input.                                                                                  |  |  |

| 3       | NIC              | No Internal Connection. A voltage or signal applied to this pin will have no effect on device operation. |  |  |

| 4       | GND              | System Ground.                                                                                           |  |  |

| 5       | OUT              | Drive Output. Active-high push-pull output.                                                              |  |  |

| 6       | VDD              | Positive Power Supply.                                                                                   |  |  |

# **Table 2. ABSOLUTE MAXIMUM RATINGS**

| Rating                                                                            | Symbol              | Value                                                    | Unit |

|-----------------------------------------------------------------------------------|---------------------|----------------------------------------------------------|------|

| Input Voltage Range                                                               | $V_{DD}$            | -0.3 to 6                                                | V    |

| Output Voltage Range                                                              | V <sub>OUT</sub>    | -0.3 to 6 or (V <sub>DD</sub> + 0.3), whichever is lower | V    |

| Input Voltage; PWR_ON, V <sub>CHG</sub>                                           | V <sub>IN</sub>     | -0.3 to 6 or (V <sub>DD</sub> + 0.3), whichever is lower | V    |

| Maximum Junction Temperature                                                      | T <sub>J(max)</sub> | 150                                                      | °C   |

| Output Current; OUT                                                               | l <sub>out</sub>    | 10                                                       | mA   |

| Storage Temperature Range                                                         | T <sub>STG</sub>    | -65 to 150                                               | °C   |

| ESD Capability, Human Body Model (Note 1)                                         | ESD <sub>HBM</sub>  | 2                                                        | kV   |

| ESD Capability, Machine Model (Note 2)                                            | ESD <sub>MM</sub>   | 150                                                      | V    |

| Lead Temperature Soldering<br>Reflow (SMD Styles Only), Pb-Free Versions (Note 2) | T <sub>SLD</sub>    | 260                                                      | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

- This device series incorporates ESD protection and is tested by the following methods:

ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114)

ESD Machine Model tested per AEC-Q100-003 (EIA/JESD22-A115)

- Latch-up Current Maximum Rating: ≤150 mA per JEDEC standard: JESD78

- 2. For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D

**Table 3. RECOMMENDED OPERATING CONDITIONS**

| Rating                                  | Symbol           | Min | Max      | Unit |

|-----------------------------------------|------------------|-----|----------|------|

| Input Voltage; VDD                      | $V_{DD}$         | 1.8 | 5.5      | V    |

| Input Voltage; PWR_ON, V <sub>CHG</sub> | V <sub>IN</sub>  | 0   | $V_{DD}$ | V    |

| Output Current; OUT                     | I <sub>OUT</sub> | 0   | 3        | mA   |

| Ambient Temperature                     | T <sub>A</sub>   | -40 | 85       | °C   |

$\begin{tabular}{ll} \textbf{Table 4. ELECTRICAL OPERATING CHARACTERISTICS} \\ (V_{DD} = 1.8 \ V \ to \ 5.5 \ V. \ For \ typical \ values \ T_A = 25 \ ^\circ C, \ for \ min/max \ values \ T_A = -40 \ ^\circ C \ to \ +85 \ ^\circ C \ unless \ otherwise \ noted.) \\ \end{tabular}$

| Parameter                                                       | Test Conditions                                                                                                                                                                    | Symbol                 | Min                   | Тур  | Max                    | Unit |

|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|------|------------------------|------|

| POWER                                                           |                                                                                                                                                                                    |                        | •                     | •    | •                      |      |

| V <sub>DD</sub> Supply Voltage                                  |                                                                                                                                                                                    | $V_{DD}$               | 1.8                   |      | 5.5                    | V    |

| Quiescent Supply Current                                        | Current PWR_ON = VDD, V <sub>CHG</sub> = 0 V                                                                                                                                       |                        |                       | 100  | 1000                   | nA   |

| Operating Supply Current                                        | PWR_ON = 0 V, $V_{CHG}$ = 0 V Measured during setup period. Measurement includes current through internal 200 k $\Omega$ pull-up resistor on PWR_ON                                |                        |                       |      | 50                     | μΑ   |

| LOGIC INPUTS AND OUTPUTS                                        |                                                                                                                                                                                    |                        |                       |      |                        |      |

| Input Voltage; HIGH                                             | PWR_ON, V <sub>CHG</sub>                                                                                                                                                           | V <sub>IH</sub>        | 0.7 x V <sub>DD</sub> |      |                        | V    |

| Input Voltage; LOW                                              | PWR_ON, V <sub>CHG</sub>                                                                                                                                                           | V <sub>IL</sub>        |                       |      | 0.25 x V <sub>DD</sub> | V    |

| Hysteresis                                                      |                                                                                                                                                                                    | V <sub>HYS</sub>       |                       | 250  |                        | mV   |

| Input Current V <sub>CHG</sub>                                  | V <sub>CHG</sub> = 0 V; V <sub>DD</sub> = 5 V<br>(internal pull-down)                                                                                                              | I <sub>IL1</sub>       |                       | 50   | 300                    | nA   |

| Input Current V <sub>CHG</sub>                                  | V <sub>CHG</sub> = 5 V; V <sub>DD</sub> = 5 V<br>(internal pull-down)                                                                                                              | I <sub>IH1</sub>       |                       | 25   |                        | μΑ   |

| Input Current PWR_ON                                            | PWR_ON = 0 V; $V_{DD}$ = 5 V (internal 200 kΩ pull–up resistor)                                                                                                                    | I <sub>IL2</sub>       |                       | 25   |                        | μΑ   |

| Input Current PWR_ON                                            | PWR_ON = 5 V; $V_{DD}$ = 5 V (internal 200 kΩ pull–up resistor)                                                                                                                    | I <sub>IH2</sub>       |                       | 50   | 300                    | nA   |

| Output Voltage; HIGH                                            | $I_{SOURCE} = -0.1 \text{ mA}, V_{DD} = 1.8 \text{ V}$                                                                                                                             | V <sub>OH</sub>        | V <sub>DD</sub> – 0.2 |      |                        | V    |

| Output Voltage; LOW                                             | I <sub>SINK</sub> = 3 mA, V <sub>DD</sub> = 1.8 V                                                                                                                                  | V <sub>OL</sub>        |                       | 0.1  | 0.4                    | V    |

| TIMING                                                          |                                                                                                                                                                                    |                        |                       |      |                        |      |

| Input Delay PWR_ON                                              | T <sub>A</sub> = 25°C                                                                                                                                                              | t <sub>low_delay</sub> | 6.56                  | 8.00 | 9.44                   | S    |

|                                                                 | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                                                                                                                |                        | 6.00                  |      | 10.00                  |      |

| <b>TEST MODE</b> (V <sub>DD</sub> = 5 V, T <sub>A</sub> = 25°C) | (Note 3)                                                                                                                                                                           |                        |                       |      |                        |      |

| Start TEST Window                                               |                                                                                                                                                                                    | t <sub>ST</sub>        |                       |      | 35                     | μs   |

| Test Mode Delay                                                 | $\begin{array}{c} \text{PWR\_ON} = 0 \text{ V, V}_{CHG} \rightarrow 7 \\ \text{cycles, delay measured after 8th} \\ \text{rising edge of V}_{CHG} \text{ clock pulse} \end{array}$ | t <sub>D</sub>         |                       | 250  |                        | μs   |

| Test Mode Clock Frequency                                       | Clock applied to V <sub>CHG</sub>                                                                                                                                                  | f <sub>tm</sub>        |                       | 1    |                        | MHz  |

| PWR_ON Test Mode Clock Setup Time                               | Measured from PWR_ON falling edge to first falling edge of V <sub>CHG</sub>                                                                                                        | t <sub>P</sub>         | 1                     |      |                        | μs   |

| V <sub>CHG</sub> Input Voltage; LOW                             | V <sub>CHG</sub> , Test Mode Operation                                                                                                                                             | $V_{IL\_TM}$           |                       |      | 0.2 x V <sub>DD</sub>  | V    |

| V <sub>CHG</sub> Pulse Width                                    |                                                                                                                                                                                    | t <sub>pw</sub>        |                       | 500  |                        | ns   |

<sup>3. &</sup>quot;Test Mode" parameters are not tested in production.

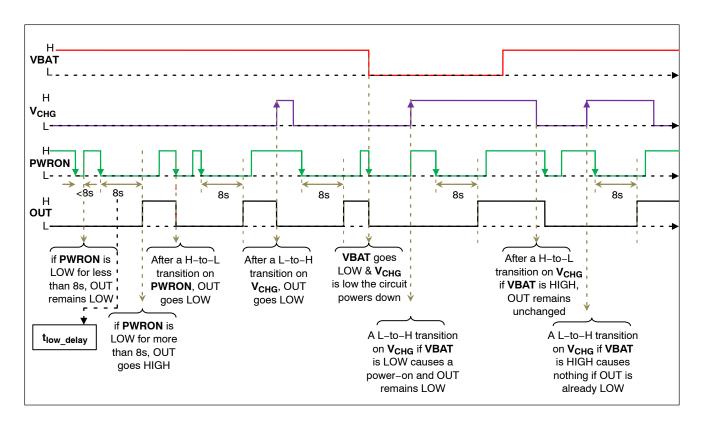

# **TIMING WAVEFORMS**

Figure 3. Timing Waveforms

#### SYSTEM DESCRIPTION AND APPLICATIONS INFORMATION

### General

CAT874 is designed for the manual switching of microprocessors and microcontrollers. To prevent accidental resets, CAT874 requires PWR\_ON input be held low for a prescribed period before an Active high output is issued to the system processor.

# PWR\_ON and V<sub>CHG</sub> Inputs

PWR\_ON and V<sub>CHG</sub> are Schmitt trigger CMOS inputs. PWR\_ON must go low and stay low for a predetermined period (t<sub>LOW\_DELAY</sub>) to generate an Active high on the output.

$V_{CHG}$  is a standard CMOS input with internal pull down resistor 200  $k\Omega$  to keep the input low when charger is not plugged in and PWR\_ON is also a CMOS input with an internal 200  $k\Omega$  pull-up resistor, thus PWR\_ON can be left floating.

When PWR\_ON goes low, an internal timing cycle is initiated. If it goes high before the countdown timer has concluded its cycle, the timer will reset and will restart from the beginning when PWR\_ON returns to being low.

### **Output (OUT)**

CAT874 provides an active-high push pull output. This output will sink up to 3 mA.

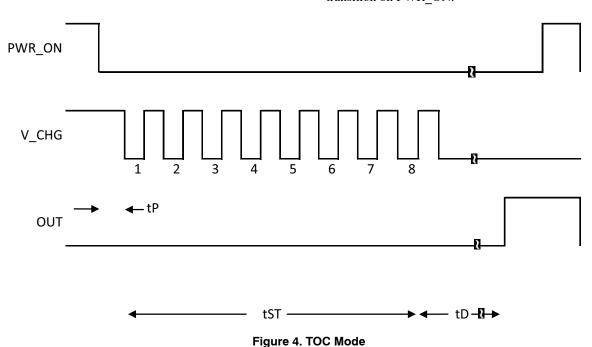

#### **Delay Timer Testing:**

A user test mode is provided to reduce the system test time after the CAT874 is mounted on the board. Instead of waiting  $t_{LOW\ DELAY}$  for the output to go active.

The user brings PWR\_ON low, and sends seven positive edges on the  $V_{CHG}$  pin in a window of time  $t_{ST}$ . After a delay  $t_{D}$ , the device output will change state from low to high, and will return to the low state only when there is a high-to-low transition on PWR\_ON.

### **APPLICATION INFORMATION**

# **Output Operation**

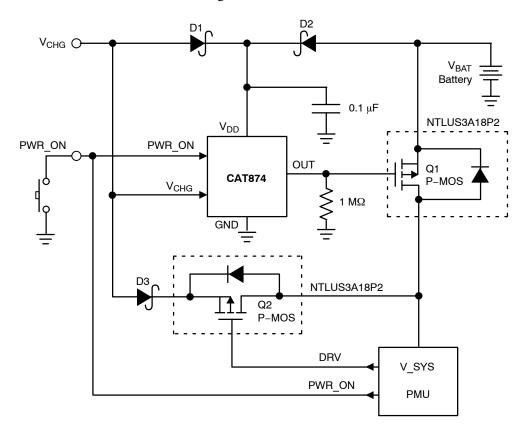

# System with Two Different Power Supply Voltages

When both  $V_{CHG}$  and VBAT are present, the following application can be adapted. Schottky diodes D1 and D2 can be used to isolate the two sources. The higher source will supply the VDD power.

If  $V_{CHG}$  is not present then drop across D2 should be low enough to turn off Q1. If both  $V_{CHG}$  and VBAT are present, the timing waveforms should be used as shown in Figure 4.

An external resistor 1M should be used OUT, to discharge the output when both sources turn off.

# Operation with Low VDD Voltage and Brownout Condition

The CAT874 requires a minimum supply voltage VDD of 1.8 V to guarantee the normal operation within the specification. To prevent small VDD supply glitch, a small ceramic capacitor can be added between the VDD pin and GND.

Figure 5. Application Schematic in Dual Supply System

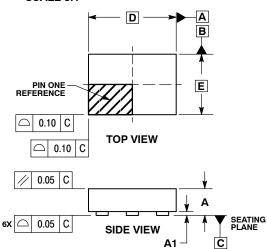

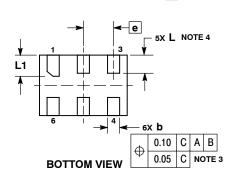

ULLGA6, 1.45x1.0, 0.5P CASE 613AF-01 **ISSUE A**

**DATE 06 FEB 2008**

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994. CONTROLLING DIMENSION: MILLIMETERS.

- DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30 mm FROM THE TERMINAL THE AMAIMUM OF 0.05 PULL BACK OF THE PLATED TERMINAL TROM THE EDGE OF THE PLATED TERMINAL FROM THE EDGE OF THE PLATED TERMINAL FROM THE EDGE OF THE PLATED TERMINAL FROM THE EDGE OF THE

- PACKAGE IS ALLOWED.

|     | MILLIMETERS |      |  |  |

|-----|-------------|------|--|--|

| DIM | MIN         | MAX  |  |  |

| Α   |             | 0.40 |  |  |

| A1  | 0.00        | 0.05 |  |  |

| b   | 0.15        | 0.25 |  |  |

| D   | 1.45 BSC    |      |  |  |

| Е   | 1.00 BSC    |      |  |  |

| е   | 0.50 BSC    |      |  |  |

| L   | 0.25        | 0.35 |  |  |

| L1  | 0.30        | 0.40 |  |  |

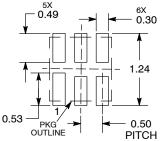

#### **MOUNTING FOOTPRINT SOLDERMASK DEFINED\***

DIMENSIONS: MILLIMETERS

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER: | 98AON24011D            | Electronic versions are uncontrolled except when accessed directly from the Document Reposit Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | ULLGA6, 1.45X1.0, 0.5P |                                                                                                                                                                              | PAGE 1 OF 1 |  |

ON Semiconductor and (III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer pu

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT: Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

onsemi

CAT874-80ULGT3