## **ABSOLUTE MAXIMUM RATINGS**

| VCCTXPA, VCCPA and TXRF_ to GND0.3V to +4.5V           |

|--------------------------------------------------------|

| VCCLNA, VCCTXMX, VCCPLL, VCCCP, VCCXTAL, VCCVCO,       |

| VCCRXVGA, VCCRXFL, and VCCRXMX_ to GND0.3V to +3.9V    |

| B6, B7, B3, B2, SHDN, B5, CS, SCLK, DIN, B1, TUNE, B4, |

| TXBBI_, TXBBQ_, RXHP, RXTX, RXBBI_, RXBBQ_, RSSI,      |

| BYPASS, CPOUT, LD, CLOCKOUT, XTAL, CTUNE, RXRF_ to     |

| GND0.3V to (Operating V <sub>CC</sub> + 0.3V)          |

| RXBBI_, RXBBQ_, RSSI, BYPASS, CPOUT, LD, CLOCKOUT      |

| Short-Circuit Duration10s                              |

| RF Input Power                                        | +10dBm  |

|-------------------------------------------------------|---------|

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |         |

| 48-Pin TQFN (derates 27.8mW/°C above +70°C)           | 2.22W   |

| Operating Temperature Range40°C t                     | o +85°C |

| Junction Temperature                                  | .+150°C |

| Storage Temperature Range65°C to                      | +160°C  |

| Lead Temperature (soldering, 10s)                     | .+300°C |

| Soldering Temperature (reflow)                        | .+260°C |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**CAUTION!** ESD SENSITIVE DEVICE

## DC ELECTRICAL CHARACTERISTICS

(MAX2831 EV kit: V<sub>CC</sub> = 2.7V to 3.6V, V<sub>CCPA</sub> = V<sub>CCTXPA</sub> = 2.7V to 4.2V, T<sub>A</sub> = -40°C to +85°C, Rx set to the maximum gain.  $\overline{CS}$  = high, RXHP = SCLK = DIN = low, RSSI and clock output buffer are off, no signal at RF inputs, all RF inputs and outputs terminated into 50 $\Omega$ , receiver baseband outputs are open. 100mV<sub>RMS</sub> differential I and Q signals (54Mbps IEEE 802.11g OFDM) applied to I/Q baseband inputs of transmitter in transmit mode, f<sub>REF</sub> = 40MHz, and registers set to recommended settings and corresponding test mode, unless otherwise noted. Typical values are at V<sub>CC</sub> = 2.8V, V<sub>CCPA</sub> = 3.3V, and T<sub>A</sub> = +25°C, LO frequency = 2.437GHz, unless otherwise noted. RF inputs/outputs specifications are referenced to device pins and do not include 1dB loss from EV kit PCB, balun, and SMA connectors.) (Note 1)

| PARAMETERS                                                | CONDITIONS                                                                                    |                                               |      | ТҮР | MAX  | UNITS |

|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------|------|-----|------|-------|

| Supply Voltage                                            | V <sub>CC</sub> _                                                                             |                                               | 2.7  |     | 3.6  | V     |

|                                                           | VCCPA, VCCTXPA                                                                                |                                               | 2.7  |     | 4.2  | v     |

| Supply Current                                            | Shutdown mode,<br>B7: B1 = 0000000,<br>reference oscillator not<br>applied                    | $T_A = +25^{\circ}C$                          |      | 20  |      | μA    |

|                                                           | Standby made                                                                                  | $T_A = +25^{\circ}C$                          |      | 28  | 35   |       |

|                                                           | Standby mode                                                                                  | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |      |     | 35   |       |

|                                                           | Rx mode                                                                                       | $T_A = +25^{\circ}C$                          |      | 62  | 78   |       |

|                                                           |                                                                                               | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |      |     | 82   |       |

|                                                           | Tx mode, $T_A = +25^{\circ}C$ ,<br>V <sub>CC</sub> = 2.8V, V <sub>CCPA</sub> = 3.3V, (Note 2) | MAX2831, transmit section                     |      | 82  | 104  | mA    |

|                                                           |                                                                                               | MAX2831, PA, P <sub>OUT</sub> = +18.2dBm      |      | 209 | 258  |       |

|                                                           |                                                                                               | MAX2832                                       |      | 86  |      |       |

|                                                           | Rx calibration mode                                                                           | $T_A = +25^{\circ}C$                          |      | 101 |      |       |

|                                                           | Tx calibration mode                                                                           | $T_A = +25^{\circ}C$                          |      | 78  |      |       |

| Rx I/Q Output Common-Mode<br>Voltage                      | $T_A = +25^{\circ}C$ at default c                                                             | ommon-mode setting                            | 0.98 | 1.2 | 1.33 | V     |

| Rx I/Q Output Common-Mode                                 | $T_A = -40^{\circ}C$ (relative to T                                                           | Γ <sub>A</sub> = +25°C)                       |      | -17 |      | mV    |

| Voltage Variation                                         | $T_A = +85^{\circ}C$ (relative to $T_A = +25^{\circ}C$ )                                      |                                               |      | 15  |      | IIIV  |

| Tx Baseband Input Common-<br>Mode Voltage Operating Range | DC-coupled                                                                                    |                                               | 0.9  |     | 1.3  | V     |

| Tx Baseband Input Bias Current                            | Source current                                                                                |                                               |      |     | 22   | μA    |

## DC ELECTRICAL CHARACTERISTICS (continued)

(MAX2831 EV kit:  $V_{CC_{-}} = 2.7V$  to 3.6V,  $V_{CCPA} = V_{CCTXPA} = 2.7V$  to 4.2V,  $T_A = -40^{\circ}$ C to +85°C, Rx set to the maximum gain.  $\overline{CS} =$  high, RXHP = SCLK = DIN = low, RSSI and clock output buffer are off, no signal at RF inputs, all RF inputs and outputs terminated into 50 $\Omega$ , receiver baseband outputs are open. 100mVRMs differential I and Q signals (54Mbps IEEE 802.11g OFDM) applied to I/Q baseband inputs of transmitter in transmit mode, f<sub>REF</sub> = 40MHz, and registers set to recommended settings and corresponding test mode, unless otherwise noted. Typical values are at V<sub>CC</sub> = 2.8V, V<sub>CCPA</sub> = 3.3V, and T<sub>A</sub> = +25°C, LO frequency = 2.437GHz, unless otherwise noted. RF inputs/outputs specifications are referenced to device pins and do not include 1dB loss from EV kit PCB, balun, and SMA connectors.) (Note 1)

| PARAMETERS                                           | CONDITIONS     | MIN                      | ТҮР | МАХ | UNITS |  |  |  |  |  |

|------------------------------------------------------|----------------|--------------------------|-----|-----|-------|--|--|--|--|--|

| LOGIC INPUTS: SHDN, RXTX, SCLK, DIN, CS, B7:B1, RXHP |                |                          |     |     |       |  |  |  |  |  |

| Digital Input-Voltage High, VIH                      |                | V <sub>CC</sub> -<br>0.4 |     |     | V     |  |  |  |  |  |

| Digital Input-Voltage Low, VIL                       |                |                          |     | 0.4 | V     |  |  |  |  |  |

| Digital Input-Current High, IIH                      |                | -1                       |     | +1  | μA    |  |  |  |  |  |

| Digital Input-Current Low, IIL                       |                | -1                       |     | +1  | μA    |  |  |  |  |  |

| LOGIC OUTPUTS: LD, CLOCKOU                           | TL             |                          |     |     |       |  |  |  |  |  |

| Digital Output-Voltage High, V <sub>OH</sub>         | Sourcing 100µA | V <sub>CC</sub> -<br>0.4 |     |     | V     |  |  |  |  |  |

| Digital Output-Voltage Low, VOL                      | Sinking 100µA  |                          |     | 0.4 | V     |  |  |  |  |  |

## AC ELECTRICAL CHARACTERISTICS-Rx Mode

(MAX2831 EV kit:  $V_{CC_{-}} = 2.8V$ ,  $V_{CCPA} = V_{CCTXPA} = 3.3V$ ,  $T_A = +25^{\circ}C$ ,  $f_{RF} = 2.439$ GHz,  $f_{LO} = 2.437$ GHz; receiver baseband I/Q outputs at 112 mV<sub>RMS</sub> (-19dBV),  $f_{REF} = 40$ MHz,  $\overline{SHDN} = \overline{CS} =$  high, RXTX = SCLK = DIN = low, with power matching for the differential RF pins using the typical applications and registers set to default settings and corresponding test mode, unless otherwise noted. Unmodulated single-tone RF input signal is used with specifications which normally apply over the entire operating conditions, unless otherwise indicated. RF inputs/outputs specifications are referenced to device pins and do not include 1dB loss from EV kit PCB, balun, and SMA connectors.) (Note 1)

| PARAMETER                          | CONDITIONS                                                                             |                                               |     | ТҮР | МАХ | UNITS |

|------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------|-----|-----|-----|-------|

| <b>RECEIVER SECTION: LNA RF II</b> | JTPUTS                                                                                 |                                               |     |     |     |       |

| RF Input Frequency Range           |                                                                                        |                                               | 2.4 |     | 2.5 | GHz   |

|                                    | High RF gain                                                                           |                                               |     | 18  |     |       |

| RF Input Return Loss               | Mid RF gain                                                                            |                                               |     | 11  |     | dB    |

|                                    | Low RF gain                                                                            |                                               |     | 14  |     |       |

| Total Voltage Gain                 | Maximum gain, B7:B1 =                                                                  | $T_A = +25^{\circ}C$                          | 86  | 98  |     |       |

|                                    | 1111111                                                                                | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ | 83  |     |     | -10   |

|                                    | Minimum gain, B7:B1 = 0000000                                                          | $T_A = +25^{\circ}C$                          |     | 3   | 8   | dB    |

|                                    | From high-gain mode (B7:E<br>mode (B7:B6 = 10)                                         | 6 = 11) to medium-gain                        |     | -16 |     | -10   |

| RF Gain Steps (Note 3)             | From high-gain mode (B7:B6 = 11) to low-gain mode<br>(B7:B6 = 0X)                      |                                               |     | -33 |     | dB    |

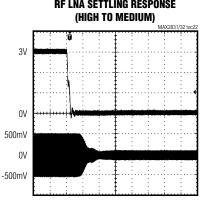

| RF Gain-Change Settling Time       | Gain change from high gair<br>low, or medium gain to low<br>±2dB of steady state; RXHF | 0 10 0                                        |     | 0.2 |     | μs    |

## AC ELECTRICAL CHARACTERISTICS—Rx Mode (continued)

(MAX2831 EV kit:  $V_{CC_{-}} = 2.8V$ ,  $V_{CCPA} = V_{CCTXPA} = 3.3V$ ,  $T_A = +25^{\circ}C$ ,  $f_{RF} = 2.439$ GHz,  $f_{LO} = 2.437$ GHz; receiver baseband I/Q outputs at 112 mV<sub>RMS</sub> (-19dBV),  $f_{REF} = 40$ MHz,  $\overline{SHDN} = \overline{CS} = high$ , RXTX = SCLK = DIN = low, with power matching for the differential RF pins using the typical applications and registers set to default settings and corresponding test mode, unless otherwise noted. Unmodulated single-tone RF input signal is used with specifications which normally apply over the entire operating conditions, unless otherwise indicated. RF inputs/outputs specifications are referenced to device pins and do not include 1dB loss from EV kit PCB, balun, and SMA connectors.) (Note 1)

| PARAMETER                                                                                           | CONI                                                                                   | MIN                                                                                                                                                                                                                                | ТҮР   | МАХ  | UNITS   |                   |  |

|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|---------|-------------------|--|

| Baseband Gain Range                                                                                 | From maximum baseband gain (B5:B1 = 11111) to<br>minimum baseband gain (B5:B1 = 00000) |                                                                                                                                                                                                                                    |       | 62   | 67      | dB                |  |

|                                                                                                     | Voltage gain = maximum w                                                               | ith B7:B6 = 11                                                                                                                                                                                                                     |       | 2.6  |         |                   |  |

|                                                                                                     | Voltage gain = 50dB with B                                                             | 7:B6 = 11                                                                                                                                                                                                                          |       | 3.2  |         |                   |  |

| DSB Noise Figure                                                                                    | Voltage gain = 45dB with B                                                             | 7:B6 = 10                                                                                                                                                                                                                          |       | 16   |         | dB                |  |

|                                                                                                     | Voltage gain = 15dB with B                                                             | oltage gain = 15dB with B7:B6 = 0X                                                                                                                                                                                                 |       | 34   |         |                   |  |

|                                                                                                     | -19dBV <sub>RMS</sub> baseband                                                         | B7:B6 = 11                                                                                                                                                                                                                         |       | -41  |         |                   |  |

| In-Band Compression Point<br>Based on EVM                                                           | output EVM degrades to                                                                 | B7:B6 = 10                                                                                                                                                                                                                         |       | -24  |         | dBm               |  |

| Dased on Evin                                                                                       | 9%                                                                                     | B7:B6 = 0X                                                                                                                                                                                                                         |       | -6   |         |                   |  |

| In-Band Output P-1dB                                                                                | Voltage gain = 90dB, with E                                                            | 37:B6 = 11                                                                                                                                                                                                                         |       | 2.5  |         | VP-P              |  |

|                                                                                                     | B7:B6 = 11                                                                             |                                                                                                                                                                                                                                    |       | -12  |         |                   |  |

| Out-of-Band Input IP3 (Note 4)                                                                      | B7:B6 = 10                                                                             |                                                                                                                                                                                                                                    |       | -4   |         | dBm               |  |

|                                                                                                     | B7:B6 = 0X                                                                             | 7:B6 = 0X                                                                                                                                                                                                                          |       |      |         | 1                 |  |

| I/Q Phase Error                                                                                     | $1\sigma$ variation (without calibra                                                   |                                                                                                                                                                                                                                    | ±0.35 |      | Degrees |                   |  |

| I/Q Gain Imbalance                                                                                  | $1\sigma$ variation (without calibra                                                   | tion)                                                                                                                                                                                                                              | ±0.1  |      |         | dB                |  |

| RX I/Q Output Load Impedance                                                                        | Minimum differential resista                                                           | nce                                                                                                                                                                                                                                |       | 10   |         | kΩ                |  |

| (R II C)                                                                                            | Maximum differential capac                                                             | tance                                                                                                                                                                                                                              | 10    |      |         | рF                |  |

| Tx-to-Rx Conversion Gain for Rx<br>I/Q Calibration                                                  | For receiver gain, B7:B1 =                                                             | For receiver gain, B7:B1 = 1101111 (Note 5)                                                                                                                                                                                        |       |      |         | dB                |  |

| Baseband VGA Settling Time                                                                          | Gain change from B5:B1 = settling to within ±2dB of sto                                | 10111 to B5:B1 = 00111; gain<br>eady state                                                                                                                                                                                         |       | 0.1  |         | μs                |  |

| I/Q Output DC Step when RXHP<br>Transitions from 1 to 0 in<br>Presence of 802.11g Short<br>Sequence | ideal short sequence data a channel, for -19dBV output;                                | After switching RXHP to logic 0 from initial logic 1, during ideal short sequence data at -55dBm input in AWGN channel, for -19dBV output; normalized to RMS signal on I and Q outputs; transition point varied from 0 to 0.8µs in |       |      |         | dBc               |  |

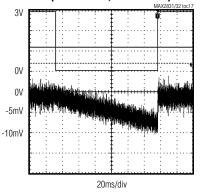

| I/Q Output DC Droop                                                                                 | After switching RXHP to 0, [<br>(A3:A0 = 0111)                                         | D13:D12, Register 7                                                                                                                                                                                                                |       | ±1   |         | V/s               |  |

| I/Q Static DC Offset                                                                                | RXHP = 1, B7:B1 = 110111                                                               | ±1                                                                                                                                                                                                                                 |       |      | mV      |                   |  |

| Spurious Signal Emissions from<br>LNA input                                                         | RF = 1GHz to 26.5GHz                                                                   |                                                                                                                                                                                                                                    | -51   |      | dBm     |                   |  |

| RECEIVER BASEBAND FILTER                                                                            | S                                                                                      |                                                                                                                                                                                                                                    |       |      |         | ·                 |  |

| Gain Ripple in Passband                                                                             | 10kHz to 8.5MHz at baseba                                                              | and                                                                                                                                                                                                                                |       | ±1.3 |         | DB <sub>P-P</sub> |  |

| Group-Delay Ripple in Passband                                                                      | 10kHz to 8.5MHz at baseba                                                              | and                                                                                                                                                                                                                                |       | ±45  |         | NSP-P             |  |

## AC ELECTRICAL CHARACTERISTICS-Rx Mode (continued)

(MAX2831 EV kit:  $V_{CC_{-}} = 2.8V$ ,  $V_{CCPA} = V_{CCTXPA} = 3.3V$ ,  $T_A = +25^{\circ}C$ ,  $f_{RF} = 2.439$ GHz,  $f_{LO} = 2.437$ GHz; receiver baseband I/Q outputs at 112 mV<sub>RMS</sub> (-19dBV),  $f_{REF} = 40$ MHz,  $\overline{SHDN} = \overline{CS} =$  high, RXTX = SCLK = DIN = low, with power matching for the differential RF pins using the typical applications and registers set to default settings and corresponding test mode, unless otherwise noted. Unmodulated single-tone RF input signal is used with specifications which normally apply over the entire operating conditions, unless otherwise indicated. RF inputs/outputs specifications are referenced to device pins and do not include 1dB loss from EV kit PCB, balun, and SMA connectors.) (Note 1)

| PARAMETER                   | CONDITIONS                               |                   |     | TYP | MAX | UNITS |

|-----------------------------|------------------------------------------|-------------------|-----|-----|-----|-------|

|                             | At 8.5MHz                                |                   |     | 3.2 |     |       |

| Baseband Filter Rejection   | At 15MHz                                 |                   |     | 27  |     |       |

| (Nominal Mode)              | At 20MHz                                 |                   |     | 50  |     | dB    |

|                             | At > 40MHz                               | At > 40MHz        |     |     |     |       |

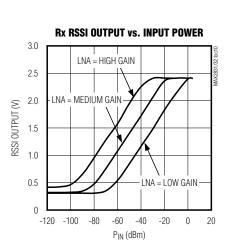

| RSSI                        |                                          |                   |     |     |     |       |

| RSSI Minimum Output Voltage | $R_{LOAD} \ge 10 k\Omega \parallel 5 pF$ |                   |     | 0.4 |     | V     |

| RSSI Maximum Output Voltage | $R_{LOAD} \ge 10 k\Omega \parallel 5 pF$ |                   |     | 2.4 |     | V     |

| RSSI Slope                  |                                          |                   |     | 30  |     | mV/dB |

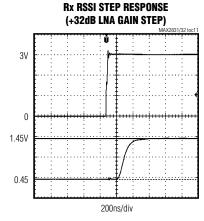

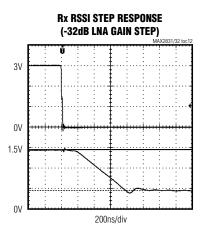

|                             | To within 3dB of steady                  | +32dB signal step | 200 |     |     |       |

| RSSI Output Settling Time   | state                                    | -32dB signal step |     | 600 |     | ns    |

## AC ELECTRICAL CHARACTERISTICS-Tx Mode

(MAX2831 EV kit:  $V_{CC_{-}} = 2.8V$ ,  $V_{CCPA} = V_{CCTXPA} = 3.3V$ ,  $T_A = +25^{\circ}C$ ,  $f_{RF} = 2.439GHz$ ,  $f_{LO} = 2.437GHz$ .  $f_{REF} = 40MHz$ ,  $\overline{SHDN} = RXTX = \overline{CS} = high$ , and SCLK = DIN = low, with power matching for the differential RF pins using the typical applications circuit. 100mV<sub>RMS</sub> sine and cosine signal (or 100mV<sub>RMS</sub> 54Mbps IEEE 802.11g I/Q signals wherever OFDM is mentioned) applied to baseband I/Q inputs of transmitter (differential DC-coupled). Registers set to recommend settings and corresponding test mode, unless otherwise noted. RF inputs/outputs specifications are referenced to device pins and do not include 1dB loss from EV kit PCB, balun, and SMA connectors.) (Note 1)

| PARAMETER                                          | CONDITIONS                   |                                                                         |                          |                                                                 |     | ТҮР   | MAX | UNITS       |

|----------------------------------------------------|------------------------------|-------------------------------------------------------------------------|--------------------------|-----------------------------------------------------------------|-----|-------|-----|-------------|

| TRANSMIT SECTION: Tx BASE                          | BAND I/Q INF                 | UTS TO                                                                  | RF OUTPUT                | S                                                               |     |       |     |             |

| RF Output Frequency Range                          |                              |                                                                         |                          |                                                                 | 2.4 |       | 2.5 | GHz         |

|                                                    |                              | 54Mbps 802.11g to meet 5.6% EV                                          |                          | Output power adjusted<br>to meet 5.6% EVM,<br>and spectral mask |     | 18.5  |     |             |

|                                                    |                              |                                                                         |                          | B6:B1 = 000000                                                  |     | -7.5  |     |             |

| Output Power                                       | MAX2831                      | 802.11b signal,<br>141mV <sub>RMS</sub> ,<br>IEEE802.11b I/Q<br>signals |                          | Output power adjusted to meet spectral mask                     |     | 21    |     | dBm         |

|                                                    |                              | -3dB VG                                                                 | A back off               |                                                                 |     | -5.3  |     |             |

|                                                    | MAX2832                      | B6:B1 =                                                                 | 000000                   |                                                                 |     | -31.5 |     |             |

| Unwanted Sideband Suppression                      | Without I/Q                  | calibratio                                                              | on, B6:B1 = <sup>-</sup> | 100001                                                          |     | -42   |     | dBc         |

| Carrier Leakage at Center<br>Frequency of Channel  | Without DC offset correction |                                                                         |                          |                                                                 |     | -30   |     | dBc         |

|                                                    |                              | 1/3 x f <sub>LO</sub><br>< 1GHz<br>> 1GHz<br>2/3 x f <sub>LO</sub>      |                          |                                                                 | -67 |       |     |             |

|                                                    |                              |                                                                         |                          |                                                                 |     | -36   |     |             |

|                                                    |                              |                                                                         |                          |                                                                 |     | -47   |     | 1           |

|                                                    |                              |                                                                         |                          | 2/3 x fLO                                                       |     | -64   |     |             |

| Transmitter Spurious Signal<br>Emissions (MAX2831) | B6:B1 = 11<br>OFDM sign      |                                                                         | 4/3 x f <sub>LO</sub>    |                                                                 |     | -42   |     | dBm/<br>MHz |

|                                                    | Of Divi sign                 | a                                                                       | 5/3 x f <sub>LO</sub>    |                                                                 |     | -65   |     |             |

|                                                    |                              |                                                                         | 8/3 x f <sub>LO</sub>    |                                                                 |     | -51   |     | 1           |

|                                                    |                              |                                                                         | 2 x f <sub>LO</sub>      |                                                                 |     | -33   |     |             |

|                                                    |                              |                                                                         | 3 x f <sub>LO</sub>      |                                                                 |     | -54   |     |             |

|                                                    |                              |                                                                         | 1/3 x f <sub>LO</sub>    |                                                                 |     | -78   |     |             |

|                                                    |                              |                                                                         | < 1GHz                   |                                                                 |     | -65   |     |             |

|                                                    |                              |                                                                         | > 1GHz                   |                                                                 |     | -72   |     |             |

|                                                    |                              |                                                                         | 2/3 x f <sub>LO</sub>    |                                                                 |     | -78   |     | ĺ           |

| Transmitter Spurious Signal<br>Emissions (MAX2832) | B6:B1 = 11                   |                                                                         | 4/3 x f <sub>LO</sub>    |                                                                 |     | -46   |     | dBm/<br>MHz |

|                                                    |                              | OFDM signal                                                             |                          |                                                                 |     | -72   |     |             |

|                                                    |                              |                                                                         |                          |                                                                 |     | -46   |     |             |

|                                                    |                              |                                                                         | 2 x f <sub>LO</sub>      |                                                                 |     | -60   |     | ]           |

|                                                    |                              |                                                                         | 3 x f <sub>LO</sub>      |                                                                 |     | -75   |     |             |

## AC ELECTRICAL CHARACTERISTICS—Tx Mode (continued)

(MAX2831 EV kit:  $V_{CC_{-}} = 2.8V$ ,  $V_{CCPA} = V_{CCTXPA} = 3.3V$ ,  $T_A = +25^{\circ}C$ ,  $f_{RF} = 2.439GHz$ ,  $f_{LO} = 2.437GHz$ .  $f_{REF} = 40MHz$ ,  $\overline{SHDN} = RXTX = \overline{CS} = high$ , and SCLK = DIN = low, with power matching for the differential RF pins using the typical applications circuit. 100mV<sub>RMS</sub> sine and cosine signal (or 100mV<sub>RMS</sub> 54Mbps IEEE 802.11g I/Q signals wherever OFDM is mentioned) applied to baseband I/Q inputs of transmitter (differential DC-coupled). Registers set to recommend settings and corresponding test mode, unless otherwise noted. RF inputs/outputs specifications are referenced to device pins and do not include 1dB loss from EV kit PCB, balun, and SMA connectors.) (Note 1)

| Off-chip balun + match, single-<br>ended              | MAX2831                                                                                                                                                                             | -2                                                                                                                                                                                 | 0                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                       | 1443/0000                                                                                                                                                                           |                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                  | -10                                                                                                                                                                                                                                                                        |

|                                                       | MAX2832                                                                                                                                                                             | -1                                                                                                                                                                                 | 0                                                                                                                                                                                                                                                  | dB                                                                                                                                                                                                                                                                         |

| Minimum differential resistance                       |                                                                                                                                                                                     | 2                                                                                                                                                                                  | C                                                                                                                                                                                                                                                  | kΩ                                                                                                                                                                                                                                                                         |

| Maximum differential capacitance                      |                                                                                                                                                                                     | 0.                                                                                                                                                                                 | 7                                                                                                                                                                                                                                                  | pF                                                                                                                                                                                                                                                                         |

| D1:D0 = 01, Register 8<br>(A3:A0 = 1000) Nominal mode |                                                                                                                                                                                     | 11                                                                                                                                                                                 |                                                                                                                                                                                                                                                    | MHz                                                                                                                                                                                                                                                                        |

| At 30MHz, in nominal mode                             |                                                                                                                                                                                     | 6                                                                                                                                                                                  | dB                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                            |

| Short sequence transmitter power =                    | 0.                                                                                                                                                                                  | 3                                                                                                                                                                                  | V                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                            |

| Short sequence transmitter power =                    | 1.                                                                                                                                                                                  | 2                                                                                                                                                                                  | V                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                            |

|                                                       |                                                                                                                                                                                     | 0.                                                                                                                                                                                 | 3                                                                                                                                                                                                                                                  | μs                                                                                                                                                                                                                                                                         |

| D I/Q CALIBRATION USING LO LE                         | AKAGE AND SIDEBA                                                                                                                                                                    | ND DETECTO                                                                                                                                                                         | R (see the <i>T</i>                                                                                                                                                                                                                                | ¢∕Rx                                                                                                                                                                                                                                                                       |

| [                                                     | D1:D0 = 01, Register 8<br>(A3:A0 = 1000)<br>At 30MHz, in nominal mode<br>Short sequence transmitter power =<br>Short sequence transmitter power =<br>D I/Q CALIBRATION USING LO LEA | D1:D0 = 01, Register 8 Nominal mode   (A3:A0 = 1000) Nominal mode   At 30MHz, in nominal mode Short sequence transmitter power = +9dBm   Short sequence transmitter power = +19dBm | D1:D0 = 01, Register 8 Nominal mode 1   (A3:A0 = 1000) At 30MHz, in nominal mode 66   Short sequence transmitter power = +9dBm 0.   Short sequence transmitter power = +19dBm 1.   0. 0.   D1/Q CALIBRATION USING LO LEAKAGE AND SIDEBAND DETECTOR | D1:D0 = 01, Register 8 Nominal mode 11   (A3:A0 = 1000) 62   At 30MHz, in nominal mode 62   Short sequence transmitter power = +9dBm 0.3   Short sequence transmitter power = +19dBm 1.2   0.3 0.3   D I/Q CALIBRATION USING LO LEAKAGE AND SIDEBAND DETECTOR (see the Tx) |

| Tx BASEBAND I/Q INPUTS TO F                | ECEIVER OUTPUTS                        |                                                                                                                  |     |                      |

|--------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------|-----|----------------------|

| LO Leakage and Sideband<br>Detector Output | Calibration register,<br>D12:D11 = 00, | Output at 1 x f <sub>TONE</sub><br>(for LO leakage = -29dBc),<br>f <sub>TONE</sub> = 2MHz, 100mV <sub>RMS</sub>  | -34 | - dBV <sub>RMS</sub> |

|                                            | A3:A0 = 0110                           | Output at 2 x f <sub>TONE</sub><br>(for LO leakage = -240dBc),<br>f <sub>TONE</sub> = 2MHz, 100mV <sub>RMS</sub> | -44 | UDVRMS               |

| Amplifier Gain Range                       | D12:D11 = 00 to D12:                   | D12:D11 = 00 to D12:D11 = 11, A3:A0 = 0110                                                                       |     | dB                   |

| Lower -3dB Corner Frequency                |                                        |                                                                                                                  | 1   | MHz                  |

## AC ELECTRICAL CHARACTERISTICS—Frequency Synthesis

(MAX2831 EV kit:  $V_{CC_}$  = 2.7V,  $V_{CCPA}$  =  $V_{CCTXPA}$  = 3.3V,  $T_A$  = +25°C,  $f_{LO}$  = 2.437GHz,  $f_{REF}$  = 40MHz,  $\overline{SHDN}$  =  $\overline{CS}$  = high, SCLK = DIN = low, PLL loop bandwidth = 150kHz, and  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                                 | CONDIT                                                 | IONS                    | MIN  | ТҮР     | MAX               | UNITS   |  |

|-----------------------------------------------------------|--------------------------------------------------------|-------------------------|------|---------|-------------------|---------|--|

| FREQUENCY SYNTHESIZER                                     |                                                        |                         |      |         |                   |         |  |

| RF Channel Center Frequency                               |                                                        | 2.4                     |      | 2.5     | GHz               |         |  |

| Channel Center Frequency<br>Programming Minimum Step Size |                                                        |                         | 20   |         | Hz                |         |  |

| Charge-Pump Comparison<br>Frequency                       |                                                        |                         | 20   |         | MHz               |         |  |

| Reference Frequency Range                                 |                                                        |                         |      |         |                   | MHz     |  |

| Reference Frequency Input<br>Levels                       | AC-coupled to XTAL pin                                 | 800                     |      |         | mV <sub>P-P</sub> |         |  |

| Reference Frequency Input                                 | Resistance (XTAL)                                      |                         | 5    |         | kΩ                |         |  |

| Impedance (R II C)                                        | Capacitance (XTAL)                                     |                         |      | 4       |                   | pF      |  |

|                                                           | foffset = 1kHz                                         |                         | -86  |         |                   |         |  |

|                                                           | foffset = 10kHz                                        |                         | -94  |         |                   |         |  |

| Closed-Loop Phase Noise                                   | foffset = 100kHz                                       |                         | -94  |         | dBc/Hz            |         |  |

|                                                           | f <sub>OFFSET</sub> = 1MHz                             |                         |      | -110    |                   |         |  |

|                                                           | foffset = 10MHz                                        |                         | -120 |         |                   |         |  |

| Closed-Loop Integrated Phase<br>Noise                     | RMS phase jitter; integrate from                       | n 10kHz to 10MHz offset |      | 0.9     |                   | Degrees |  |

| Charge-Pump Output Current                                |                                                        |                         |      | 1       |                   | mA      |  |

| Reference Spurs                                           | 20MHz offset                                           |                         |      | -55     |                   | dBc     |  |

| VCO Frequency Error                                       | Measured from Tx-Rx or Rx-Tx transition                | 3µs to 9µs<br>> 9µs     |      | 50<br>1 |                   | kHz     |  |

| VOLTAGE-CONTROLLED OSCI                                   | LATOR                                                  | · ·                     |      |         |                   |         |  |

| Pushing                                                   | Referred to 2400MHz LO, V <sub>CC</sub> varies by 0.3V |                         |      | 210     |                   | kHz     |  |

| VCO Tuning Voltage Range                                  |                                                        |                         | 0.5  |         | 2.2               | V       |  |

| LO Tuning Gain                                            | $V_{\text{TLINE}} = 0.5V$                              |                         |      | 103     |                   | MHz/V   |  |

|                                                           | $V_{TUNE} = 2.2V$                                      |                         | 86   |         |                   |         |  |

## AC ELECTRICAL CHARACTERISTICS—Miscellaneous Blocks

(MAX2831 EV kit:  $V_{CC_}$  = 2.8V,  $V_{CCPA}$  =  $V_{CCTXPA}$  = 3.3V,  $f_{LO}$  = 2.437GHZ,  $f_{REF}$  = 40MHz,  $\overline{SHDN}$  =  $\overline{CS}$  = high, SCLK = DIN = low, and  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                               | CONE                       | MIN                                                | TYP | MAX  | UNITS |    |

|-----------------------------------------|----------------------------|----------------------------------------------------|-----|------|-------|----|

| CRYSTAL OSCILLATOR                      |                            |                                                    |     |      |       |    |

| On-Chip Tuning Capacitance              | Maximum capacitance, A3:A0 | Maximum capacitance, A3:A0 = 1110, D6:D0 = 1111111 |     |      |       | ~  |

| Range                                   | Minimum capacitance, A3:A0 | 0 = 1110, D6:D0 = 0000000                          |     | 0.5  |       | рF |

| On-Chip Tuning Capacitance<br>Step Size |                            |                                                    |     | 0.12 |       | pF |

| ON-CHIP TEMPERATURE SEN                 | SOR                        |                                                    | •   |      |       |    |

|                                         |                            | $T_A = -40^{\circ}C$                               |     | 0.35 |       |    |

| Output Voltage                          | A3:A0 = 1000, D9:D8 = 01   | $T_A = +25^{\circ}C$                               |     | 1    |       | V  |

|                                         | $T_A = +85^{\circ}C$       |                                                    |     | 1.6  |       |    |

## AC ELECTRICAL CHARACTERISTICS—Timing

(MAX2831 EV kit:  $V_{CC_}$  = 2.8V,  $V_{CCPA}$  =  $V_{CCTXPA}$  = 3.3V,  $T_A$  =+25°C,  $f_{LO}$  = 2.437GHz,  $f_{REF}$  = 40MHz,  $\overline{SHDN}$  =  $\overline{CS}$  = high, SCLK = DIN = low, PLL loop bandwidth = 150kHz, and  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                              | CONDITIONS                                                                                                               |                      |   | ТҮР | MAX | UNITS |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------|---|-----|-----|-------|

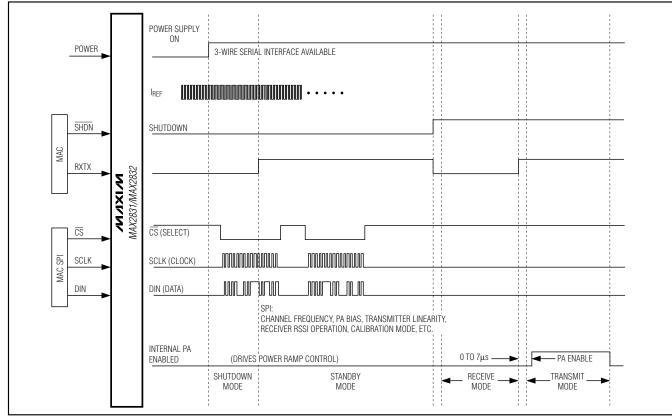

| SYSTEM TIMING (See Figure 3)           |                                                                                                                          |                      |   |     |     |       |

| Turn-On Time                           | From SHDN rising edge to LO settled within 1kHz using external reference frequency input                                 |                      |   | 60  |     | μs    |

| Crystal Oscillator Turn-On Time        | 90% of final output amplitude I                                                                                          | evel                 |   | 1   |     | ms    |

| Channel Switching Time                 | Loop BW = $150$ kHz, f <sub>RF</sub> = $2.50$                                                                            | GHz to 2.4GHz        |   | 25  |     | μs    |

| Rx/Tx Turnaround Time                  | Measured from Tx or Rx<br>enable rising edge; signal<br>settling to within ±2dB of<br>steady stateRx to TxTx to Rx, RXHI | Rx to Tx             |   | 2   |     | μs    |

|                                        |                                                                                                                          | Tx to Rx, RXHP = $1$ |   | 2   |     |       |

| Tx Turn-On Time (from Standby Mode)    | From Tx-enable active rising edge; signal settling to within ±2dB of steady state                                        |                      |   | 1.5 |     | μs    |

| Tx Turn-Off Time (from Standby Mode)   | From Tx-enable inactive rising                                                                                           |                      | 1 |     | μs  |       |

| Rx Turn-On Time (from Standby<br>Mode) | From Rx-enable active rising edge; signal settling to within ±2dB of steady state                                        |                      |   | 1.9 |     | μs    |

| Rx Turn-Off Time (from Standby Mode)   | From Rx-enable inactive rising edge                                                                                      |                      |   | 0.1 |     | μs    |

## AC ELECTRICAL CHARACTERISTICS—Timing (continued)

(MAX2831 EV kit:  $V_{CC_}$  = 2.8V,  $V_{CCPA}$  =  $V_{CCTXPA}$  = 3.3V,  $T_A$  =+25°C,  $f_{LO}$  = 2.437GHz,  $f_{REF}$  = 40MHz,  $\overline{SHDN}$  =  $\overline{CS}$  = high, SCLK = DIN = low, PLL loop bandwidth = 150kHz, and  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                                                                                                    | CONDITIONS | MIN | ТҮР | МАХ | UNITS |

|------------------------------------------------------------------------------------------------------------------------------|------------|-----|-----|-----|-------|

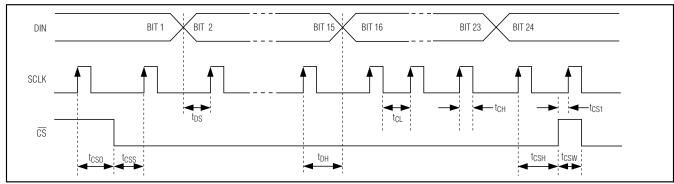

| 3-WIRE SERIAL-INTERFACE TIMING (See Figure 2)                                                                                |            |     |     |     |       |

| SCLK Rising Edge to $\overline{\text{CS}}$ Falling Edge Wait Time, t <sub>CSO</sub>                                          |            |     | 6   |     | ns    |

| Falling Edge of $\overline{CS}$ to Rising<br>Edge of First SCLK Time, t <sub>CSS</sub>                                       |            |     | 6   |     | ns    |

| DIN to SCLK Setup Time, t <sub>DS</sub>                                                                                      |            |     | 6   |     | ns    |

| DIN to SCLK Hold Time, t <sub>DH</sub>                                                                                       |            |     | 6   |     | ns    |

| SCLK Pulse-Width High, t <sub>CH</sub>                                                                                       |            |     | 6   |     | ns    |

| SCLK Pulse-Width Low, t <sub>CL</sub>                                                                                        |            |     | 6   |     | ns    |

| Last Rising Edge of SCLK to<br>Rising Edge of $\overline{\text{CS}}$ or Clock to<br>Load Enable Setup Time, t <sub>CSH</sub> |            |     | 6   |     | ns    |

| CS High Pulse Width, t <sub>CSW</sub>                                                                                        |            |     | 20  |     | ns    |

| Time Between the Rising Edge of<br><del>CS</del> and the Next Rising Edge of<br>SCLK, t <sub>CS1</sub>                       |            |     | 6   |     | ns    |

| Clock Frequency, f <sub>CLK</sub>                                                                                            |            |     | 20  |     | MHz   |

| Rise Time, t <sub>R</sub>                                                                                                    |            |     | 2   |     | ns    |

| Fall Time, t <sub>F</sub>                                                                                                    |            |     | 2   |     | ns    |

Note 1: Min and max limits are guaranteed by test at  $T_A = +25^{\circ}$ C and  $+85^{\circ}$ C and guaranteed by design and characterization at  $T_A = -40^{\circ}$ C. The power-on register settings are not production tested. Recommended register setting must be loaded after V<sub>CC</sub> is supplied.

Note 2: Guaranteed by design and characterization.

Note 3: The nominal part-to-part variation of the RF gain step is ±1dB.

Note 4: Two tones at +25MHz and +48MHz offset with -35dBm/tone. Measure IM3 at 2MHz.

Note 5: Tx I/Q inputs = 100mV<sub>RMS</sub>.

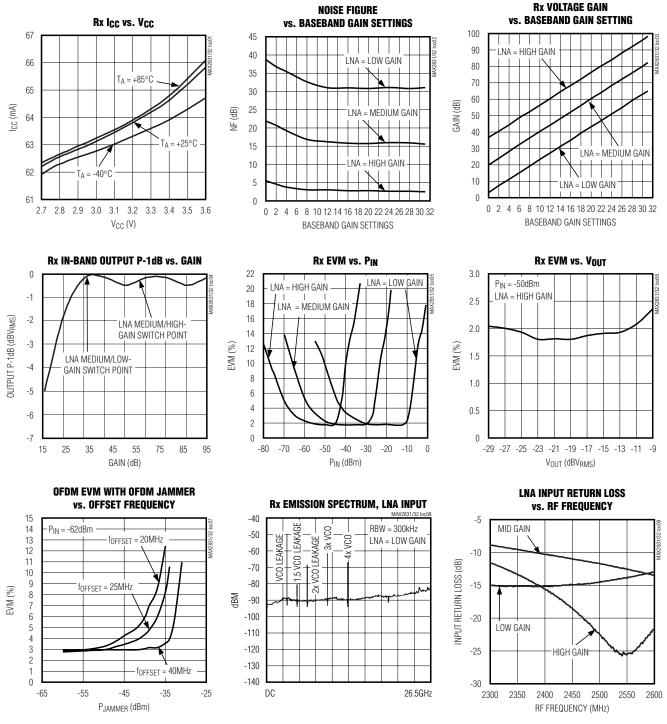

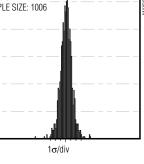

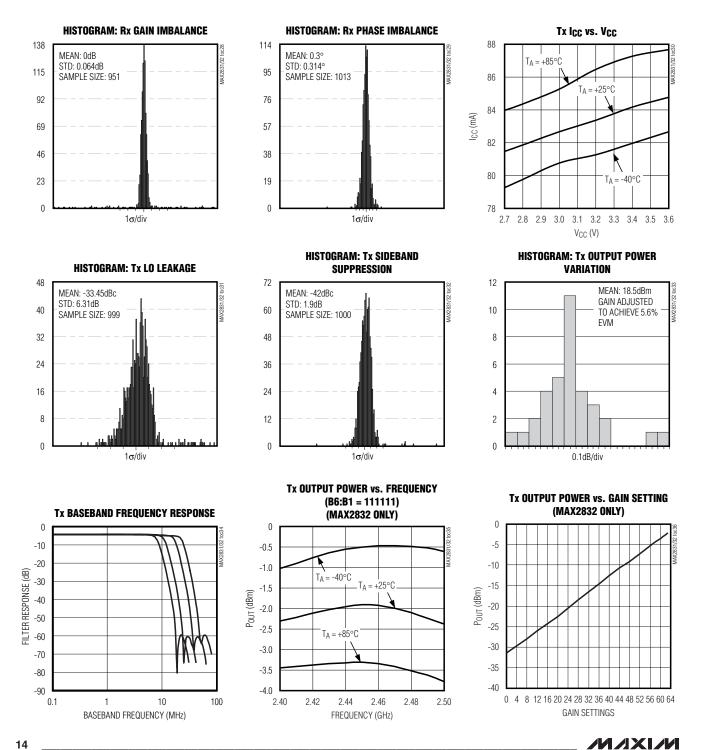

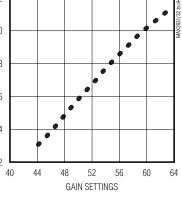

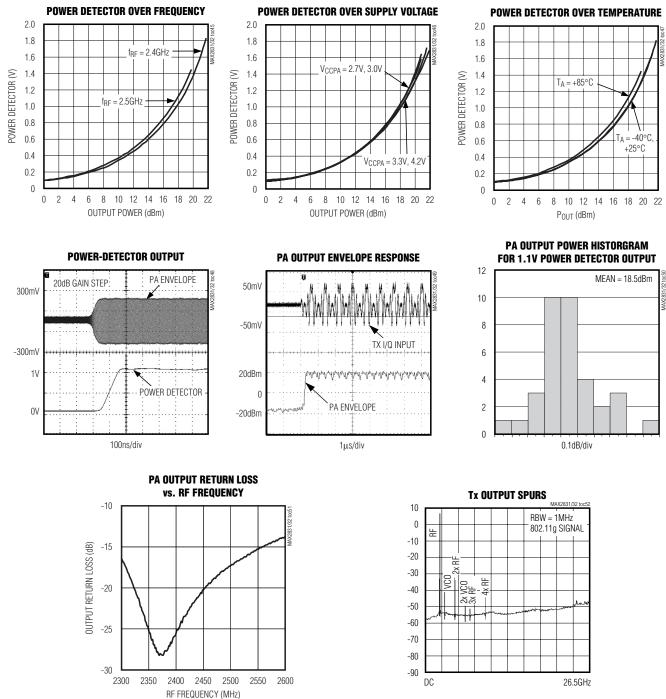

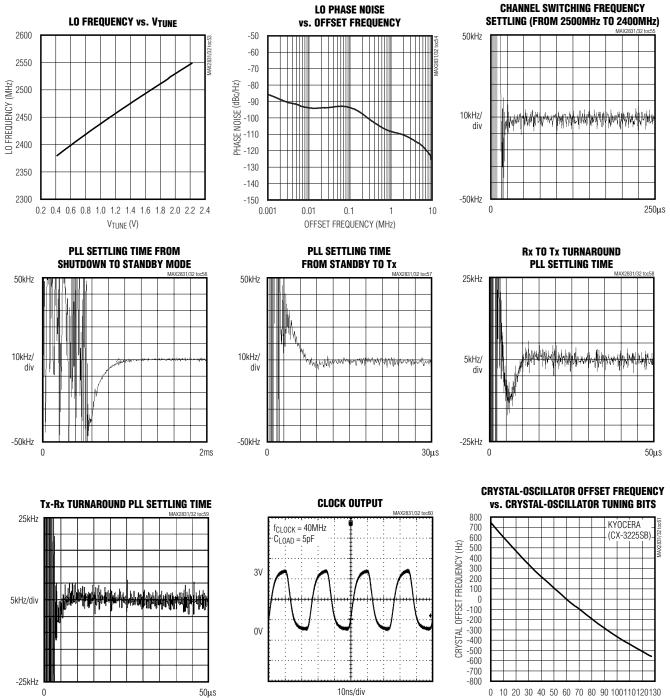

## \_Typical Operating Characteristics

(MAX2831 EV kit, V<sub>CC</sub> = 2.8V, V<sub>CCPA</sub> = V<sub>CCTXPA</sub> = 3.3V, T<sub>A</sub> = +25°C, f<sub>LO</sub> = 2.437GHz, f<sub>REF</sub> = 40MHz,  $\overline{SHDN} = \overline{CS}$  = high, RXHP = SCLK = DIN = low.)

**MAX2831/MAX2832**

## **Typical Operating Characteristics (continued)**

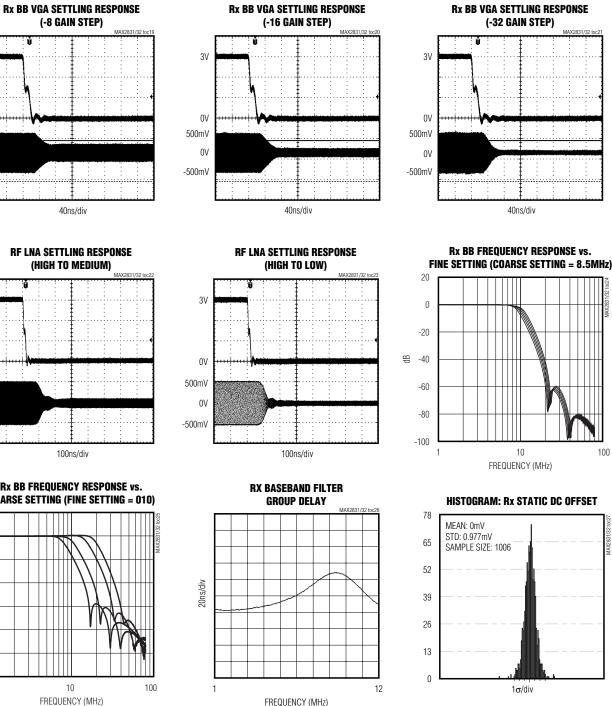

(MAX2831 EV kit, V<sub>CC</sub> = 2.8V, V<sub>CCPA</sub> = V<sub>CCTXPA</sub> = 3.3V, T<sub>A</sub> = +25°C, f<sub>LO</sub> = 2.437GHz, f<sub>REF</sub> = 40MHz,  $\overline{SHDN} = \overline{CS}$  = high, RXHP = SCLK = DIN = low.)

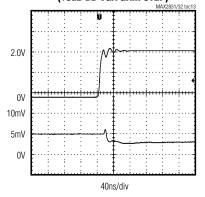

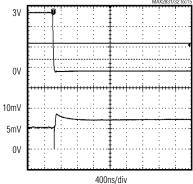

Rx I/Q DC OFFSET SETTLING RESPONSE (+8dB BB VGA GAIN STEP)

Rx I/Q DC OFFSET SETTLING RESPONSE (-8dB BB VGA GAIN STEP) MX/2831/32 toc14

I/Q OUTPUT DC ERROR DROOP (RxHP =  $1 \rightarrow 0$ ; 100Hz MODE)

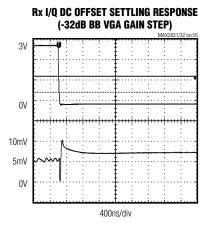

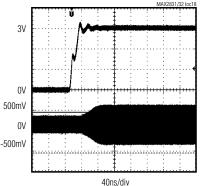

Rx I/Q DC OFFSET SETTLING RESPONSE (-16dB BB VGA GAIN STEP) MAX2831/32 loc15

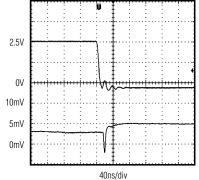

Rx BB VGA SETTLING RESPONSE (+8 GAIN STEP)

MAX2831/MAX2832

SCLK = DIN = Iow.)

(MAX2831 EV kit, V<sub>CC</sub> = 2.8V, V<sub>CCPA</sub> = V<sub>CCTXPA</sub> = 3.3V, T<sub>A</sub> = +25°C, f<sub>LO</sub> = 2.437GHz, f<sub>REF</sub> = 40MHz,  $\overline{SHDN} = \overline{CS}$  = high, RXHP =

3V 0٧ 500mV 0V -500mV

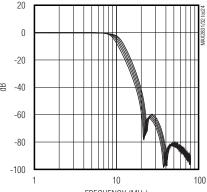

**Rx BB FREQUENCY RESPONSE vs. COARSE SETTING (FINE SETTING = 010)**

20

0

-20

-40

-60

-80

-100

믱

## **Typical Operating Characteristics (continued)**

$(MAX2831 \text{ EV kit}, \text{ V}_{CC_{-}} = 2.8\text{V}, \text{ V}_{CCPA} = \text{ V}_{CCTXPA} = 3.3\text{V}, \text{ T}_{A} = +25^{\circ}\text{C}, \text{ f}_{LO} = 2.437\text{GHz}, \text{ f}_{REF} = 40\text{MHz}, \overline{\text{SHDN}} = \overline{\text{CS}} = \text{high}, \text{RXHP} = 10^{\circ}\text{C}, \text{ f}_{LO} = 2.437\text{GHz}, \text{ f}_{REF} = 40\text{MHz}, \overline{\text{SHDN}} = \overline{\text{CS}} = \text{high}, \text{RXHP} = 10^{\circ}\text{C}, \text{ f}_{LO} = 2.437\text{GHz}, \text{ f}_{REF} = 40\text{MHz}, \overline{\text{SHDN}} = \overline{\text{CS}} = \text{high}, \text{RXHP} = 10^{\circ}\text{C}, \text{ f}_{LO} = 2.437\text{GHz}, \text{ f}_{REF} = 40\text{MHz}, \overline{\text{SHDN}} = 10^{\circ}\text{C}, \text{ f}_{LO} = 10^$ SCLK = DIN = low.)

## **Typical Operating Characteristics (continued)**

SCLK = DIN = low.)

## **Typical Operating Characteristics (continued)**

(MAX2831 EV kit,  $V_{CC_}$  = 2.8V,  $V_{CCPA}$  =  $V_{CCTXPA}$  = 3.3V,  $T_A$  = +25°C,  $f_{LO}$  = 2.437GHz,  $f_{REF}$  = 40MHz,  $\overline{SHDN}$  =  $\overline{CS}$  = high, RXHP = SCLK = DIN = Iow.)

MAX2831/MAX2832

## **Typical Operating Characteristics (continued)**

$(MAX2831 \text{ EV kit}, \text{ V}_{CC\_} = 2.8\text{V}, \text{ V}_{CCPA} = \text{ V}_{CCTXPA} = 3.3\text{V}, \text{ T}_{A} = +25^{\circ}\text{C}, \text{ f}_{LO} = 2.437\text{GHz}, \text{ f}_{REF} = 40\text{MHz}, \overline{\text{SHDN}} = \overline{\text{CS}} = \text{high}, \text{RXHP} = 10^{\circ}\text{C}$ SCLK = DIN = low.)

MAX2831/MAX2832

C<sub>TUNE</sub> (DIGITAL BITS)

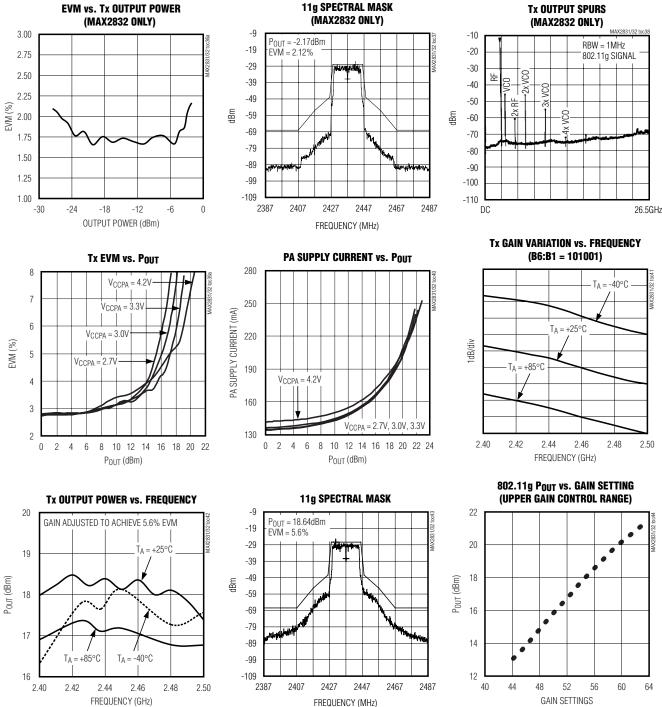

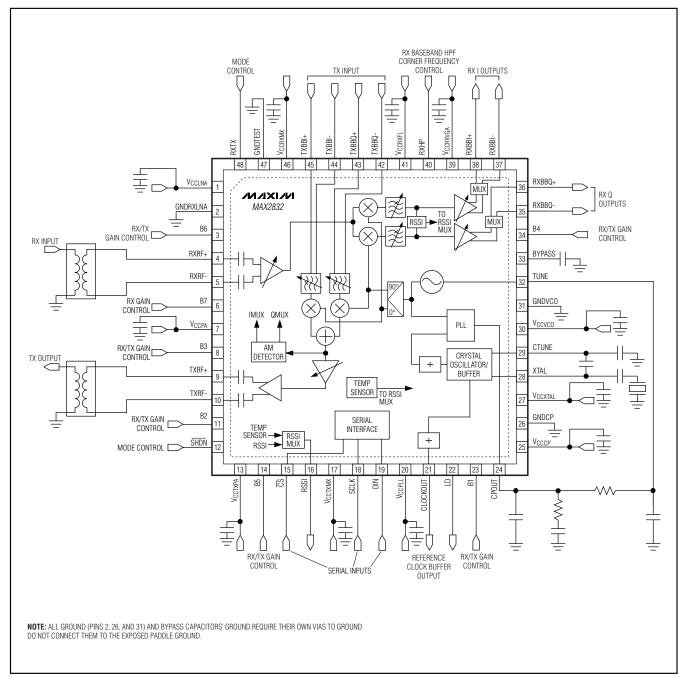

RX BASEBAND HPF MODE CONTROL CORNER FREQUENCY CONTROL TX INPUT **RX I OUTPUTS** Π Ē Ι \_ GNDTEST CCRXFI XBBQ XBB RXBBI RXTX XBBI ) BBX RXHP XBBI 48 44 43 38 37 47 45 42 41 40 - -VCCLNA RXBBQ+ 工 MUX RX Q ///XI/// OUTPUTS GNDRXLNA MAX2831 RXRB0 ΤO -RSSI MUX MUX BX/TX B6 RX/TX GAIN B4 GAIN CONTROL CONTROL **RX INPUT** RXRF+ BYPASS | Λ 38 RXRF TUNE Z XX B7 RX GAIN CONTROL GNDVCO IMUX QMUX Vccvco PLL VCCPA ΞĽ 30 ΔM RX/TX GAIN CONTROL B3 CTUNE DETECTOR CRYSTAL TX OUTPUT ÷ OSCILLATOR/ BUFFER TXRF+ \_\_\_\_ XTA TEMP SENSOR TO RSSI MUX 28 TXRF-VCCXT 27 POWER DETECTOR B2 GNDCP RX/TX GAIN SFRIAI TEMP CONTROL INTERFACE NSOR - RSSI RSSI - MUX SENSOR ---÷ SHDN Vcc MODE CONTROL 13 14 15 16 18 20 21 22 23 24 VCCTXPA CPOUT Ж RSSI 9 Ξ ß NO CLOCKOUT /CCTXMX /CCPLL SCL WM Š Ē Ţ Т V RX/TX GAIN L REFERENCE RX/TX GAIN CONTROL CLOCK BUFFER CONTROL SERIAL INPUTS OUTPUT NOTE: ALL GROUND (PINS 2, 26, AND 31) AND BYPASS CAPACITORS' GROUND REQUIRE THEIR OWN VIAS TO GROUND. DO NOT CONNECT THEM TO THE EXPOSED PADDLE GROUND.

## Block Diagrams/Typical Operating Circuits

## \_Block Diagrams/Typical Operating Circuits (continued)

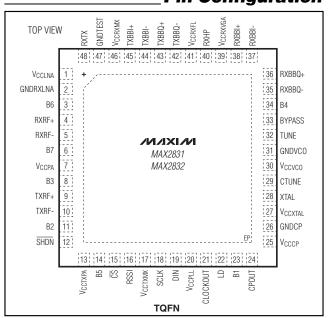

## **Pin Description**

| 1  |          | FUNCTION                                                                                                                                                                                                 |  |

|----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1  | Vcclna   | LNA Supply Voltage                                                                                                                                                                                       |  |

| 2  | GNDRXLNA | LNA Ground                                                                                                                                                                                               |  |

| 3  | B6       | Receiver and Transmitter Gain-Control Logic-Input Bit 6                                                                                                                                                  |  |

| 4  | RXRF+    | LNA Differential Input. Input is internally AC-coupled and matched to 100 $\Omega$ differential. Connect                                                                                                 |  |

| 5  | RXRF-    | directly to a 2:1 balun.                                                                                                                                                                                 |  |

| 6  | B7       | Receiver Gain-Control Logic-Input Bit 7                                                                                                                                                                  |  |

| 7  | VCCPA    | Supply Voltage for Second Stage of Power Amplifier                                                                                                                                                       |  |

| 8  | B3       | Receiver and Transmitter Gain-Control Logic-Input Bit 3                                                                                                                                                  |  |

| 9  | TXRF+    | Power-Amplifier Differential Output for the MAX2831. PA output must be AC-coupled. PA driver internally AC-coupled differential outputs and matched to $100\Omega$ differential for the MAX2832. Connect |  |

| 10 | TXRF-    | directly to a 2:1 balun.                                                                                                                                                                                 |  |

| 11 | B2       | Receiver and Transmitter Gain-Control Logic-Input Bit 2                                                                                                                                                  |  |

| 12 | SHDN     | Active-Low Shutdown and Standby Logic Input. See Table 31 for operating modes.                                                                                                                           |  |

| 13 | Vcctxpa  | Supply Voltage for First-Stage of PA and PA Driver                                                                                                                                                       |  |

| 14 | B5       | Receiver and Transmitter Gain-Control Logic-Input Bit 5                                                                                                                                                  |  |

| 15 | CS       | Active-Low Chip-Select Logic Input of 3-Wire Serial Interface (See Figure 2)                                                                                                                             |  |

| 16 | RSSI     | RSSI, PA Power Detector (MAX2831 Only) or Temperature-Sensor Multiplexed Analog Output                                                                                                                   |  |

| 17 | VCCTXMX  | Transmitter Upconverter Supply Voltage                                                                                                                                                                   |  |

| 18 | SCLK     | Serial-Clock Logic Input of 3-Wire Serial Interface (See Figure 2)                                                                                                                                       |  |

| 19 | DIN      | Data Logic Input of 3-Wire Serial Interface (See Figure 2)                                                                                                                                               |  |

| 20 | VCCPLL   | PLL and Registers Supply Voltage. Connect to the supply voltage to retain the register settings.                                                                                                         |  |

| 21 | CLOCKOUT | Reference Clock Buffer Output                                                                                                                                                                            |  |

| 22 | LD       | Lock-Detect Logic Output of Frequency Synthesizer. Output high indicates that the frequency synthesizer is locked. Output programmable as CMOS or open-drain output. (See Tables 16 and 20.)             |  |

| 23 | B1       | Receiver and Transmitter Gain-Control Logic-Input Bit 1                                                                                                                                                  |  |

| 24 | CPOUT    | Charge-Pump Output. Connect the frequency synthesizer's loop filter between CPOUT and TUNE (see the <i>Block Diagrams/Typical Operating Circuits</i> ).                                                  |  |

| 25 | VCCCP    | PLL Charge-Pump Supply Voltage                                                                                                                                                                           |  |

| 26 | GNDCP    | Charge-Pump Circuit Ground                                                                                                                                                                               |  |

| 27 | VCCXTAL  | Crystal Oscillator Supply Voltage                                                                                                                                                                        |  |

| 28 | XTAL     | Crystal or Reference Clock Input. AC-couple a crystal or a reference clock to this analog input.                                                                                                         |  |

| 29 | CTUNE    | Connection for Crystal Oscillator Off-Chip Capacitors. When using an external reference clock input leave CTUNE unconnected.                                                                             |  |

| 30 | Vccvco   | VCO Supply Voltage                                                                                                                                                                                       |  |

| 31 | GNDVCO   | VCO Ground                                                                                                                                                                                               |  |

| 32 | TUNE     | VCO TUNE Input (see the Block Diagrams/Typical Operating Circuits)                                                                                                                                       |  |

| 33 | BYPASS   | On-Chip VCO Regulator Output Bypass. Bypass with a 0.1µF to 1µF capacitor to GND. Do not connect other circuitry to this point.                                                                          |  |

|    |          |                                                                                                                                                                                                          |  |

## Pin Description (continued)

| PIN | NAME     | FUNCTION                                                                                                                                                                         |  |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 35  | RXBBQ-   | Receiver Baseband Q-Channel Differential Outputs. In TX calibration mode, these pins are the LO                                                                                  |  |

| 36  | RXBBQ+   | leakage and sideband detector outputs.                                                                                                                                           |  |