#### MAXIMUM RATINGS (Voltages referenced to Pin 7)

| Rating                                                        | Symbol                                                                               | Value                                                                                   | Unit |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------|

| Supply Current (I <sub>Pin 5</sub> )                          | I <sub>CC</sub>                                                                      | 15                                                                                      | mA   |

| Non–Repetitive Supply Current, (Pulse Width = $1.0 \ \mu s$ ) | I <sub>CCP</sub>                                                                     | 200                                                                                     | mA   |

| AC Synchronization Current                                    | I <sub>sync</sub>                                                                    | 3.0                                                                                     | mA   |

| Pin Voltages                                                  | V <sub>Pin 2</sub><br>V <sub>Pin 3</sub><br>V <sub>Pin 4</sub><br>V <sub>Pin 6</sub> | 0; V <sub>ref</sub><br>0; V <sub>ref</sub><br>0; V <sub>ref</sub><br>0; V <sub>EE</sub> | V    |

| V <sub>ref</sub> Current Sink                                 | I <sub>Pin 1</sub>                                                                   | 1.0                                                                                     | mA   |

| Output Current (Pin 6), (Pulse Width < 400 μs)                | Ι <sub>Ο</sub>                                                                       | 150                                                                                     | mA   |

| Power Dissipation                                             | PD                                                                                   | 625                                                                                     | mW   |

| Thermal Resistance, Junction-to-Air                           | $R_{	ext{	heta}JA}$                                                                  | 100                                                                                     | °C/W |

| Operating Temperature Range                                   | T <sub>A</sub>                                                                       | – 20 to + 85                                                                            | °C   |

Maximum ratings are those values beyond which device damage can occur. Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.

**ELECTRICAL CHARACTERISTICS** ( $T_A = 25^{\circ}C$ ,  $V_{EE} = -7.0$  V, voltages referred to Pin 7, unless otherwise noted.)

| Characteristic                                                                                                                           | Symbol            | Min  | Тур   | Max  | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|-------|------|------|

| Supply Current (Pins 6, 8 not connected), ( $T_A = -20^{\circ}$ to + 85°C)                                                               | I <sub>CC</sub>   | -    | 0.9   | 1.5  | mA   |

| Stabilized Supply Voltage (Pin 5), (I <sub>CC</sub> = 2.0 mA)                                                                            | V <sub>EE</sub>   | -10  | -9.0  | -8.0 | V    |

| Reference Voltage (Pin 1)                                                                                                                | V <sub>ref</sub>  | -6.5 | -5.5  | -4.5 | V    |

| Output Pulse Current (T <sub>A</sub> = $-20^{\circ}$ to + 85°C), (R <sub>out</sub> = 60 W, V <sub>EE</sub> = $-8.0$ V)                   | Ι <sub>Ο</sub>    | 90   | 100   | 130  | mA   |

| Output Leakage Current (V <sub>out</sub> = 0 V)                                                                                          | I <sub>OL</sub>   | -    | -     | 10   | μΑ   |

| Output Pulse Width (T <sub>A</sub> = $-20^{\circ}$ to $+85^{\circ}$ C) (Note 1), (Mains = 220 Vrms, R <sub>sync</sub> = 220 k $\Omega$ ) | Τ <sub>Ρ</sub>    | 50   | -     | 100  | μs   |

| Comparator Offset (Note 5)                                                                                                               | V <sub>off</sub>  | -10  | -     | +10  | mV   |

| Sensor Input Bias Current                                                                                                                | I <sub>IB</sub>   | -    | -     | 0.1  | μΑ   |

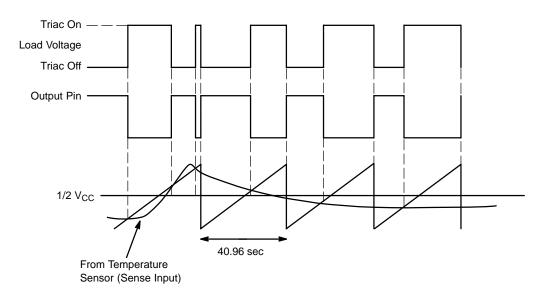

| Sawtooth Period (Note 2)                                                                                                                 | Τ <sub>S</sub>    | -    | 40.96 | -    | sec  |

| Sawtooth Amplitude (Note 6)                                                                                                              | A <sub>S</sub>    | 50   | 70    | 90   | mV   |

| Temperature Reduction Voltage (Note 3), (Pin 4 Connected to V <sub>CC</sub> )                                                            | V <sub>TR</sub>   | 280  | 350   | 420  | mV   |

| Internal Hysteresis Voltage, (Pin 2 Not Connected)                                                                                       | VIH               | -    | 10    | -    | mV   |

| Additional Hysteresis (Note 4), (Pin 2 Connected to V <sub>CC</sub> )                                                                    | V <sub>H</sub>    | 280  | 350   | 420  | mV   |

| Failsafe Threshold (T <sub>A</sub> = $-20^{\circ}$ to + 85°C) (Note 7)                                                                   | V <sub>FSth</sub> | 180  | -     | 300  | mV   |

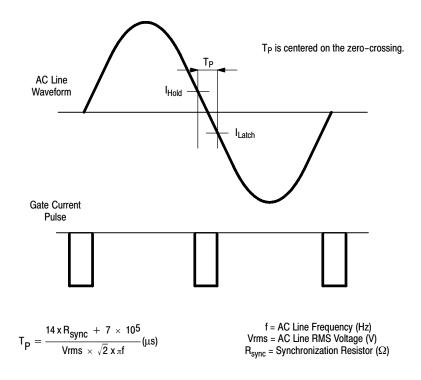

1. Output pulses are centered with respect to zero crossing point. Pulse width is adjusted by the value of R<sub>sync</sub>. Refer to application curves.

2. The actual sawtooth period depends on the AC power line frequency. It is exactly 2048 times the corresponding period. For the 50 Hz case it is 40.96 sec. For the 60 Hz case it is 34.13 sec. This is to comply with the European standard, namely that 2.0 kW loads cannot be connected or removed from the line more than once every 30 sec. The inertia of most heating systems combined with the UAA2016 will comply with the European Standard.

3. 350 mV corresponds to 5°C temperature reduction. This is tested at probe using internal test pad. Smaller temperature reduction can be obtained by adding an external resistor between Pin 4 and V<sub>CC</sub>. Refer to application curves.

350 mV corresponds to a hysteresis of 5°C. This is tested at probe using internal test pad. Smaller additional hysteresis can be obtained by adding an external resistor between Pin 2 and V<sub>CC</sub>. Refer to application curves.

5. Parameter guaranteed but not tested. Worst case 10 mV corresponds to 0.15°C shift on set point.

6. Measured at probe by internal test pad. 70 mV corresponds to 1°C. Note that the proportional band is independent of the NTC value.

At very low temperature the NTC resistor increases quickly. This can cause the sensor input voltage to reach the failsafe threshold, thus inhibiting output pulses; refer to application schematics. The corresponding temperature is the limit at which the circuit works in the typical application. By setting this threshold at 0.05 V<sub>ref</sub>, the NTC value can increase up to 20 times its nominal value, thus the application works below – 20°C.

**UAA2016**

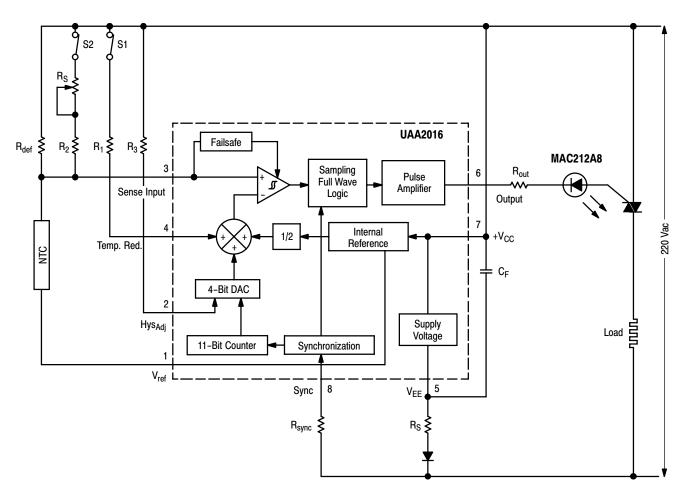

**Figure 1. Application Schematic**

#### **APPLICATION INFORMATION**

(For simplicity, the LED in series with  $R_{out}$  is omitted in the following calculations.)

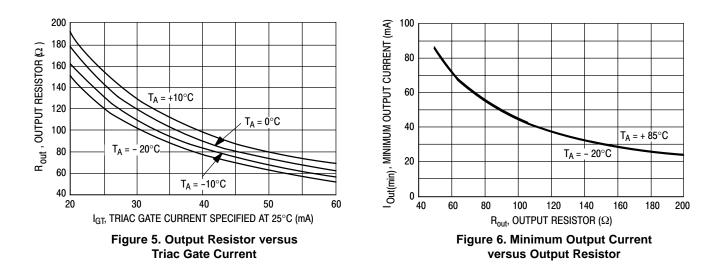

#### Triac Choice and Rout Determination

Depending on the power in the load, choose the triac that has the lowest peak gate trigger current. This will limit the output current of the UAA2016 and thus its power consumption. Use Figure 4 to determine  $R_{out}$  according to the triac maximum gate current ( $I_{GT}$ ) and the application low temperature limit. For a 2.0 kW load at 220 Vrms, a good triac choice is the ON Semiconductor MAC212A8. Its maximum peak gate trigger current at 25°C is 50 mA.

For an application to work down to  $-20^{\circ}$ C, R<sub>out</sub> should be 60  $\Omega$ . It is assumed that: I<sub>GT</sub>(T) = I<sub>GT</sub>(25°C) × exp (-T/125) with T in °C, which applies to the MAC212A8.

#### Output Pulse Width, R<sub>sync</sub>

The pulse with  $T_P$  is determined by the triac's  $I_{Hold}$ ,  $I_{Latch}$  together with the load value and working conditions (frequency and voltage):

Given the RMS AC voltage and the load power, the load value is:

$$R_L = V^2 rms/POWER$$

The load current is then:

I

$$Load = (Vrms \times \sqrt{2} \times sin(2\pi ft) - V_{TM})/R_L$$

where  $V_{TM}$  is the maximum on state voltage of the triac, f is the line frequency.

Set  $I_{Load} = I_{Latch}$  for  $t = T_P/2$  to calculate  $T_P$ .

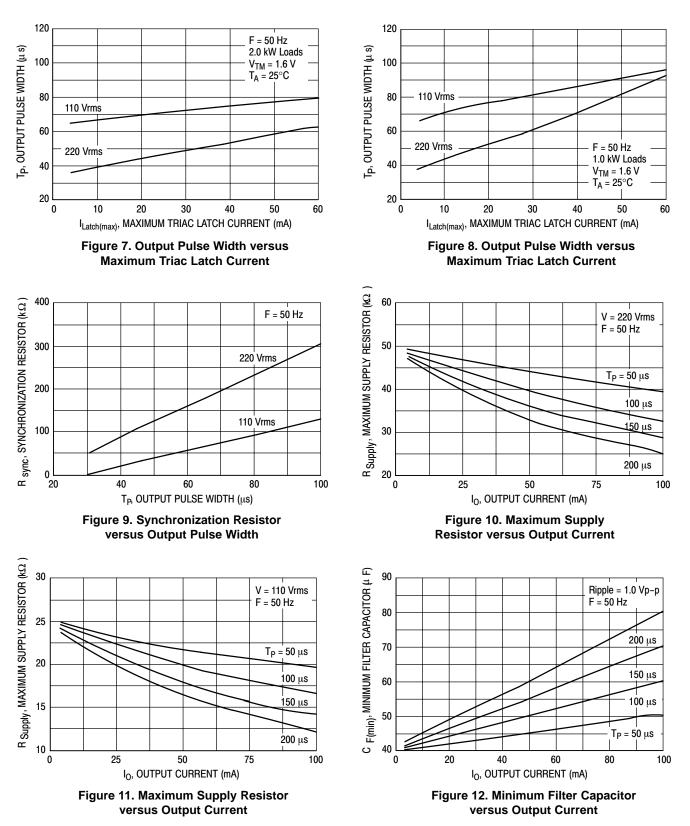

Figures 6 and 7 give the value of  $T_P$  which corresponds to the higher of the values of  $I_{Hold}$  and  $I_{Latch}$ , assuming that  $V_{TM} = 1.6$  V. Figure 8 gives the  $R_{sync}$  that produces the corresponding  $T_P$

#### R<sub>Supply</sub> and Filter Capacitor

With the output current and the pulse width determined as above, use Figures 9 and 10 to determine  $R_{Supply}$ , assuming that the sinking current at  $V_{ref}$  pin (including NTC bridge current) is less than 0.5 mA. Then use Figure 11 and 12 to determine the filter capacitor ( $C_F$ ) according to the ripple desired on supply voltage. The maximum ripple allowed is 1.0 V.

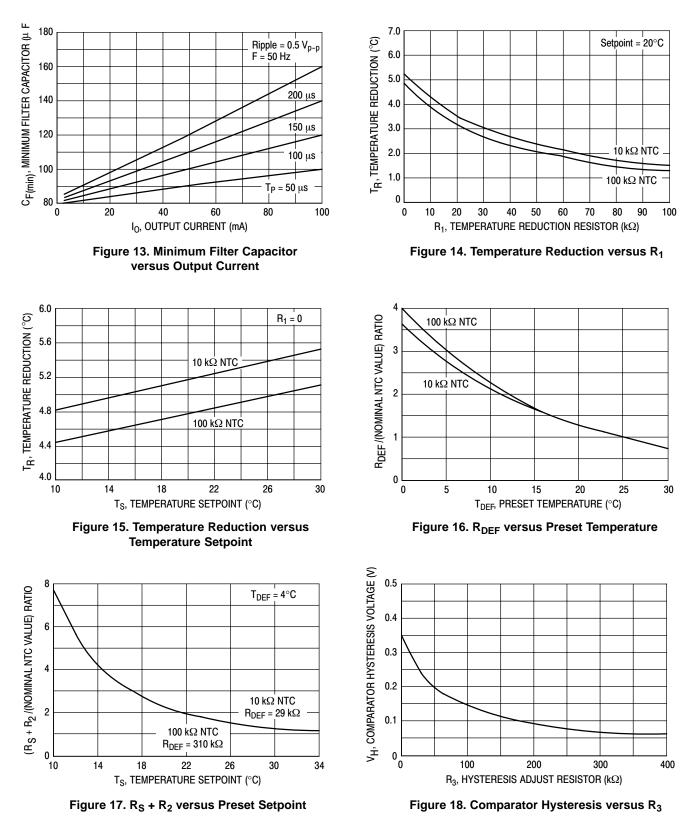

#### Temperature Reduction Determined by R<sub>1</sub>

(Refer to Figures 13 and 14.)

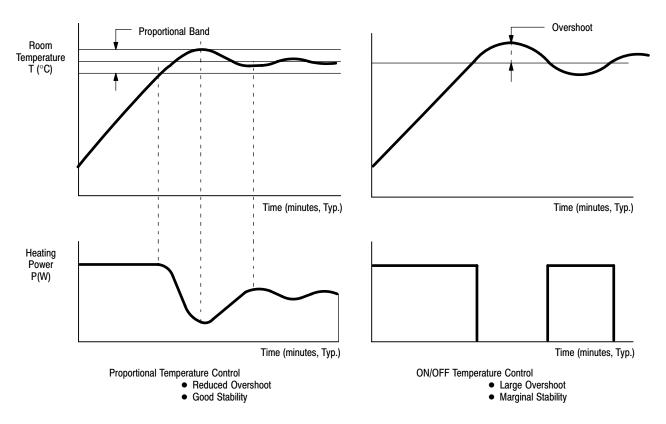

Figure 2. Comparison Between Proportional Control and ON/OFF Control

Figure 3. Zero Voltage Technique

#### **CIRCUIT FUNCTIONAL DESCRIPTION**

#### Power Supply (Pin 5 and Pin 7)

The application uses a current source supplied by a single high voltage rectifier in series with a power dropping resistor. An integrated shunt regulator delivers a  $V_{EE}$  voltage of – 8.6 V with respect to Pin 7. The current used by the total regulating system can be shared in four functional blocks: IC supply, sensing bridge, triac gate firing pulses and zener current. The integrated zener, as in any shunt regulator, absorbs the excess supply current. The 50 Hz pulsed supply current is smoothed by the large value capacitor connected between Pins 5 and 7.

#### **Temperature Sensing (Pin 3)**

The actual temperature is sensed by a negative temperature coefficient element connected in a resistor divider fashion. This two element network is connected between the ground terminal Pin 5 and the reference voltage -5.5 V available on Pin 1. The resulting voltage, a function of the measured temperature, is applied to Pin 3 and internally compared to a control voltage whose value depends on several elements: Sawtooth, Temperature Reduction and Hysteresis Adjust. (Refer to Application Information.)

#### **Temperature Reduction**

For energy saving, a remotely programmable temperature reduction is available on Pin 4. The choice of resistor  $R_1$  connected between Pin 4 and  $V_{CC}$  sets the temperature reduction level.

#### Comparator

When the noninverting input (Pin 3) receives a voltage less than the internal reference value, the comparator allows the triggering logic to deliver pulses to the triac gate. To improve the noise immunity, the comparator has an adjustable hysteresis. The external resistor  $R_3$  connected to Pin 2 sets the hysteresis level. Setting Pin 2 open makes a 10 mV hysteresis level, corresponding to 0.15°C. Maximum hysteresis is obtained by connecting Pin 2 to V<sub>CC</sub>. In that case the level is set at 5°C. This configuration can be useful for low temperature inertia systems.

#### Sawtooth Generator

In order to comply with European norms, the ON/OFF period on the load must exceed 30 seconds. This is achieved by an internal digital sawtooth which performs the proportional regulation without any additional components. The sawtooth signal is added to the reference applied to the comparator inverting input. Figure 2 shows the regulation improvement using the proportional band action. Figure 4 displays a timing diagram of typical system performance using the UAA2016. The internal sawtooth generator runs at a typical 40.96 sec period. The output duty cycle drive waveform is adjusted depending on the time within the 40.96 sec period the drive needs to turn on. This occurs when the voltage on the sawtooth waveform is above the voltage provided at the Sense Input.

#### **Noise Immunity**

The noisy environment requires good immunity. Both the voltage reference and the comparator hysteresis minimize the noise effect on the comparator input. In addition the effective triac triggering is enabled every 1/3 sec.

#### Failsafe

Output pulses are inhibited by the "failsafe" circuit if the comparator input voltage exceeds the specified threshold voltage. This would occur if the temperature sensor circuit is open.

#### Sampling Full Wave Logic

Two consecutive zero–crossing trigger pulses are generated at every positive mains half–cycle. This ensures that the number of delivered pulses is even in every case. The pulse length is selectable by  $R_{sync}$  connected on Pin 8. The pulse is centered on the zero–crossing mains waveform.

#### **Pulse Amplifier**

The pulse amplifier circuit sinks current pulses from Pin 6 to  $V_{EE}$ . The minimum amplitude is 70 mA. The triac is then triggered in quadrants II and III. The effective output current amplitude is given by the external resistor  $R_{out}$ . Eventually, an LED can be inserted in series with the Triac gate (see Figure 1).

#### **ORDERING INFORMATION**

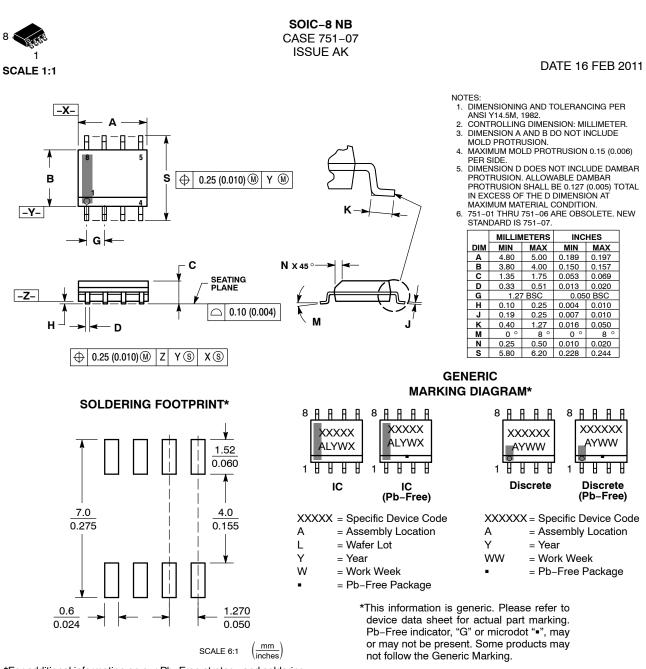

| Device     | Operating Temperature Range | Package             | Shipping <sup>†</sup> |  |

|------------|-----------------------------|---------------------|-----------------------|--|

| UAA2016D   |                             | SOIC-8              | 98 Units / Rail       |  |

| UAA2016DG  |                             | SOIC-8<br>(Pb-Free) | 98 Units / Rail       |  |

| UAA2016AD  | — T                         | SOIC-8              | 98 Units / Rail       |  |

| UAA2016ADG | $T_A = -20^\circ$ to +85°C  | SOIC-8<br>(Pb-Free) | 98 Units / Rail       |  |

| UAA2016P   | — T                         | PDIP-8              | 1000 Units / Rail     |  |

| UAA2016PG  |                             | PDIP-8<br>(Pb-Free) | 1000 Units / Rail     |  |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

A = Assembly Location

- WL = Wafer Lot

- YY = Year

- WW = Work Week

- G = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb–Free indicator, "G" or microdot " ■", may or may not be present.

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

### STYLES ON PAGE 2

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 98ASB42564B         | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CRIPTION: SOIC-8 NB |                                                                                                                                                                                     | PAGE 1 OF 2 |  |  |  |

| ON Semiconductor and ()) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding<br>the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically<br>disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights or the |                     |                                                                                                                                                                                     |             |  |  |  |

© Semiconductor Components Industries, LLC, 2019

#### SOIC-8 NB CASE 751-07 ISSUE AK

STYLE 1: PIN 1. EMITTER COLLECTOR 2. COLLECTOR 3. 4. EMITTER 5. EMITTER BASE 6. 7 BASE EMITTER 8. STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN DRAIN 4. GATE 5. 6. GATE SOURCE 7. 8. SOURCE STYLE 9: PIN 1. EMITTER, COMMON COLLECTOR, DIE #1 COLLECTOR, DIE #2 2. З. EMITTER, COMMON 4. 5. EMITTER, COMMON 6 BASE. DIE #2 BASE, DIE #1 7. 8. EMITTER, COMMON STYLE 13: PIN 1. N.C. 2. SOURCE 3 GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. DRAIN 8. STYLE 17: PIN 1. VCC 2. V2OUT V10UT З. TXE 4. 5. RXE 6. VFF 7. GND 8. ACC STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3 CATHODE 3 CATHODE 4 4. 5. CATHODE 5 6. COMMON ANODE COMMON ANODE 7. 8. CATHODE 6 STYLE 25: PIN 1. VIN 2 N/C REXT З. 4. GND 5. IOUT 6. IOUT IOUT 7. 8. IOUT STYLE 29: BASE, DIE #1 PIN 1. 2 EMITTER, #1 BASE, #2 З. EMITTER, #2 4. 5 COLLECTOR, #2

STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 COLLECTOR, #2 3. 4 COLLECTOR, #2 BASE, #2 5. EMITTER, #2 6. 7 BASE #1 EMITTER, #1 8. STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN SOURCE 4. SOURCE 5. 6. GATE GATE 7. 8. SOURCE STYLE 10: GROUND PIN 1. BIAS 1 OUTPUT 2. З. GROUND 4. 5. GROUND 6 BIAS 2 INPUT 7. 8. GROUND STYLE 14: PIN 1. N-SOURCE 2. N-GATE P-SOURCE 3 P-GATE 4. P-DRAIN 5 6. P-DRAIN N-DRAIN 7. N-DRAIN 8. STYLE 18: PIN 1. ANODE 2. ANODE SOURCE 3. GATE 4. 5. DRAIN 6 DRAIN CATHODE 7. CATHODE 8. STYLE 22 PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3 COMMON CATHODE/VCC 4. I/O LINE 3 5. COMMON ANODE/GND 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND STYLE 26: PIN 1. GND 2 dv/dt З. ENABLE 4. ILIMIT 5. SOURCE SOURCE 6. SOURCE 7. 8. VCC STYLE 30: DRAIN 1 PIN 1. DRAIN 1 2 GATE 2 З. SOURCE 2 4. SOURCE 1/DRAIN 2 SOURCE 1/DRAIN 2 5. 6.

STYLE 3: PIN 1. DRAIN, DIE #1 DRAIN, #1 2. DRAIN, #2 З. 4. DRAIN, #2 GATE, #2 5. SOURCE, #2 6. 7 GATE #1 8. SOURCE, #1 STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS THIRD STAGE SOURCE GROUND З. 4. 5. DRAIN 6. GATE 3 SECOND STAGE Vd 7. FIRST STAGE Vd 8. STYLE 11: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. 3. GATE 2 4. 5. DRAIN 2 6. DRAIN 2 DRAIN 1 7. 8. DRAIN 1 STYLE 15: PIN 1. ANODE 1 2. ANODE 1 ANODE 1 3 ANODE 1 4. 5. CATHODE, COMMON CATHODE, COMMON CATHODE, COMMON 6. 7. CATHODE, COMMON 8. STYLE 19: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. 3. GATE 2 4. 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 8. **MIRROR 1** STYLE 23: PIN 1. LINE 1 IN COMMON ANODE/GND COMMON ANODE/GND 2. 3 LINE 2 IN 4. LINE 2 OUT 5. COMMON ANODE/GND COMMON ANODE/GND 6. 7. LINE 1 OUT 8. STYLE 27: PIN 1. ILIMIT 2 OVI 0 UVLO З. 4. INPUT+ 5. SOURCE SOURCE 6. SOURCE 7. 8 DRAIN

#### DATE 16 FEB 2011

STYLE 4: PIN 1. 2. ANODE ANODE ANODE З. 4. ANODE ANODE 5. 6. ANODE 7 ANODE COMMON CATHODE 8. STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 BASE, #2 З. COLLECTOR, #2 4. COLLECTOR, #2 5. 6. EMITTER, #2 EMITTER, #1 7. 8. COLLECTOR, #1 STYLE 12: PIN 1. SOURCE SOURCE 2. 3. GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 16: PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 EMITTER, DIE #2 3 BASE, DIE #2 4. 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 COLLECTOR, DIE #1 7. COLLECTOR, DIE #1 8. STYLE 20: PIN 1. SOURCE (N) GATE (N) SOURCE (P) 2. 3. 4. GATE (P) 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 24: PIN 1. BASE 2. EMITTER 3 COLLECTOR/ANODE COLLECTOR/ANODE 4. 5. CATHODE 6. CATHODE COLLECTOR/ANODE 7. 8. COLLECTOR/ANODE STYLE 28: PIN 1. SW\_TO\_GND 2. DASIC OFF DASIC\_SW\_DET З. 4. GND 5. 6. V MON VBULK 7. VBULK 8 VIN

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 98ASB42564B         | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CRIPTION: SOIC-8 NB |                                                                                                                                                                                     | PAGE 2 OF 2 |  |  |

| ON Semiconductor and () are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding<br>the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically<br>disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the |                     |                                                                                                                                                                                     |             |  |  |

SOURCE 1/DRAIN 2

7.

8. GATE 1

COLLECTOR, #2

COLLECTOR, #1

COLLECTOR, #1

6.

7.

8

rights of others

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and calcular performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

onsemi Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Onsemi: UAA2016DG UAA2016PG