## **Absolute Maximum Ratings**

| Voltage (with respect to GND)          |                                  |

|----------------------------------------|----------------------------------|

| V <sub>BB</sub>                        | 0.3V to +80V                     |

| Vcc                                    | 0.3V to +6V                      |

| OUT                                    | 0.3V to $(V_{BB} + 0.3V)$        |

| All Other Pins                         | 0.3V to (V <sub>CC</sub> + 0.3V) |

| OUT_ Continuous Source Current         | 45mA                             |

| OUT_ Pulsed (1ms max, 1/4 max duty) \$ | Source Current80mA               |

| Total OUT_ Continuous Source Current   | :540mA                           |

| Total OUT_ Continuous Sink Current     | 60mA                             |

| Total OUT_ Pulsed (1ms max, 1/4 max    | duty)                            |

| Source Current                         | 960mA                            |

|                                        |                                  |

| OUT_ Sink Current                                                           | 15mA   |

|-----------------------------------------------------------------------------|--------|

| CLK, DIN, LOAD, BLANK, DOUT Current                                         |        |

| Continuous Power Dissipation                                                |        |

| 20-Pin Wide SO (derate 10mW/°C over T <sub>A</sub> = +70°C)                 | .800mW |

| Operating Temperature Range (T <sub>MIN</sub> to T <sub>MAX</sub> )-40°C to | +125°C |

| Junction Temperature                                                        | +150°C |

| Storage Temperature Range65°C to                                            | +150°C |

| Lead Temperature (soldering, 10s)                                           | +300°C |

|                                                                             |        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Electrical Characteristics**

(Typical Operating Circuit,  $V_{BB}$  = 8V to 76V,  $V_{CC}$  = 3V to 5.5V,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.) (Note 1)

| PARAMETER                      | SYMBOL          | CONI                                                    | DITIONS                                        | MIN                   | TYP                 | MAX  | UNITS |

|--------------------------------|-----------------|---------------------------------------------------------|------------------------------------------------|-----------------------|---------------------|------|-------|

| Logic Supply Voltage           | V <sub>CC</sub> |                                                         |                                                | 3                     |                     | 5.5  | V     |

| Tube Supply Voltage            | V <sub>BB</sub> |                                                         |                                                | 8                     |                     | 76   | V     |

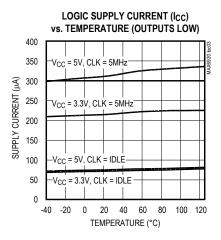

|                                | lcc             | All outputs OUT_<br>low, CLK = idle                     | T <sub>A</sub> = +25°C                         |                       | 72                  | 170  | - μΑ  |

| Logic Supply Operating Current |                 |                                                         | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$ |                       |                     | 200  |       |

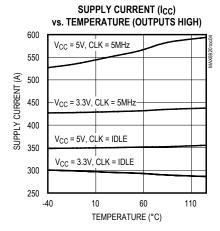

| Logic Supply Operating Current |                 | All outputs OUT_                                        | T <sub>A</sub> = +25°C                         |                       | 350                 | 650  |       |

|                                |                 | high, CLK = idle                                        | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$ |                       |                     | 700  |       |

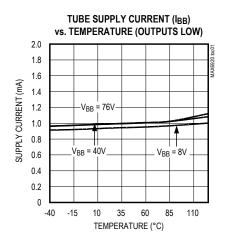

|                                |                 |                                                         | T <sub>A</sub> = +25°C                         |                       | 1                   | 2    | mA    |

|                                | l               | All outputs OUT_ low                                    | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$ |                       |                     | 4.2  |       |

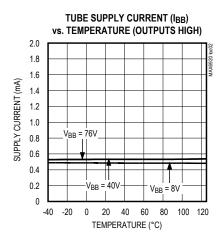

| Tube Supply Operating Current  | l <sub>BB</sub> | All outputs OUT_                                        | T <sub>A</sub> = +25°C                         |                       | 0.53                | 0.85 |       |

|                                |                 | high                                                    | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$ |                       |                     | 0.9  |       |

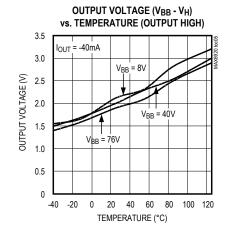

|                                | V <sub>H</sub>  | V <sub>BB</sub> ≥ 15V,<br>I <sub>OUT</sub> = -25mA      | T <sub>A</sub> = +25°C                         | VI                    | <sub>3B</sub> - 1.1 |      |       |

|                                |                 |                                                         | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$  | V <sub>BB</sub> - 2   |                     |      | V     |

|                                |                 |                                                         | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$ | V <sub>BB</sub> - 2.5 |                     |      |       |

| High-Voltage OUT_              |                 | $V_{BB} \ge 15V$ ,<br>$I_{OUT} = -40mA$                 | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$  | V <sub>BB</sub> - 3.5 |                     |      |       |

| Tright-vollage Oo1_            |                 |                                                         | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$ | V <sub>BB</sub> - 4.0 |                     |      |       |

|                                |                 | 8V < V <sub>BB</sub> < 15V,<br>I <sub>OUT</sub> = -25mA | T <sub>A</sub> = +25°C                         | VI                    | <sub>3B</sub> - 1.2 |      |       |

|                                |                 |                                                         | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$  | V <sub>BB</sub> - 2.5 |                     |      |       |

|                                |                 |                                                         | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$ | V <sub>BB</sub> - 3.0 |                     |      |       |

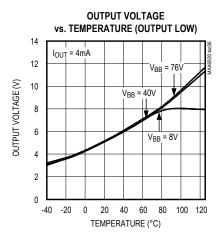

|                                | VL              | V <sub>BB</sub> ≥ 15V,<br>I <sub>OUT</sub> = 1mA        | T <sub>A</sub> = +25°C                         |                       | 0.75                | 1    | - V   |

|                                |                 |                                                         | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$  |                       |                     | 1.5  |       |

| Low-Voltage OUT_               |                 |                                                         | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$ |                       |                     | 1.9  |       |

| Low-voilage OO1_               | VL              | 8V < V <sub>BB</sub> < 15V,<br>I <sub>OUT</sub> = 1mA   | T <sub>A</sub> = +25°C                         |                       | 8.0                 | 1.1  |       |

|                                |                 |                                                         | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$  |                       |                     | 1.6  |       |

|                                |                 |                                                         | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$ |                       |                     | 2.0  |       |

www.maximintegrated.com Maxim Integrated | 2

## **Electrical Characteristics (continued)**

(Typical Operating Circuit,  $V_{BB}$  = 8V to 76V,  $V_{CC}$  = 3V to 5.5V,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.) (Note 1)

| PARAMETER                                         | SYMBOL                            | COI                                              | NDITIONS                   | MIN                      | TYP      | MAX                      | UNITS |

|---------------------------------------------------|-----------------------------------|--------------------------------------------------|----------------------------|--------------------------|----------|--------------------------|-------|

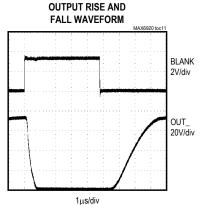

| Rise Time OUT_ (20% to 80%)                       | t <sub>R</sub>                    | $V_{BB} = 60V, C_{L} = 50pF, R_{L} = 2.3k\Omega$ |                            |                          | 0.9      | 2                        | μs    |

| Fall Time OUT_ (80% to 20%)                       | t <sub>F</sub>                    | $V_{BB} = 60V, C_L = 50pF, R_L = 2.3k\Omega$     |                            |                          | 0.6      | 1.5                      | μs    |

| SERIAL INTERFACE TIMING CHAR                      | RACTERISTIC                       | CS                                               |                            |                          |          |                          |       |

| LOAD Rising to OUT_ Falling Delay                 |                                   | (Notes 2, 3)                                     |                            |                          | 0.9      | 1.8                      | μs    |

| LOAD Rising to OUT_ Rising Delay                  |                                   | (Notes 2, 3)                                     |                            |                          | 1.2      | 2.4                      | μs    |

| BLANK Rising to OUT_ Falling Delay                |                                   | (Notes 2, 3)                                     |                            |                          | 0.9      | 1.8                      | μs    |

| BLANK Falling to OUT_ Rising Delay                |                                   | (Notes 2, 3)                                     |                            |                          | 1.3      | 2.5                      | μs    |

| Input Leakage Current<br>CLK, DIN, LOAD, BLANK    | I <sub>IH</sub> , I <sub>IL</sub> |                                                  |                            |                          | 0.05     | 10                       | μA    |

| Logic-High Input Voltage<br>CLK, DIN, LOAD, BLANK | V <sub>IH</sub>                   |                                                  |                            | 0.8 x<br>V <sub>CC</sub> |          |                          | V     |

| Logic-Low Input Voltage<br>CLK, DIN, LOAD, BLANK  | V <sub>IL</sub>                   |                                                  |                            |                          |          | 0.3 x<br>V <sub>CC</sub> | V     |

| Hysteresis Voltage<br>DIN, CLK, LOAD, BLANK       | ΔV <sub>I</sub>                   |                                                  |                            |                          | 0.6      |                          | V     |

| High-Voltage DOUT                                 | V <sub>OH</sub>                   | I <sub>SOURCE</sub> = -1.0mA                     |                            | V <sub>CC</sub> – 0.5    |          |                          | V     |

| Low-Voltage DOUT                                  | V <sub>OL</sub>                   | I <sub>SINK</sub> = 1.0mA                        |                            |                          |          | 0.5                      | V     |

| Rise and Fall Time DOUT                           |                                   | C <sub>DOUT</sub> = 10pF<br>(Note 2)             | 3V to 4.5V<br>4.5V to 5.5V |                          | 60<br>30 | 100<br>80                | ns    |

| CLK Clock Period                                  | t <sub>CP</sub>                   |                                                  |                            | 200                      |          |                          | ns    |

| CLK Pulse-Width High                              | t <sub>CH</sub>                   |                                                  |                            | 90                       |          |                          | ns    |

| CLK Pulse-Width Low                               | t <sub>CL</sub>                   |                                                  |                            | 90                       | ,        |                          | ns    |

| CLK Rise to LOAD Rise Hold Time                   | tcsH                              | (Note 2)                                         |                            | 100                      |          |                          | ns    |

| DIN Setup Time                                    | t <sub>DS</sub>                   |                                                  |                            | 5                        | ,        | ,                        | ns    |

| DINI Hald Time                                    | t <sub>DH</sub>                   | 3V to 4.5V                                       |                            | 20                       |          |                          |       |

| DIN Hold Time                                     |                                   | 4.5V to 5.5V                                     |                            | 15                       | _        |                          | ns    |

| DOUT Propagation Delay                            | t <sub>DO</sub>                   | C 10pE                                           | 3.0V to 4.5V               | 25                       | 120      | 240                      | ne    |

| DOOT FTOPAGALIOTI Delay                           |                                   | C <sub>DOUT</sub> = 10pF                         | 4.5V to 5.5V               | 20                       | 75       | 150                      | ns    |

| LOAD Pulse High                                   | t <sub>CSW</sub>                  |                                                  |                            | 55                       |          |                          | ns    |

**Note 1:** All parameters are tested at  $T_A = +25$ °C. Specifications over temperature are guaranteed by design.

Note 2: Guaranteed by design.

Note 3: Delay measured from control edge to when output OUT\_ changes by 1V.

### **Typical Operating Characteristics**

( $V_{CC}$  = 5.0V,  $V_{BB}$  = 76V, and  $T_A$  = +25°C, unless otherwise noted.)

## **Pin Description**

| PIN        | NAME             | FUNCTION                                                                                                                                                                                                       |

|------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | V <sub>BB</sub>  | VFD Tube Supply Voltage                                                                                                                                                                                        |

| 2          | DOUT             | Serial-Clock Output. Data is clocked out of the internal shift register to DOUT on CLK's rising edge.                                                                                                          |

| 3–8, 13–18 | OUT0 to<br>OUT11 | VFD Anode and Grid Drivers. OUT0 to OUT11 are push-pull outputs swinging from V <sub>BB</sub> to GND.                                                                                                          |

| 9          | BLANK            | Blanking Input. High forces outputs OUT0 to OUT11 low, without altering the contents of the output latches. Low enables outputs OUT0 to OUT11 to follow the state of the output latches.                       |

| 10         | GND              | Ground                                                                                                                                                                                                         |

| 11         | CLK              | Serial-Clock Input. Data is loaded into the internal shift register on CLK's rising edge.                                                                                                                      |

| 12         | LOAD             | Load Input. Data is loaded transparently from the internal shift register to the output latch while LOAD is high. Data is latched into the output latch on LOAD's rising edge, and retained while LOAD is low. |

| 19         | DIN              | Serial-Data Input. Data is loaded into the internal shift register on CLK's rising edge.                                                                                                                       |

| 20         | V <sub>CC</sub>  | Logic Supply Voltage                                                                                                                                                                                           |

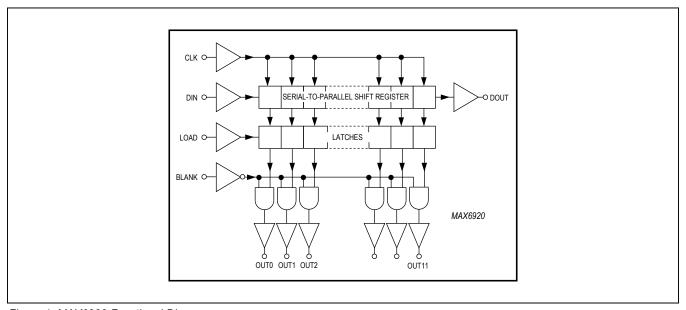

Figure 1. MAX6920 Functional Diagram

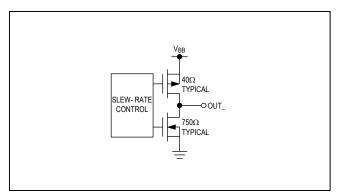

Figure 2. MAX6920 CMOS Output Driver Structure

#### **Detailed Description**

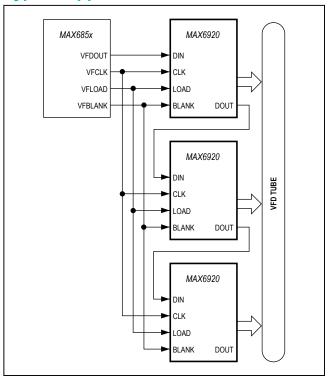

The MAX6920 is a VFD tube driver comprising a 4-wire serial interface driving 12 high-voltage rail-to-rail output ports. The driver is suitable for both static and multiplexed displays.

The output ports feature high current-sourcing capability to drive current into grids and anodes of static or multiplex VFDs. The ports also have active current sinking for fast discharge of capacitive display electrodes in multiplexing applications.

The 4-wire serial interface comprises a 12-bit shift register and a 12-bit transparent latch. The shift register is written through a clock input CLK and a data input DIN and the data propagates to a data output DOUT. The data output allows multiple drivers to be cascaded and operated together. The output latch is transparent to

the shift register outputs when LOAD is high, and latches the current state on the falling edge of LOAD.

Each driver output is a slew-rated controlled CMOS pushpull switch driving between  $V_{BB}$  and GND. The output rise time is always slower than the output fall time to avoid shoot-through currents during output transitions. The output slew rates are slow enough to minimize EMI, yet are fast enough so as not to impact the typical 100 $\mu$ s digit multiplex period and affect the display intensity.

#### **Initial Power-Up and Operation**

An internal reset circuit clears the internal registers of the MAX6920 on power-up. All outputs OUT0 to OUT11 and the interface output DOUT initialize low regardless of the initial logic levels of the CLK, DIN, BLANK, and LOAD inputs.

#### **4-Wire Serial Interface**

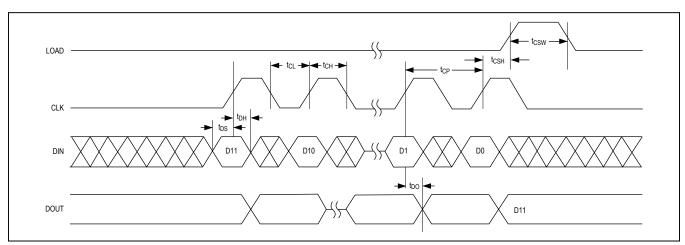

The MAX6920 uses a 4-wire serial interface with three inputs (DIN, CLK, LOAD) and a data output (DOUT). This interface is used to write output data to the MAX6920 (Figure 3) (Table 1). The serial interface data word length is 12 bits, D0–D11.

The functions of the four serial interface pins are:

- CLK input is the interface clock, which shifts data into the MAX6920's 12-bit shift register on its rising edge.

- LOAD input passes data from the MAX6920's 12-bit shift register to the 12-bit output latch when LOAD is high (transparent latch), and latches the data on LOAD's falling edge.

Figure 3. 4-Wire Serial Interface Timing Diagram

SERIAL CLOCK LOAD **BLANKING** SHIFT REGISTER CONTENTS **LATCH CONTENTS OUTPUT CONTENTS INPUT INPUT INPUT** DATA INPUT Dn-1 Dn Dn-1 Dn CLK D0 D1 D2 Dn-1 Dn LOAD D0 D1 D2 **BLANK** D0 D1 D2 DIN Н Н R0 R1 Rn-2 Rn-1 ... \_ L R0 R1 Rn-2 Rn-1 Χ ` R0 R1 R2 ... Rn-1 Rn Χ Χ Χ Χ Χ L R0 R1 R2 Rn-1 Rn ... P0 P1 P2 Pn-1 Pn Н P0 P1 P2 Pn-1 Pn L P0 P1 P2 Pn-1 Pn ... Χ Χ Χ Х Χ Н L L L L ı

**Table 1. 4-Wire Serial Interface Truth Table**

L = Low logic level.

H = High logic level.

X = Don't care.

P = Present state (shift register).

R = Previous state (latched).

- DIN is the interface data input, and must be stable when it is sampled on the rising edge of CLK.

- DOUT is the interface data output, which shifts data out from the MAX6920' 12-bit shift register on the falling edge of CLK. Data at DIN is propagated through the shift register and appears at DOUT (20 CLK cycles + t<sub>DO</sub>) later.

A fifth input pin, BLANK, can be taken high to force outputs OUT0 to OUT11 low, without altering the contents of the output latches. When the BLANK input is low, outputs OUT0 to OUT11 follow the state of the output latches. A common use of the BLANK input is PWM intensity control.

The BLANK input's function is independent of the operation of the serial interface. Data can be shifted into the serial interface shift register and latched regardless of the state of BLANK.

# Writing Device Registers Using the 4-Wire Serial Interface

The MAX6920 is written using the following sequence:

- 1) Take CLK low.

- 2) Clock 12 bits of data in order D11 first to D0 last into DIN, observing the data setup and hold times.

- Load the 12 output latches with a falling edge on LOAD.

LOAD may be high or low during a transmission. If LOAD is high, then the data shifted into the shift register at DIN appears at the OUT0 to OUT11 outputs.

CLK and DIN may be used to transmit data to other peripherals. Activity on CLK always shifts data into the MAX6920's shift register. However, the MAX6920 only updates its output latch on the rising edge of LOAD, and the last 12 bits of data are loaded. Therefore, multiple devices can share CLK and DIN as long as they have unique LOAD controls.

#### **Determining Driver Output Voltage Drop**

The outputs are CMOS drivers, and have a resistive characteristic. The typical and maximum sink and source output resistances can be calculated from the  $V_H$  and  $V_L$  electrical characteristics. Use this calculated resistance to determine the output voltage drop at different output currents.

#### **Output Current Ratings**

The continuous current source capability is 40mA per output. Outputs may drive up to 75mA as a repetitive peak current, subject to the on time (output high) being no longer than 1ms, and the duty cycle being such that the output power dissipation is no more than the dissipation for the continuous case. The repetitive peak rating allows outputs to drive a higher current in multiplex grid driver applications, where only one grid is on at a time, and the multiplex time per grid is no more than 1ms.

www.maximintegrated.com Maxim Integrated | 7

Since dissipation is proportional to current squared, the maximum current that can be delivered for a given multiplex ratio is given by:

$$I_{PEAK} = (grids \times 1600)^{1/2} mA$$

where grids is the number of grids in a multiplexed display.

This means that a duplex application (two grids) can use a repetitive peak current of 56.5mA, a triplex application (three grids) can use a repetitive peak current of 69.2mA, and higher multiplex ratios are limited to 75mA.

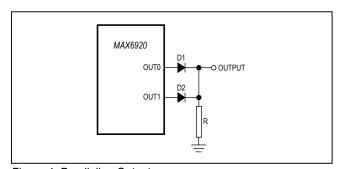

#### **Paralleling Outputs**

Any number of outputs within the same package may be paralleled in order to raise the current drive or reduce the output resistance. Only parallel outputs directly (by shorting outputs together) if the interface control can be guaranteed to set the outputs to the same level. Although the sink output is relatively weak (typically 750 $\Omega$ ), that resistance is low enough to dissipate 530mW when shorted to an opposite level output at a V<sub>BB</sub> voltage of only 20V. A safe way to parallel outputs is to use diodes to prevent the outputs from sinking current (Figure 4). Because the outputs cannot sink current from the VFD tube, an external discharge resistor, R, is required. For static tubes, R can be a large value such as  $100k\Omega$ . For multiplexed tubes, the value of the resistor can be determined by the load capacitance and timing characteristics required. Resistor RI discharges tube capacitance C to 10% of the initial voltage in 2.3 x RC seconds. So, for example, a  $15k\Omega$  value for R discharges 100pF tube grid or anode from 40V to 4V in 3.5µs, but draws an additional 2.7mA from the driver when either output is high.

#### **Power Dissipation**

Take care to ensure that the maximum package dissipation ratings for the chosen package are not exceeded. Over dissipation is unlikely to be an issue when driving static tubes, but the peak currents are usually

Figure 4. Paralleling Outputs

higher for multiplexed tubes. When using multiple driver devices, try to share the average dissipation evenly between the drivers.

Determine the power dissipation (PD) for the MAX6920 for static tube drivers with the following equation:

$$P_D = (V_{CC} \times I_{CC}) + (V_{BB} \times I_{BB}) + ((V_{BB} - V_H) \times I_{ANODE} \times A))$$

where:

A = number of anodes driven (a MAX6920 can drive a maximum of 12).

$I_{ANODF}$  = maximum anode current.

(VBB - VH) is the output voltage drop at the given maximum anode current IOUT.

A static tube dissipation example follows:

$$V_{CC}$$

= 5V ±5%,  $V_{BB}$  = 10V to 18V, A = 12,  $I_{OUT}$  = 2mA

$P_D$  = (5.25V x 0.7mA) + (18V x 0.9mA) + ((2.5V x 2mA/25mA) x 2mA x 12) = 24.7mW

Determine the power dissipation (PD) for the MAX6920 for multiplex tube drivers with the following equation:

$$P_D = (V_{CC} \times I_{CC}) + (V_{BB} \times I_{BB}) + ((V_{BB} - V_H) \times I_{ANODE} \times A) + ((V_{BB} - V_H) \times I_{GRID}))$$

where:

A = number of anodes driven

G = number of grids driven

I<sub>ANODE</sub> = maximum anode current

I<sub>GRID</sub> = maximum grid current

The calculation presumes all anodes are on but only one grid is on. The calculated PD is the worst case, presuming one digit is always being driven with all its anodes lit. Actual PD can be estimated by multiplying this PD figure by the actual tube drive duty cycle, taking into account interdigit blanking and any PWM intensity control.

A multiplexed tube dissipation example follows:

$$V_{CC}$$

= 5V ±5%,  $V_{BB}$  = 36V to 42V, A = 6, G = 6,  $I_{ANODE}$  = 0.4mA,  $I_{GRID}$  = 24mA

$$P_D = (5.25V \times 0.7mA) + (42V \times 0.9mA) + ((2.5V \times 0.4mA/25mA) \times 0.4mA \times 6) + ((2.5V \times 24mA/25mA) \times 24mA) = 99mW$$

Thus, for a 20-pin wide SO package ( $T_{JA} = 1/0.01 =$ +100°C/W from Absolute Maximum Ratings), the maximum allowed ambient temperature TA is given by:

$$T_{J(MAX)} = T_A + (PD \times T_{JA}) = +150^{\circ}C = T_A + (0.099 \times +100^{\circ}C/W)$$

So  $T_A = +140$ °C.

This means that the driver can be operated in this application up to the MAX6920's +125°C maximum operating temperature.

#### **Power-Supply Considerations**

The MAX6920 operates with multiple power-supply voltages. Bypass the  $V_{CC}$  and  $V_{BB}$  power-supply pins to GND with a 0.1µF capacitor close to the device. For multiplex applications, it may be necessary to add an additional 1µF bulk electrolytic capacitor, or greater, to the  $V_{BB}$  supply.

#### **Power-Supply Sequencing**

The order of the power-supply sequencing is not important. The MAX6920 will not be damaged if either  $V_{CC}$  or  $V_{BB}$  is grounded (or maintained at any other voltage below the data sheet minimum), while the other supply is maintained up to its maximum rating. However, as with any CMOS device, do not drive the MAX6920's logic inputs if the logic supply  $V_{CC}$  is not operational because the input protection diodes clamp the signals.

## **Chip Information**

PROCESS: BICMOS

### **Typical Application Circuit**

#### **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE | PACKAGE | DOCUMENT | LAND        |

|---------|---------|----------|-------------|

| TYPE    | CODE    | NO.      | PATTERN NO. |

| 20 SO   | W20-2   | 21-0042  | 90-0108     |

www.maximintegrated.com Maxim Integrated | 9

## 12-Output, 76V, Serial-Interfaced VFD Tube Driver

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                  | PAGES<br>CHANGED |

|--------------------|------------------|----------------------------------------------|------------------|

| 0                  | 10/03            | Initial Release                              | _                |

| 1                  | 8/14             | Removed automotive reference from data sheet | 1                |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## Maxim Integrated:

MAX6920ATP+ MAX6920ATP+T MAX6920AWP+ MAX6920AWP+T