## **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| Supply Voltage (Pin 8 to Pin 4)            | 36V  |

|--------------------------------------------|------|

| Output to Negative Supply (Pin 7 to Pin 4) |      |

| LT1011AC, LT1011C                          | 40V  |

| LT1011AI, LT1011I                          | 40V  |

| LT1011AM, LT1011M (OBSOLETE)               | 50V  |

| Ground to Negative Supply (Pin 1 to Pin 4) | 30V  |

| Differential Input Voltage                 | ±36V |

| Voltage at STROBE Pin (Pin 6 to Pin 8)     | 5V   |

| Input Voltage (Note 2)                | .Equal to Supplies |

|---------------------------------------|--------------------|

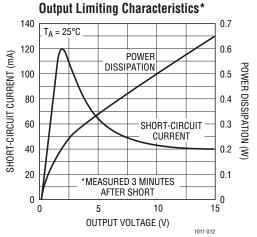

| Output Short-Circuit Duration         | 10 sec             |

| Operating Temperature Range (Note 3)  | )                  |

| LT1011AC, LT1011C                     | 0°C to 70°C        |

| LT1011AI, LT1011I                     | 40°C to 85°C       |

| LT1011AM, LT1011M (OBSOLETE)          | –55°C to 125°C     |

| Storage Temperature Range             | –65°C to 150°C     |

| Lead Temperature (Soldering, 10 sec). | 300°C              |

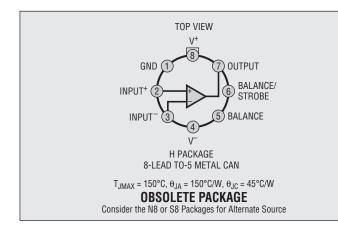

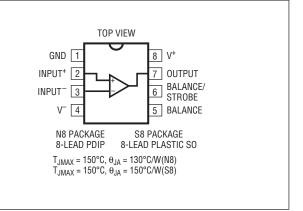

## PIN CONFIGURATION

## **ORDER INFORMATION**

| LEAD FREE FINISH  | TAPE AND REEL    | PART MARKING* | PACKAGE DESCRIPTION   | TEMPERATURE RANGE |  |  |  |

|-------------------|------------------|---------------|-----------------------|-------------------|--|--|--|

| LT1011ACN8#PBF    | N/A              | LT1011        | 8-Lead Plastic DIP    | 0°C to 70°C       |  |  |  |

| LT1011CN8#PBF     | N/A              | LT1011        | 8-Lead Plastic DIP    | 0°C to 70°C       |  |  |  |

| LT1011AIS8#PBF    | LT1011AIS8#TRPBF | 1011AI        | 8-Lead Plastic SO     | -40°C to 85°C     |  |  |  |

| LT1011CS8#PBF     | LT1011CS8#TRPBF  | 1011          | 8-Lead Plastic SO     | 0°C to 70°C       |  |  |  |

| LT1011IS8#PBF     | LT1011IS8#TRPBF  | 10111         | 8-Lead Plastic SO     | -40°C to 85°C     |  |  |  |

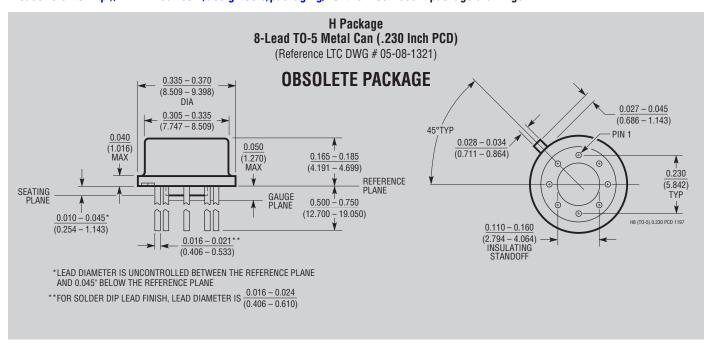

| OBSOLETE PACKAGES |                  |               |                       |                   |  |  |  |

| LT1011ACH#PBF     | N/A              |               | 8-Lead TO-5 Metal Can | −55°C to 125°C    |  |  |  |

| LT1011CH#PBF      | N/A              |               | 8-Lead TO-5 Metal Can | −55°C to 125°C    |  |  |  |

| LT1011AMH#PBF     | N/A              |               | 8-Lead TO-5 Metal Can | −55°C to 125°C    |  |  |  |

| LT1011MH#PBF      | N/A              |               | 8-Lead TO-5 Metal Can | −55°C to 125°C    |  |  |  |

| LT1011ACJ8#PBF    | N/A              |               | 8-Lead CERDIP         | −55°C to 125°C    |  |  |  |

| LT1011CJ8#PBF     | N/A              |               | 8-Lead CERDIP         | −55°C to 125°C    |  |  |  |

| LT1011AMJ8#PBF    | N/A              |               | 8-Lead CERDIP         | −55°C to 125°C    |  |  |  |

| LT1011MJ8#PBF     | N/A              |               | 8-Lead CERDIP         | −55°C to 125°C    |  |  |  |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on nonstandard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/ For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_S = \pm 15V$ , $V_{CM} = 0V$ , $R_S = 0\Omega$ , $V_{GND} = -15V$ , output at pin 7 unless otherwise noted.

|                                  |                                                     |                                                                                                                                            |   | LT1011AC/AI/AM |                     | I/AM               | LT1011C/I/M  |                     |                    |          |

|----------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---|----------------|---------------------|--------------------|--------------|---------------------|--------------------|----------|

| SYMBOL                           | PARAMETER                                           | CONDITIONS                                                                                                                                 |   | MIN            | TYP                 | MAX                | MIN          | TYP                 | MAX                | UNITS    |

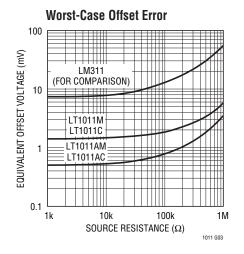

| V <sub>OS</sub>                  | Input Offset Voltage                                | (Note 4)                                                                                                                                   | • |                | 0.3                 | 0.5<br>1           |              | 0.6                 | 1.5<br>3           | mV<br>mV |

|                                  | *Input Offset Voltage                               | R <sub>S</sub> ≤ 50k (Note 5)                                                                                                              | • |                |                     | 0.75<br>1.5        |              |                     | 2 3                | mV<br>mV |

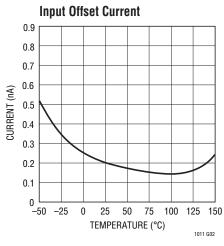

| I <sub>OS</sub>                  | *Input Offset Current                               | (Note 5)                                                                                                                                   | • |                | 0.2                 | 3<br>5             |              | 0.2                 | 4<br>6             | nA<br>nA |

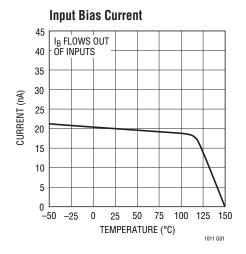

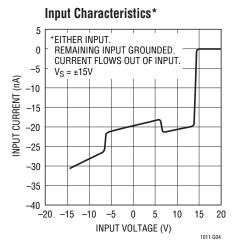

| I <sub>B</sub>                   | Input Bias Current                                  | (Note 4)                                                                                                                                   |   |                | 15                  | 25                 |              | 20                  | 50                 | nA       |

|                                  | *Input Bias Current                                 | (Note 5)                                                                                                                                   | • |                | 20                  | 35<br>50           |              | 25                  | 65<br>80           | nA<br>nA |

| $\frac{\Delta V_{OS}}{\Delta T}$ | Input Offset Voltage Drift<br>(Note 6)              | $T_{MIN} \le T \le T_{MAX}$                                                                                                                | • |                | 4                   | 15                 |              | 4                   | 25                 | μV/°C    |

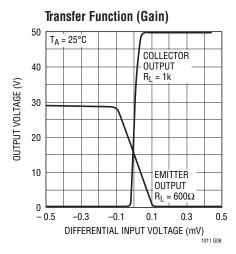

| A <sub>VOL</sub>                 | *Large-Signal Voltage Gain                          | $R_L = 1k$ Connected to 15V,<br>-10V $\leq$ V <sub>OUT</sub> $\leq$ 14.5V                                                                  |   | 200            | 500                 |                    | 200          | 500                 |                    | V/mV     |

|                                  |                                                     | $R_L = 500\Omega$ Connected to 5V,<br>$V_S = $ Single 5V, $V_{GND} = $ 0V,<br>$0.5V \le V_{OUT} \le 4.5V$                                  |   | 50             | 300                 |                    | 50           | 300                 |                    | V/mV     |

| CMRR                             | Common Mode Rejection Ratio                         |                                                                                                                                            |   | 94             | 115                 |                    | 90           | 115                 |                    | dB       |

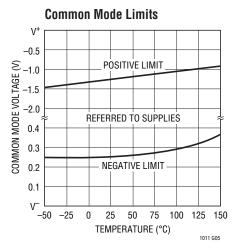

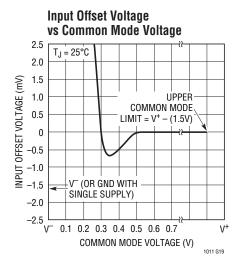

|                                  | *Input Voltage Range (Note 9)                       | $V_S = \pm 15V$<br>$V_S = \text{Single 5V}$                                                                                                | • | -14.5<br>0.5   |                     | 13<br>3            | -14.5<br>0.5 |                     | 13<br>3            | V        |

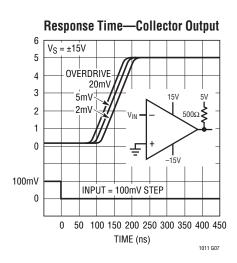

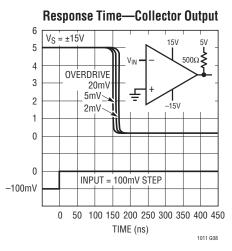

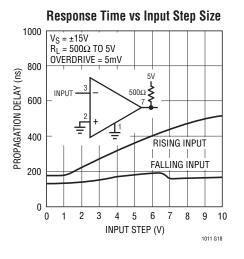

| $t_D$                            | *Response Time                                      | (Note 7)                                                                                                                                   |   |                | 150                 | 250                |              | 150                 | 250                | ns       |

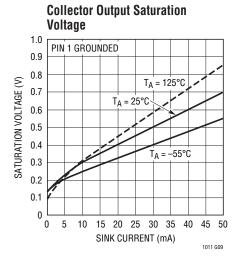

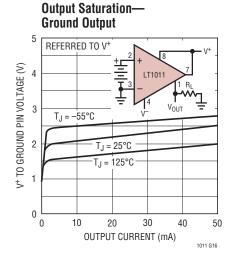

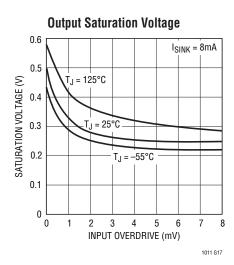

| V <sub>OL</sub>                  | *Output Saturation Voltage,<br>V <sub>GND</sub> = 0 | $V_{IN} = -5mV$ , $I_{SINK} = 8mA$ , $T_{J} \le 100^{\circ}C$<br>$V_{IN} = -5mV$ , $I_{SINK} = 8mA$<br>$V_{IN} = -5mV$ , $I_{SINK} = 50mA$ | • |                | 0.25<br>0.25<br>0.7 | 0.4<br>0.45<br>1.5 |              | 0.25<br>0.25<br>0.7 | 0.4<br>0.45<br>1.5 | V<br>V   |

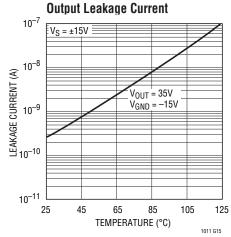

|                                  | *Output Leakage Current                             | $V_{IN} = 5mV$ , $V_{GND} = -15V$ , $V_{OUT} = 20V$                                                                                        | • |                | 0.2                 | 10<br>500          |              | 0.2                 | 10<br>500          | nA<br>nA |

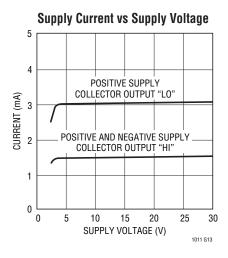

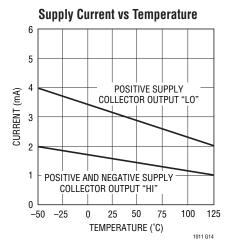

|                                  | *Positive Supply Current                            | V <sub>GND</sub> = 0                                                                                                                       |   |                | 3.2                 | 4                  |              | 3.2                 | 4                  | mA       |

|                                  | *Negative Supply Current                            | V <sub>GND</sub> = 0                                                                                                                       |   |                | 1.7                 | 2.5                |              | 1.7                 | 2.5                | mA       |

|                                  | *Strobe Current (Note 8)                            |                                                                                                                                            |   | 500            |                     |                    | 500          |                     |                    | μА       |

|                                  | Input Capacitance                                   |                                                                                                                                            |   |                | 6                   |                    |              | 6                   |                    | pF       |

<sup>\*</sup>Indicates parameters which are guaranteed for all supply voltages, including a single 5V supply. See Note 5.

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** Inputs may be clamped to supplies with diodes so that maximum input voltage actually exceeds supply voltage by one diode drop. See Input Protection in the Applications Information section.

Note 3:  $T_{JMAX} = 150$ °C.

**Note 4:** Output is sinking 1.5mA with  $V_{OUT} = 0V$ .

**Note 5:** These specifications apply for all supply voltages from a single 5V to  $\pm 15$ V, the entire input voltage range, and for both high and low output states. The high state is  $I_{SINK}=100\mu A$ ,  $V_{OUT}=(V^+-1V)$  and the low state is  $I_{SINK}=8mA$ ,  $V_{OUT}=0.8$ V. Therefore, this specification

defines a worst-case error band that includes effects due to common mode signals, voltage gain and output load.

**Note 6:** Drift is calculated by dividing the offset voltage difference measured at min and max temperatures by the temperature difference.

**Note 7:** Response time is measured with a 100mV step and 5mV overdrive. The output load is a  $500\Omega$  resistor tied to 5V. Time measurement is taken when the output crosses 1.4V.

**Note 8:** Do not short the STROBE pin to ground. It should be current driven at 3mA to 5mA for the shortest strobe time. Currents as low as  $500\mu\text{A}$  will strobe the LT1011A if speed is not important. External leakage on the STROBE pin in excess of  $0.2\mu\text{A}$  when the strobe is "off" can cause offset voltage shifts.

Note 9: See graph "Input Offset Voltage vs Common Mode Voltage."

TECHNOLOGY TECHNOLOGY

## TYPICAL PERFORMANCE CHARACTERISTICS

## TYPICAL PERFORMANCE CHARACTERISTICS

1011 G10

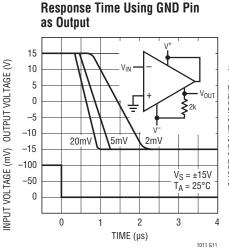

**Response Time Using GND Pin** as Output 15 5mV 20mV INPUT VOLTAGE (mV) OUTPUT VOLTAGE (V) 10 5 0 -5 -10 -15 0 -50  $V_S = \pm 15V$ -100  $T_A = 25^{\circ}C$ 3 0 2

TIME (µs)

## TYPICAL PERFORMANCE CHARACTERISTICS

## PIN FUNCTIONS

GND (PIN 1): Ground.

INPUT+ (PIN 2): Non-Inverting Input of Comparator

INPUT (PIN 3): Inverting Input of Comparator

V- (PIN 4): Negative Supply Voltage

OUT (PIN 7): Open-Collector Output of Comparator

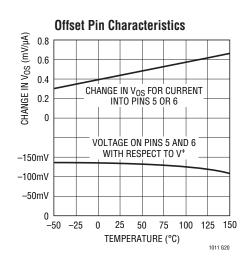

**BALANCE (PIN 5):** Balance Input. This input can be used to adjust the input voltage offset or to add hysteresis. If offset balancing or hysteresis is not used, the BALANCE pins should be connected together with a 0.1µF capacitor.

BALANCE/STROBE (PIN 6): Strobe Input Pin. Using this pin, the output transistor can be forced to an "off" state, giving a "hi" output at the collector (Pin 7). This input can be used to adjust the input voltage offset or used to add hysteresis. If offset balancing or hysteresis is not used, the BALANCE pins should be connected together with a 0.1µF capacitor.

V+ (PIN 8): Positive Supply Voltage

#### **Preventing Oscillation Problems**

Oscillation problems in comparators are nearly always caused by stray capacitance between the output and inputs or between the output and other sensitive pins on the comparator. This is especially true with high gain bandwidth comparators like the LT1011, which are designed for fast switching with millivolt input signals. The gain bandwidth product of the LT1011 is over 10GHz. Oscillation problems tend to occur at frequencies around 5MHz, where the LT1011 has a gain of ≈2000. This implies that attenuation of output signals must be at least 2000:1 at 5MHz as measured at the inputs. If the source impedance is  $1k\Omega$ , the effective stray capacitance between output and input must have a reactance of more than  $(2000)(1k\Omega) =$  $2M\Omega$ , or less than 0.02pF. The actual interlead capacitance between input and output pins on the LT1011 is less than 0.002pF when cut to printed circuit mount length. Additional stray capacitance due to printed circuit traces must be minimized by routing the output trace directly away from input lines and, if possible, running ground traces next to input traces to provide shielding. Additional steps to ensure oscillation-free operation are:

- 1. Bypass the STROBE/BALANCE pins with a 0.01µF capacitor connected from Pin 5 to Pin 6. This eliminates stray capacitive feedback from the output to the BALANCE pins, which are nearly as sensitive as the inputs.

- Bypass the negative supply (Pin 4) with a 0.1μF ceramic capacitor close to the comparator. 0.1μF can also be used for the positive supply (Pin 8) if the pull-up load is tied to a separate supply. When the pull-up load is tied directly to Pin 8, use a 2μF solid tantalum bypass capacitor.

- 3. Bypass any slow moving or DC input with a capacitor (≥0.01µF) close to the comparator to reduce high frequency source impedance.

- 4. Keep resistive source impedance as low as possible. If a resistor is added in series with one input to balance source impedances for DC accuracy, bypass it with a capacitor. The low input bias current of the LT1011 usually eliminates any need for source resistance balancing. A  $5k\Omega$  imbalance, for instance, will create only 0.25mV DC offset.

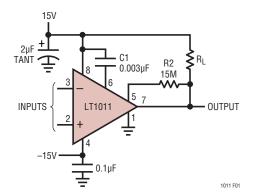

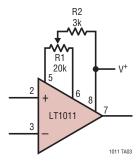

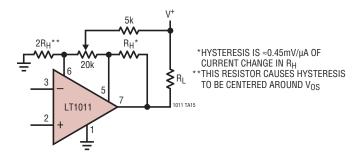

- 5. Use hysteresis. This consists of shifting the input offset voltage of the comparator when the output changes state. Hysteresis forces the comparator to move quickly through its linear region, eliminating oscillations by "overdriving" the comparator under all input conditions. Hysteresis may be either AC or DC. AC techniques do not shift the apparent offset voltage of the comparator, but require a *minimum* input signal slew rate to be effective. DC hysteresis works for all input slew rates, but creates a shift in offset voltage dependent on the previous condition of the input signal. The circuit shown in Figure 1 is an excellent compromise between AC and DC hysteresis.

Figure 1. Comparator with Hysteresis

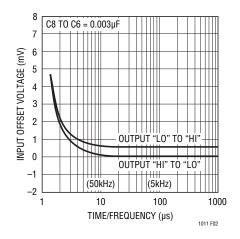

This circuit is especially useful for general purpose comparator applications because it does not force any signals directly back onto the input signal source. Instead, it takes advantage of the unique properties of the BALANCE pins to provide extremely fast, clean output switching even with low frequency input signals in the millivolt range. The 0.003µF capacitor from Pin 6 to Pin 8 generates AC hysteresis because the voltage on the BALANCE pins shifts slightly, depending on the state of the output. Both pins move about 4mV. If one pin (6) is bypassed, AC hysteresis is created. It is only a few millivolts referred to the inputs, but is sufficient to switch the output at nearly the maximum speed of which the comparator is capable. To prevent problems from low values of input slew rate, a slight amount of DC hysteresis is also used. The sensitivity of the BALANCE pins to current is about 0.5mV input referred offset for each microampere of BALANCE pin current. The 15M resistor tied from OUTPUT to Pin 5 generates 0.5mV DC hysteresis. The combination of AC and DC hysteresis creates clean oscillation-free switching with very small input errors. Figure 2 plots input referred error versus switching frequency for the circuit as shown.

Note that at low frequencies, the error is simply the DC hysteresis, while at high frequencies, an additional error is created by the AC hysteresis. The high frequency error can be reduced by reducing  $C_H$ , but lower values may not provide clean switching with very low slew rate input signals.

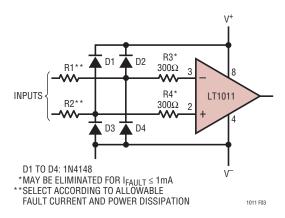

#### **Input Protection**

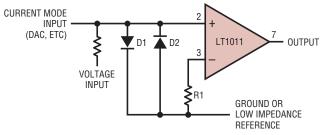

The inputs to the LT1011 are particularly suited to general purpose comparator applications because large differential and/or common mode voltages can be tolerated without damage to the comparator. Either or both inputs can be raised 40V above the negative supply, *independent of the positive supply voltage*. Internal forward biased diodes will conduct when the inputs are taken below the negative supply. In this condition, input current must be limited to 1mA. If very large (fault) input voltages must be accommodated, series resistors and clamp diodes should be used (see Figure 3).

Figure 2. Input Offset Voltage vs Time to Last Transition

Figure 3. Limiting Fault Input Currents

The input resistors should limit fault current to a reasonable value (0.1mA to 20mA). Power dissipation in the resistors must be considered for continuous faults, especially when the LT1011 supplies are off. One final caution: lightly loaded supplies may be forced to higher voltages by large fault currents flowing through D1-D4.

R3 and R4 limit input current to the LT1011 to less than 1mA when the input signals are held below  $V^-$ . They may be eliminated if R1 and R2 are large enough to limit fault current to less than 1mA.

#### **Input Slew Rate Limitations**

The response time of a comparator is typically measured with a 100mV step and a 5mV to 10mV overdrive. Unfortunately, this does not simulate many real world situations where the step size is typically much larger and overdrive can be significantly less. In the case of the LT1011, step size is important because the slew rate of internal nodes will limit response time for input step sizes larger than 1V. At 5V step size, for instance, response time increases from 150ns to 360ns. See the curve "Response Time vs Input Step Size for more detail.

If response time is critical and large input signals are expected, clamp diodes across the inputs are recommended. The slew rate limitation can also affect performance when differential input voltage is low, but both inputs must slew quickly. Maximum suggested common mode slew rate is  $10V/\mu s$ .

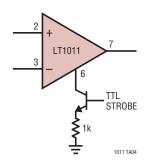

### Strobing

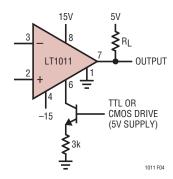

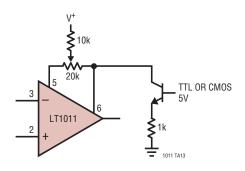

The LT1011 can be strobed by pulling current out of the STROBE pin. The output transistor is forced to an "off" state, giving a "hi" output at the collector (Pin 7). Currents as low as 250µA will cause strobing, but at low strobe currents, strobe delay will be 200ns to 300ns. If strobe current is increased to 3mA, strobe delay drops to about 60ns. The voltage at the STROBE pin is about 150mV below V+ at zero strobe current and about 2V below V+ for 3mA strobe current. Do not ground the STROBE pin. It must be current driven. Figure 4 shows a typical strobe circuit.

Note that there is no bypass capacitor between Pins 5 and 6. This maximizes strobe speed, but leaves the comparator more sensitive to oscillation problems for slow, low

Figure 4. Typical Strobe Circuit

level inputs. A 1pF capacitor between the output and Pin 5 will greatly reduce oscillation problems without reducing strobe speed.

DC hysteresis can also be added by placing a resistor from the output to Pin 5. See step 5 under "Preventing Oscillation Problems."

The pin (6) used for strobing is also one of the offset adjust pins. Current flow into or out of Pin 6 must be kept very low ( $<0.2\mu A$ ) when not strobing to prevent input offset voltage shifts.

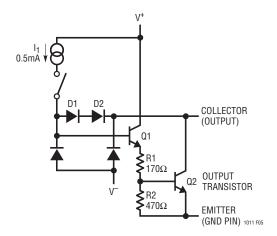

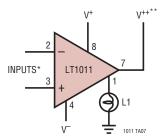

#### **Output Transistor**

The LT1011 output transistor is truly floating in the sense that no current flows into or out of either the collector or emitter when the transistor is in the "off" state. The equivalent circuit is shown in Figure 5.

Figure 5. Output Transistor Circuitry

LINEAR

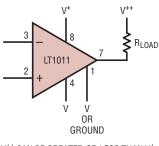

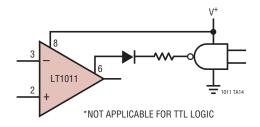

In the "off" state, I<sub>1</sub> is switched off and both Q1 and Q2 turn off. The collector of Q2 can be now held at any voltage above V<sup>-</sup> without conducting current, including voltages above the positive supply level. Maximum voltage above  $V^-$  is 50V for the LT1011M and 40V for the LT1011C/I. The emitter can be held at any voltage between V+ and V<sup>-</sup> as long as it is negative with respect to the collector.

In the "on" state,  $I_1$  is connected, turning on Q1 and Q2. Diodes D1 and D2 prevent deep saturation of Q2 to improve speed and also limit the drive current of Q1. The R1/R2 divider sets the saturation voltage of Q2 and provides turnoff drive. Either the collector or emitter pin can be held at a voltage between V<sup>+</sup> and V<sup>-</sup>. This allows the remaining pin to drive the load. In typical applications, the emitter is connected to V<sup>-</sup> or ground and the collector drives a load tied to V<sup>+</sup> or a separate positive supply.

When the emitter is used as the output, the collector is typically tied to V<sup>+</sup> and the load is connected to ground or V<sup>-</sup>. Note that the emitter output is phase reversed with respect to the collector output so that the "+" and "-" input designations must be reversed. When the collector is tied to V<sup>+</sup>, the voltage at the emitter in the "on" state is about 2V below V+ (see curves).

#### **Input Signal Range**

The common mode input voltage range of the LT1011 is about 300mV above the negative supply and 1.5V below the positive supply, independent of the actual supply voltages (see curve in the Typical Performance Characteristics). This is the voltage range over which the output will respond correctly when the common mode voltage is applied to one input and a higher or lower signal is applied to the remaining input. If one input is inside the common mode range and one is outside, the output will be correct. If the inputs are outside the common mode range in opposite directions, the output will still be correct. If both inputs are outside the common mode range in the same direction, the output will not respond to the differential input; for temperatures of 25°C and above, the output will remain unconditionally high (collector output), for temperatures below 25°C, the output becomes undefined.

## TYPICAL APPLICATIONS

#### **Offset Balancing**

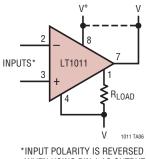

#### **Driving Load Referenced** to Positive Supply

V<sup>++</sup> CAN BE GREATER OR LESS THAN V<sup>+</sup>

#### **Driving Load Referenced** to Negative Supply

WHEN USING PIN 1 AS OUTPUT

#### **Strobing**

NOTE: DO NOT GROUND STROBE PIN

#### **Driving Ground Referred Load**

\*INPUT POLARITY IS REVERSED WHEN USING PIN 1 AS OUTPUT \*\*V<sup>++</sup> MAY BE ANY VOLTAGE ABOVE V<sup>-</sup>. PIN 1 SWINGS TO WITHIN ≈2V OF V<sup>++</sup>

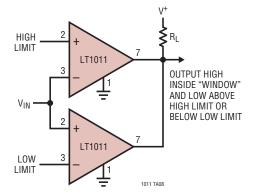

#### **Window Detector**

#### Using Clamp Diodes to Improve Frequency Response\*

\*SEE CURVE, "RESPONSE TIME VS INPUT STEP SIZE" 1011 TAG

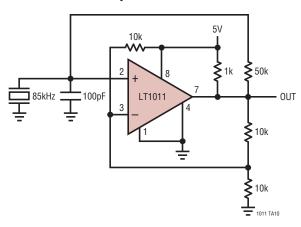

#### **Crystal Oscillator**

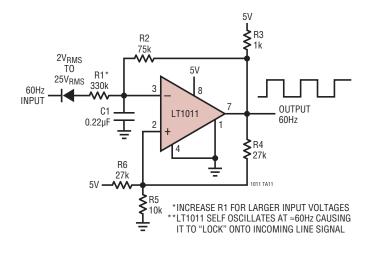

#### Noise Immune 60Hz Line Sync\*\*

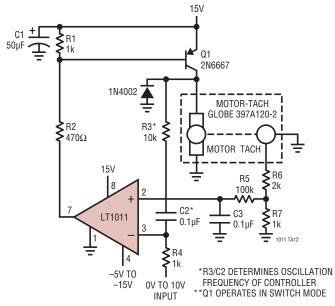

#### High Efficiency\*\* Motor Speed Controller

#### **Combining Offset Adjust and Strobe**

#### **Combining Offset Adjustment and Hystersis**

#### Direct Strobe Drive When CMOS\* Logic Uses Same V+ Supply as LT1011

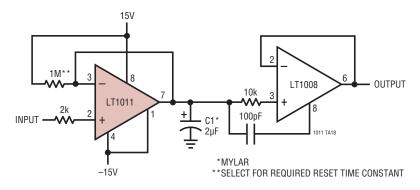

#### **Positive Peak Detector**

- \*\*SELECT FOR REQUIRED RESET TIME CONSTANT

- \*\*\*INPUT POLARITY IS REVERSED WHEN USING PIN 1 AS OUTPUT

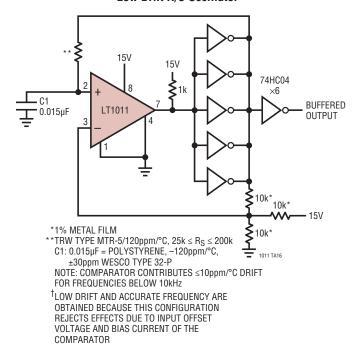

#### Low Drift R/C Oscillator†

#### **Negative Peak Detector**

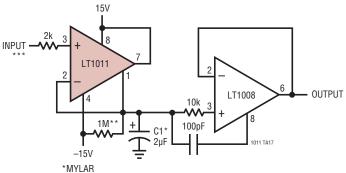

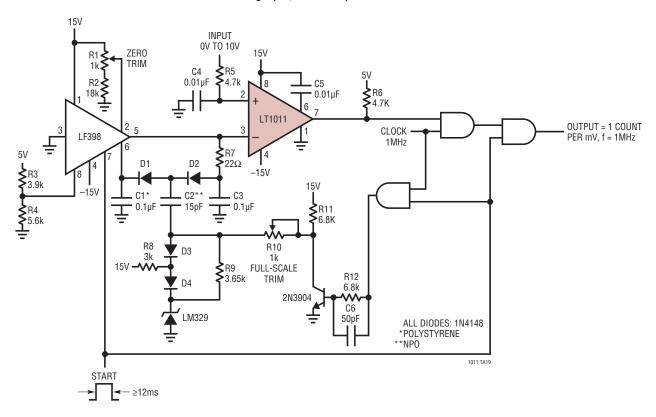

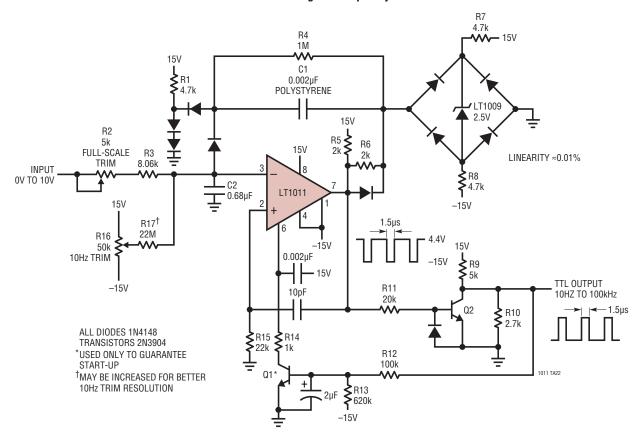

#### 4-Digit (10,000 Count) A/D Converter

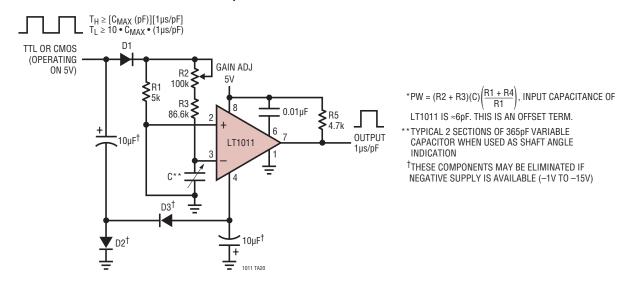

#### **Capacitance to Pulse Width Converter**

LINEAR TECHNOLOGY

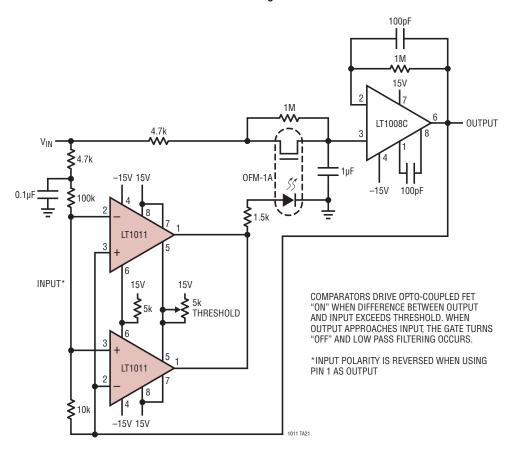

#### **Fast Settling Filter**

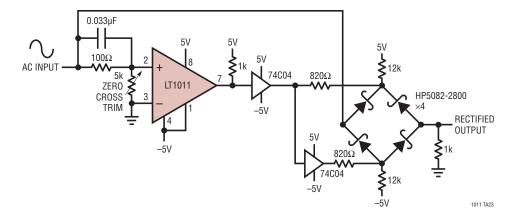

#### 100kHz Precision Rectifier

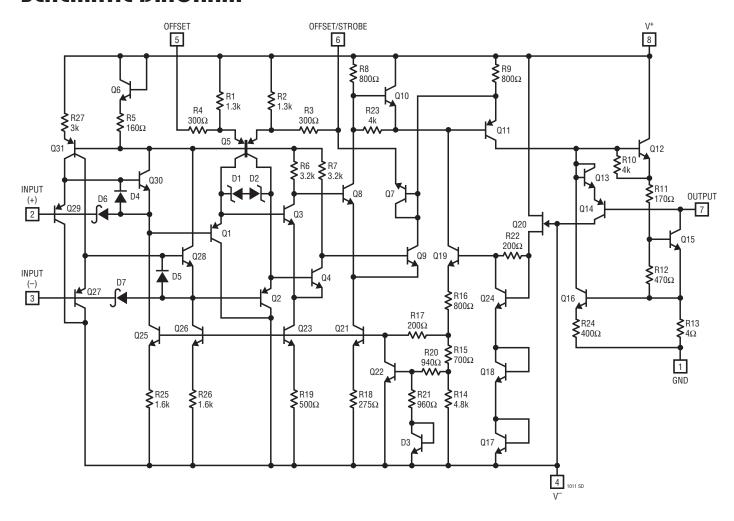

## **SCHEMATIC DIAGRAM**

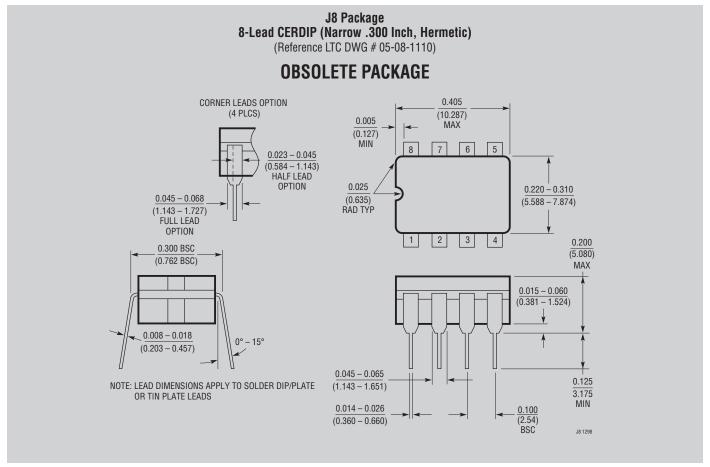

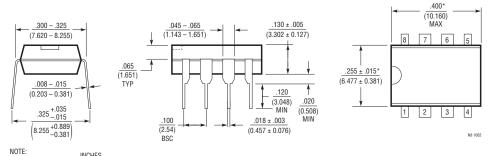

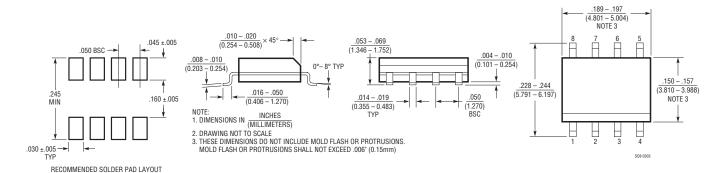

## PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

## PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

#### N8 Package 8-Lead PDIP (Narrow .300 Inch)

(Reference LTC DWG # 05-08-1510)

NOTE:

1. DIMENSIONS ARE MILLIMETERS

\*\*THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED .010 INCH (0.254mm)

#### \$8 Package 8-Lead Plastic Small Outline (Narrow .150 Inch)

(Reference LTC DWG # 05-08-1610)

# **REVISION HISTORY** (Revision history begins at Rev D)

| REV | DATE  | DESCRIPTION                                                                                                                                                                                                | PAGE NUMBER |

|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| D   | 10/12 | Update to Product Description                                                                                                                                                                              | 1           |

|     |       | Addition of Order Information                                                                                                                                                                              | 2, 3        |

|     |       | Addition of Pin Function Information                                                                                                                                                                       | 7           |

|     |       | Correction to Positive Peak Detector Circuit                                                                                                                                                               | 13          |

| Е   | 4/13  | Correction to Pin Function descriptions                                                                                                                                                                    | 2, 7        |

|     |       | Correction to Order Information and Obsolete Packages                                                                                                                                                      | 3           |

|     |       | Correction to Graphs: Response Time—Collector Output – high to low Response Time Using GND Pin as Output – low to high Response Time Using GND Pin as Output – high to low Output Saturation—Ground Output | 5, 6        |

|     |       | Correction to input pin polarity                                                                                                                                                                           | 10, 13, 15  |

#### 10Hz to 100kHz Voltage to Frequency Converter

## **RELATED PARTS**

| PART NUMBER | DESCRIPTION                                  | COMMENTS                            |

|-------------|----------------------------------------------|-------------------------------------|

| LT1016      | UltraFast™ Precision Comparator              | Industry Standard 10ns Comparator   |

| LT1116      | 12ns Single Supply Ground-Sensing Comparator | Single Supply Version of the LT1016 |

| LT1394      | UltraFast Single Supply Comparator           | 7ns, 6mA Single Supply Comparator   |

| LT1671      | 60ns, Low Power Comparator                   | 450µA Single Supply Comparator      |

UltraFast is a trademark of Linear Technology Corporation.

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## **Analog Devices Inc.:**

<u>LT1011CS8#TRPBF</u> <u>LT1011ACN8#PBF</u> <u>LT1011IS8#TRPBF</u> <u>LT1011AIS8#PBF</u> <u>LT1011CS8#PBF</u> <u>LT1011IS8#PBF</u> <u>LT1011IS8#PBF</u>