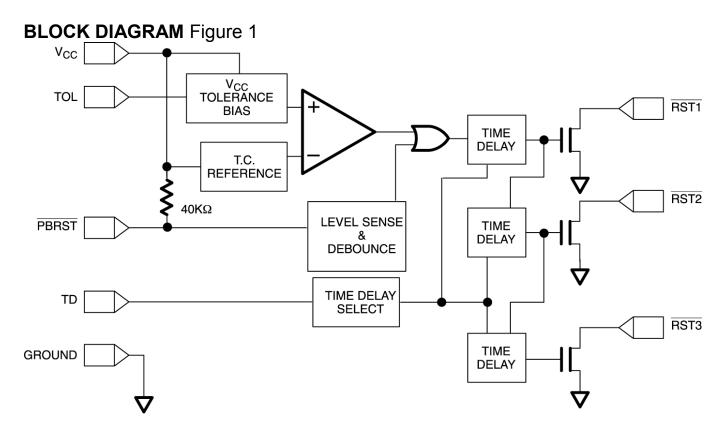

#### OPERATION — POWER MONITOR

The DS1830 provides the functions of detecting out-of-tolerance conditions on a power supply and warning a processor based system of impending power failure. When  $V_{CC}$  is detected as out-of-tolerance all reset outputs will be forced active. When  $V_{CC}$  returns to a valid state,  $\overline{\text{RST1}}$  will remain active for period of time based on the condition of the TD input. Reset outputs  $\overline{\text{RST2}}$  and  $\overline{\text{RST3}}$  follow  $\overline{\text{RST1}}$ , each one at the proper delays for the condition of the TD input. All resets will remain in the inactive state (high) until the next  $V_{CC}$  out-of-tolerance condition or pushbutton reset. On power-up all resets are kept active for an appropriate period determined by the status of the TD input after the power supply inputs have reached the selected tolerance. This allows the power supply and system power to stabilize before the reset sequences are released.

#### **OPERATION** — TOLERANCE SELECT

The DS1830/A provides a TOL input for individual customization of the DS1830x to specific application requirements (see Table 1). For the tolerance selection, see Table 1 below. The TOL input is only sampled while  $V_{CC}$  is below the lowest potential trip value and can not be changed after the  $V_{CC}$  voltage exceeds the lowest potential trip value.

| $T \cap$ | I TC |       |        | CLI          | ГСТ |          |

|----------|------|-------|--------|--------------|-----|----------|

| TO       |      | и ека | N( . F | > F I        |     | Table 1  |

| -        |      |       |        | $\mathbf{v}$ | -   | I abic i |

| TOL            | 5V (DS1830) | 3.3V (DS1830A) |

|----------------|-------------|----------------|

| $V_{CC}$       | 5%          | 5%             |

| GND            | 10%         | 10%            |

| OPEN<br>(N.C.) | 15%         | 20%            |

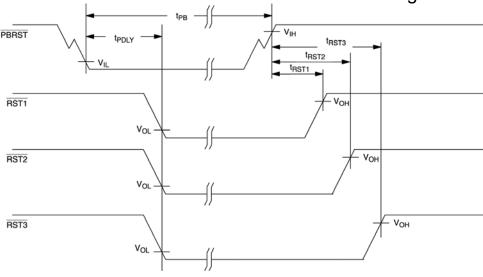

#### **OPERATION — PUSHBUTTON RESET**

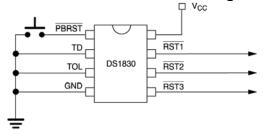

The DS1830 provides a pushbutton switch for manual reset control. When any of the DS1830/A resets are not active (low) a reset cycle can be initiated by a pushbutton reset. The pushbutton reset is generated by pulling the PBRST pin low for at least 1ms. When the push-button is held low all resets are forced active. The reset will remain active until the pushbutton input is released and then will start a sequenced time-out based on the condition of the TD input. The Pushbutton input is pulled high through an internal  $40k\Omega$  pull-up resistor and debounced via internal circuitry. See Figure 2 for an application example and Figure 3 for the timing diagram.

### **PUSHBUTTON RESET** Figure 2

### TIMING DIAGRAM — PUSHBUTTON RESET Figure 3

#### **OPERATION — TIME DELAY SELECT**

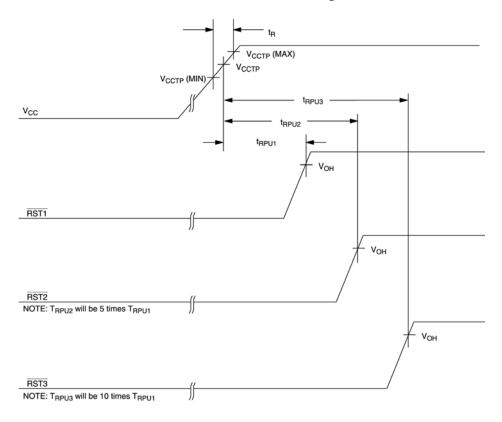

The DS1830 provides an input to select three time delay characteristics for the reset outputs. The TD input has 3 states high ( $V_{CC}$ ), low (ground) and no connect (N.C.). Table 2 details the minimum timing based on the state of the TD input. If the TD input is connected to ground;  $\overline{\text{RST1}}$  will have a minimum time delay of 10 ms after  $V_{CC}$  is in tolerance. If the TD input is floated;  $\overline{\text{RST1}}$  will have a minimum time delay of 20 ms after  $V_{CC}$  is in tolerance. If the TD input is connected to  $V_{CC}$ ,  $\overline{\text{RST1}}$  will have a minimum time delay of 50 ms after  $V_{CC}$  is in tolerance. An oscillator and clock chain generate the reset timing with each time delay based on the same device oscillator. The time delay for  $\overline{\text{RST2}}$  will be 5 times as long as  $\overline{\text{RST1}}$  and  $\overline{\text{RST3}}$  will be 10 times the duration of  $\overline{\text{RST1}}$ .

TD CONTROL MINIMUM RESET TIMING Table 2

| TD            | TRST1 | TRST2 | TRST3 |

|---------------|-------|-------|-------|

| TD = GND      | 10ms  | 50ms  | 100ms |

| TD = N.C.     | 20ms  | 100ms | 200ms |

| $TD = V_{CC}$ | 50ms  | 250ms | 500ms |

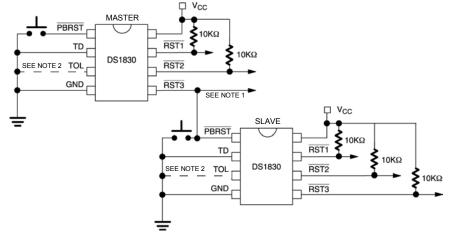

## APPLICATION DIAGRAM — CASCADE DELAY CONFIGURATIONS Figure 4

Note 1: The  $\overline{\text{RST3}}$  output tied to the pushbutton reset would be pulled to  $V_{CC}$  through the  $40k\Omega$  resistor in the pushbutton input. If a stronger pull-up is required an additional pull-up resistor could be added.

**Note 2:** When using the cascade configuration, it is important that the TOL pins of the master and the slave are configured so that the master's  $V_{CCTP}$  is greater than the slave's  $V_{CCTP}$ . This will ensure that when the master's higher  $V_{CCTP}$  is crossed, the resets will ripple through to the slave.

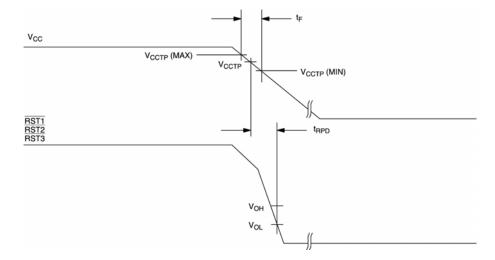

# **TIMING DIAGRAM — POWER-DOWN** Figure 5

# TIMING DIAGRAM — POWER-UP Figure 6

#### **ABSOLUTE MAXIMUM RATINGS\***

Voltage on any Pin Relative to -0.5V to +6.0V

Ground

Operating Temperature -40°C to +85°C Storage Temperature -55°C to +125°C

Soldering Temperature See IPC/JEDEC J-STD-020A

## **RECOMMENDED DC OPERATING CONDITIONS** (-40°C to +85°C)

| PARAMETER                 | SYMBOL               | MIN  | TYP | MAX            | ÚNITS | NOTES |

|---------------------------|----------------------|------|-----|----------------|-------|-------|

| Supply Voltage            | $V_{CC}$             | 1.0  |     | 5.5            | V     | 1     |

| PBRST Input High<br>Level | $ m V_{IH}$          | 2.0  |     | $V_{CC} + 0.3$ | V     |       |

| PBRST Input Low<br>Level  | $V_{_{\mathrm{IL}}}$ | -0.3 |     | +0.5           | V     |       |

<sup>\*</sup> This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

# **DC ELECTRICAL CHARACTERISTICS** (-40°C to +85°C; $V_{CC}$ = 1.0V to 5.5V)

| PARAMETER                                                     | SY                | MBOL              | MIN  | TYP      | MAX      | UNITS | NOTES |

|---------------------------------------------------------------|-------------------|-------------------|------|----------|----------|-------|-------|

| V <sub>CC</sub> Trip Point (TOL=<br>V <sub>CC</sub> ) DS1830  | V <sub>CCTP</sub> |                   | 4.50 | 4.62     | 4.74     | V     |       |

| V <sub>CC</sub> Trip Point<br>(TOL=GND) DS1830                | $V_{CCTP}$        |                   | 4.25 | 4.37     | 4.49     | V     |       |

| V <sub>CC</sub> Trip Point<br>(TOL=Open) DS1830               | ,                 | $V_{\rm CCTP}$    | 4.00 | 4.13     | 4.24     | V     |       |

| V <sub>CC</sub> Trip Point (TOL=<br>V <sub>CC</sub> ) DS1830A | ,                 | $V_{\rm CCTP}$    | 2.98 | 3.06     | 3.15     | V     |       |

| V <sub>CC</sub> Trip Point<br>(TOL=GND) DS1830A               | V <sub>CCTP</sub> |                   | 2.80 | 2.88     | 2.97     | V     |       |

| V <sub>CC</sub> Trip Point<br>(TOL=Open) DS1830A              | V <sub>CCTP</sub> |                   | 2.47 | 2.55     | 2.64     | V     |       |

| Input Leakage I <sub>IL</sub>                                 |                   | $I_{\rm IL}$      | -1.0 |          | +1.0     | μA    | 2     |

| Output Current @ 0.4V                                         | $I_{OL}$          |                   | 20   |          |          | mA    | 3     |

| Operating Current (Standby)                                   | $I_{CC}$          | DS1830<br>DS1830A |      | 18<br>10 | 35<br>25 | μА    | 4     |

# AC ELECTRICAL CHARACTERISTICS (-40°C to +85°C; $V_{CC}$ = 1.0V to 5.5V)

| PARAMETER                       | <b>SYMBOL</b>                         | MIN        | TYP        | MAX   | UNITS | NOTES |

|---------------------------------|---------------------------------------|------------|------------|-------|-------|-------|

| $\overline{PBRST} = V_{IL}$     | $t_{\scriptscriptstyle{\mathrm{PB}}}$ | $t_{PDLY}$ |            |       | ms    |       |

| RESET Active Time               | t                                     | 10         | 15         | 20    | me    |       |

| $(\overline{RST1}/TD = GND)$    | $t_{RST1}$                            | 10         | 1,3        | 20    | ms    |       |

| RESET Active Time               | +                                     | 20         | 30         | 40    | mg    |       |

| $(\overline{RST1}/TD = Float)$  | $t_{RST1}$                            | 20         | 30         | 40    | ms    |       |

| RESET Active Time               | +                                     | 50         | 75         | 100   | ma    |       |

| $(\overline{RST1}/TD = V_{CC})$ | $t_{RST1}$                            | 30         | 73         | 100   | ms    |       |

| RESET Active Time               | +                                     |            | 5x         |       | 122 G |       |

| $(\overline{RST2})$             | $t_{RST2}$                            |            | $t_{RST}1$ |       | ms    |       |

| RESET Active Time               | +                                     |            | 10x        |       | ma    |       |

| $(\overline{RST3})$             | $t_{RST3}$                            |            | $t_{RST}1$ |       | ms    |       |

| V <sub>CC</sub> Detect to RST   | $t_{ m RPD}$                          |            | 5          | 8     | μs    | 5     |

| V <sub>CC</sub> Slew Rate       | $t_{\scriptscriptstyle \mathrm{F}}$   | 20         |            |       | μs    | 6     |

| V <sub>CC</sub> Detect to RST   | t                                     | See R      | ESET A     | ctive | ms    | 7     |

|                                 | $t_{ m RPU}$                          |            | Times      | T     | 1113  | ,     |

| V <sub>CC</sub> Slew Rate       | $t_{R}$                               | 0          |            |       | ns    |       |

| PBRST Stable Low to             | t                                     | 1.0        | 1.5        | 2.0   | ms    |       |

| RST                             | $t_{ m PDLY}$                         | 1.0        | 1.5        | 2.0   | 1113  |       |

# **CAPACITANCE** (TA = $+25^{\circ}$ C)

| PARAMETER          | <b>SYMBOL</b> | MIN | TYP | MAX | UNITS | NOTES |

|--------------------|---------------|-----|-----|-----|-------|-------|

| Input Capacitance  | $C_{IN}$      |     |     | 5   | pF    |       |

| Output Capacitance | $C_{OUT}$     |     |     | 7   | pF    |       |

#### **NOTES:**

- 1. All voltages are referenced to ground.

- 2.  $\overline{\text{PBRST}}$  is internally pulled up to  $V_{CC}$  with an internal impedance of  $40k\Omega$  typical.

- 3. Measured with  $\overline{PBRST} = V_{CC}$  and  $\overline{RST1}$ ,  $\overline{RST2}$ , and  $\overline{RST3}$  open.

- 4. Measured with outputs open and all inputs at  $V_{CC}$  or Ground (except TD and TOL can be floating).

- 5. Noise Immunity Pulses  $\leq$  2ms at  $V_{CC}$  TP minimum will not cause a reset.

- 6. The  $t_F$  value is for reference in defining values for  $t_{RPD}$  and should not be considered a requirement for proper operation or use of the device.

- 7. See  $t_{RST1}$ ,  $t_{RST2}$ , and  $t_{RST3}$  for specific  $t_{RPU}$  AC timing parameters.

#### **ORDERING INFORMATION**

| PART #   | PIN PACKAGE    | TEMP           | TYPE                 |

|----------|----------------|----------------|----------------------|

| DS1830   | 8-DIP 300-MIL  | -40°C to +85°C | 5V Reset Sequencer   |

| DS1830S  | 8-SO 150-MIL   | -40°C to +85°C | 5V Reset Sequencer   |

| DS1830U  | 8-μSOP 118-MIL | -40°C to +85°C | 5V Reset Sequencer   |

| DS1830A  | 8-DIP 300-MIL  | -40°C to +85°C | 3.3V Reset Sequencer |

| DS1830AS | 8-SO 150-MIL   | -40°C to +85°C | 3.3V Reset Sequencer |

| DS1830AU | 8-μSOP 118-MIL | -40°C to +85°C | 3.3V Reset Sequencer |

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## Maxim Integrated:

<u>DS1830+</u> <u>DS1830A+</u> <u>DS1830AS+T&R</u> <u>DS1830AU+T&R</u> <u>DS1830S+</u> <u>DS1830S+T&R</u> <u>DS1830U+T&R</u> <u>DS1830AU+C02</u> <u>DS1830AS+</u> <u>DS1830AU+</u>