### ABSOLUTE MAXIMUM RATINGS (Note 1)

| V <sub>IN</sub> (Note 8)                                                        | –0.3V to 18V                 |

|---------------------------------------------------------------------------------|------------------------------|

| V <sub>SW1</sub> , V <sub>SW2</sub>                                             | –1V to 18V                   |

| PGOOD1, PGOOD2, RUN1, RUN2,                                                     |                              |

| INTV <sub>CC</sub> , EXTV <sub>CC</sub>                                         | 0.3V to 6V                   |

| MODE_PLLIN, f <sub>SET</sub> , TRACK1, TRACK2,                                  |                              |

| DIFFOUT, PHASMD                                                                 | .–0.3V to INTV <sub>CC</sub> |

| V <sub>0UT1</sub> , V <sub>0UT2</sub> , V <sub>0UTS1</sub> , V <sub>0UTS2</sub> | 0.3V to 6V                   |

| DIFFP, DIFFN                                                                    | .–0.3V to INTV <sub>CC</sub> |

| COMP1, COMP2, V <sub>FB1</sub> , V <sub>FB2</sub> (Note 6) |                |

|------------------------------------------------------------|----------------|

| INTV <sub>CC</sub> Peak Output Current                     |                |

| Internal Operating Temperature Range (I                    | Vote 2)        |

| E- and I-Grade                                             | –40°C to 125°C |

| MP-Grade                                                   | –55°C to 125°C |

| Storage Temperature Range                                  | –55°C to 125°C |

| Peak Package Body Temperature                              |                |

| (Mount on Top Side of PCB Only)                            | 245°C          |

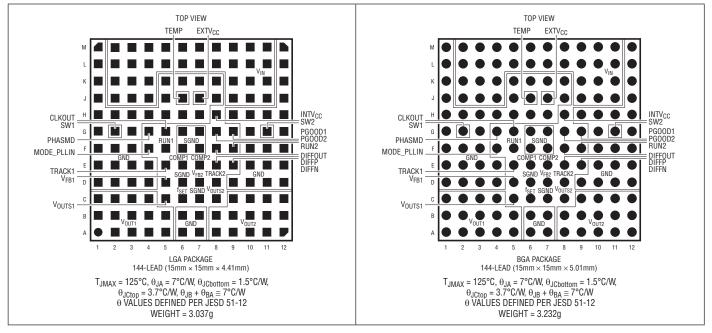

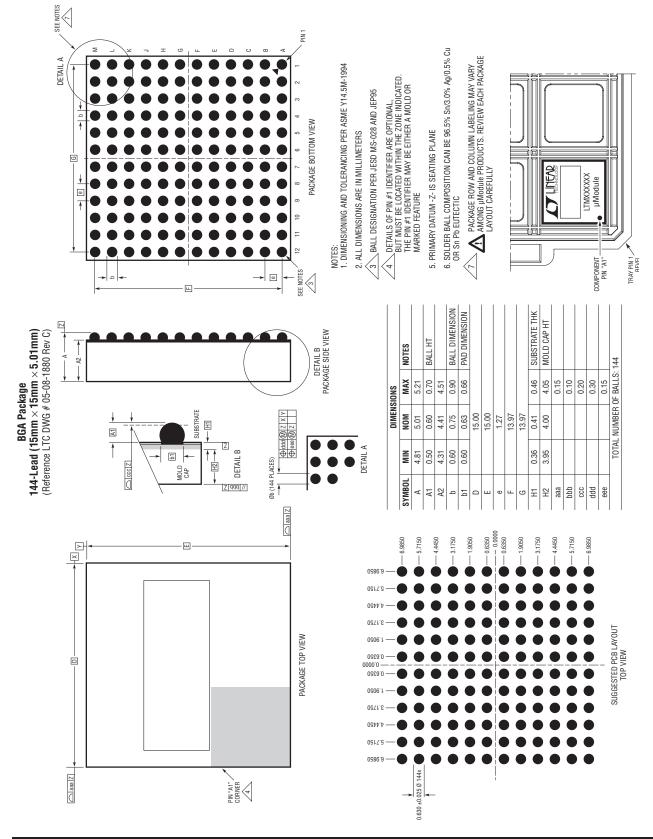

### PIN CONFIGURATION

### ORDER INFORMATION

#### http://www.linear.com/product/LTM4620A#orderinfo

|                 |                    | PART M    | PART MARKING* |                 | MSL    | TEMPERATURE RANGE |  |

|-----------------|--------------------|-----------|---------------|-----------------|--------|-------------------|--|

| PART NUMBER     | PAD OR BALL FINISH | DEVICE    | FINISH CODE   | PACKAGE<br>TYPE | RATING | (Note 2)          |  |

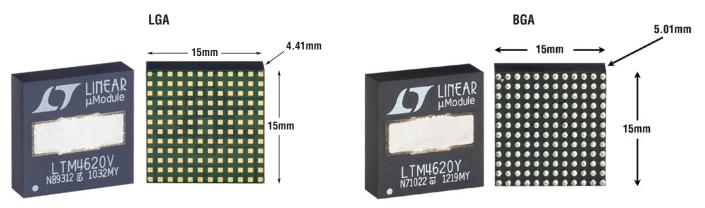

| LTM4620AEV#PBF  | Au (RoHS)          | LTM4620AV | e4            | LGA             | 3      | -40°C to 125°C    |  |

| LTM4620AIV#PBF  | Au (RoHS)          | LTM4620AV | e4            | LGA             | 3      | -40°C to 125°C    |  |

| LTM4620AEY#PBF  | SAC305 (RoHS)      | LTM4620AY | e1            | BGA             | 3      | -40°C to 125°C    |  |

| LTM4620AIY#PBF  | SAC305 (RoHS)      | LTM4620AY | e1            | BGA             | 3      | -40°C to 125°C    |  |

| LTM4620AIY      | SnPb (63/37)       | LTM4620AY | eO            | BGA             | 3      | -40°C to 125°C    |  |

| LTM4620AMPY#PBF | SAC305 (RoHS)      | LTM4620AY | e1            | BGA             | 3      | –55°C to 125°C    |  |

| LTM4620AMPY     | SnPb (63/37)       | LTM4620AY | eO            | BGA             | 3      | -55°C to 125°C    |  |

Consult Marketing for parts specified with wider operating temperature ranges. \*Device temperature grade is indicated by a label on the shipping container. Pad or ball finish code is per IPC/JEDEC J-STD-609.

Recommended LGA and BGA PCB Assembly and Manufacturing Procedures:

www.linear.com/umodule/pcbassembly

• Terminal Finish Part Marking: www.linear.com/leadfree • LGA and BGA Package and Tray Drawings: www.linear.com/packaging

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified internal operating temperature range. Specified as each individual output channel.  $T_A = 25^{\circ}C$  (Note 2),  $V_{IN} = 12V$  and  $V_{RUN1}$ ,  $V_{RUN2}$  at 5V unless otherwise noted. Per the typical application in Figure 26.

| SYMBOL                                                               | PARAMETER                                          | CONDITIONS                                                                                                                                                                                                                                                           |   | MIN   | TYP                 | MAX   | UNITS                |

|----------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|---------------------|-------|----------------------|

| V <sub>IN</sub>                                                      | Input DC Voltage                                   |                                                                                                                                                                                                                                                                      |   | 4.5   |                     | 16    | V                    |

| V <sub>OUT</sub>                                                     | Output Voltage                                     | (Note 8)                                                                                                                                                                                                                                                             |   | 0.6   |                     | 5.3   | V                    |

| V <sub>OUT1(DC)</sub> ,<br>V <sub>OUT2(DC)</sub>                     | Output Voltage, Total Variation with Line and Load | $C_{IN} = 22\mu F \times 3$ , $C_{OUT} = 100\mu F \times 1$ Ceramic,<br>220 $\mu$ F POSCAP                                                                                                                                                                           | • | 1.477 | 1.5                 | 1.523 | V                    |

| Input Specifications                                                 | l                                                  | 1                                                                                                                                                                                                                                                                    |   |       |                     |       | L                    |

| V <sub>RUN1</sub> , V <sub>RUN2</sub>                                | RUN Pin On/Off Threshold                           | RUN Rising                                                                                                                                                                                                                                                           |   | 1.1   | 1.25                | 1.40  | V                    |

| V <sub>RUN1HYS</sub> , V <sub>RUN2HYS</sub>                          | RUN Pin On Hysteresis                              |                                                                                                                                                                                                                                                                      |   |       | 150                 |       | mV                   |

| I <sub>INRUSH(VIN)</sub>                                             | Input Inrush Current at Start-Up                   | $ \begin{array}{l} I_{OUT} = 0 \text{A}, \ C_{\text{IN}} = 22 \mu \text{F} \times 3, \ C_{\text{SS}} = 0.01 \mu \text{F}, \\ C_{OUT} = 100 \mu \text{F} \times 3, \ V_{OUT1} = 1.5 \text{V}, \ V_{OUT2} = 1.5 \text{V}, \\ V_{\text{IN}} = 12 \text{V} \end{array} $ |   |       | 1                   |       | A                    |

| I <sub>Q(VIN)</sub>                                                  | Input Supply Bias Current                          | $ \begin{array}{l} V_{IN} = 12V,  V_{OUT} = 1.5V,  Burst  Mode  Operation \\ V_{IN} = 12V,  V_{OUT} = 1.5V,  Pulse-Skipping  Mode \\ V_{IN} = 12V,  V_{OUT} = 1.5V,  Switching  Continuous \\ Shutdown,  RUN = 0,  V_{IN} = 12V \end{array} $                        |   |       | 5<br>15<br>65<br>50 |       | mA<br>mA<br>mA<br>μA |

| I <sub>S(VIN)</sub>                                                  | Input Supply Current                               | V <sub>IN</sub> = 5V, V <sub>OUT</sub> = 1.5V, I <sub>OUT</sub> = 13A<br>V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 1.5V, I <sub>OUT</sub> = 13A                                                                                                                      |   |       | 4.6<br>1.853        |       | A<br>A               |

| Output Specifications                                                | 3                                                  |                                                                                                                                                                                                                                                                      |   |       |                     |       |                      |

| I <sub>OUT1(DC)</sub> , I <sub>OUT2(DC)</sub>                        | Output Continuous Current Range                    | V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 1.5V (Notes 7, 8)                                                                                                                                                                                                          |   | 0     |                     | 13    | A                    |

| $\Delta V_{OUT1(LINE)}/V_{OUT1}$<br>$\Delta V_{OUT2(LINE)}/V_{OUT2}$ | Line Regulation Accuracy                           | V <sub>OUT</sub> = 1.5V, V <sub>IN</sub> from 4.75V to 16V<br>I <sub>OUT</sub> = 0A for Each Output,                                                                                                                                                                 | • |       | 0.01                | 0.025 | %/V                  |

| $\frac{\Delta V_{OUT1}/V_{OUT1}}{\Delta V_{OUT2}/V_{OUT2}}$          | Load Regulation Accuracy                           | For Each Output, V <sub>OUT</sub> = 1.5V, 0A to 13A<br>V <sub>IN</sub> = 12V (Note 7)                                                                                                                                                                                | • |       | 0.35                | 0.5   | %                    |

| V <sub>OUT1(AC)</sub> , V <sub>OUT2(AC)</sub>                        | Output Ripple Voltage                              | For Each Output, $I_{OUT} = 0A$ , $C_{OUT} = 100\mu F \times 3/X7R/Ceramic, 470\mu F POSCAP, V_{IN} = 12V, V_{OUT} = 1.5V$ , Frequency = 400kHz                                                                                                                      |   |       | 15                  |       | mV <sub>P-P</sub>    |

| f <sub>S</sub> (Each Channel)                                        | Output Ripple Voltage Frequency                    | V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 1.5V, f <sub>SET</sub> = 1.25V (Note 4)                                                                                                                                                                                    |   |       | 500                 |       | kHz                  |

| f <sub>SYNC</sub><br>(Each Channel)                                  | SYNC Capture Range                                 |                                                                                                                                                                                                                                                                      |   | 400   |                     | 780   | kHz                  |

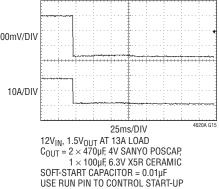

| $\Delta V_{OUTSTART}$ (Each Channel)                                 | Turn-On Overshoot                                  | $C_{OUT} = 100 \mu F/X5 R/Ceramic, 470 \mu F POSCAP,$<br>$V_{OUT} = 1.5 V, I_{OUT} = 0 A V_{IN} = 12 V$                                                                                                                                                              |   |       | 10<br>10            |       | mV<br>mV             |

| t <sub>START</sub><br>(Each Channel)                                 | Turn-On Time                                       | C <sub>OUT</sub> = 100µF/X5R/Ceramic, 470µF POSCAP,<br>No Load, TRACK/SS with 0.01µF to GND,<br>V <sub>IN</sub> = 12V                                                                                                                                                |   |       | 5<br>5              |       | ms<br>ms             |

| $\Delta V_{OUT(LS)}$ (Each Channel)                                  | Peak Deviation for Dynamic Load                    | Load: 0% to 50% to 0% of Full Load<br>$C_{OUT} = 22\mu F \times 3/X5R/Ceramic, 470\mu F POSCAP$<br>$V_{IN} = 12V, V_{OUT} = 1.5V$                                                                                                                                    |   |       | 30                  |       | mV                   |

| t <sub>SETTLE</sub><br>(Each Channel)                                | Settling Time for Dynamic Load<br>Step             | Load: 0% to 50% to 0% of Full Load,<br>V <sub>IN</sub> = 12V, C <sub>OUT</sub> = 100µF, 470µF POSCAP                                                                                                                                                                 |   |       | 20                  |       | μs                   |

| I <sub>OUT(PK)</sub><br>(Each Channel)                               | Output Current Limit                               | V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 1.5V                                                                                                                                                                                                                       |   |       | 20                  |       | A                    |

| Control Section                                                      |                                                    | •                                                                                                                                                                                                                                                                    |   |       |                     |       | ·                    |

| V <sub>FB1</sub> , V <sub>FB2</sub>                                  | Voltage at V <sub>FB</sub> Pins                    | I <sub>OUT</sub> = 0A, V <sub>OUT</sub> = 1.5V                                                                                                                                                                                                                       |   | 0.592 | 0.600               | 0.606 | V                    |

| I <sub>FB</sub>                                                      |                                                    | (Note 6)                                                                                                                                                                                                                                                             |   |       | -5                  | -20   | nA                   |

| V <sub>OVL</sub>                                                     | Feedback Overvoltage Lockout                       |                                                                                                                                                                                                                                                                      |   | 0.64  | 0.66                | 0.68  | V                    |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified internal operating temperature range. Specified as each individual output channel.  $T_A = 25$ °C (Note 2),  $V_{IN} = 12V$  and VRUN1, VRUN2 at 5V unless otherwise noted. Per the typical application in Figure 26.

| SYMBOL                                           | PARAMETER                                                                         | CONDITIONS                                                                                                                 | MIN                      | ТҮР             | MAX   | UNITS             |

|--------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------|-------|-------------------|

| TRACK1 (I),<br>TRACK2 (I)                        | Track Pin Soft-Start Pull-Up Current                                              | TRACK1 (I),TRACK2 (I) Start at 0V                                                                                          | 1                        | 1.25            | 1.5   | μA                |

| UVLO                                             | Undervoltage Lockout                                                              | V <sub>IN</sub> Falling<br>V <sub>IN</sub> Rising                                                                          |                          | 3.3<br>3.9      |       | V<br>V            |

| UVLO Hysteresis                                  |                                                                                   |                                                                                                                            |                          | 0.6             |       | V                 |

| t <sub>ON(MIN)</sub>                             | Minimum On-Time                                                                   | (Note 6)                                                                                                                   |                          | 90              |       | ns                |

| R <sub>FBHI1</sub> , R <sub>FBHI2</sub>          | Resistor Between $V_{OUTS1},V_{OUTS2}$ and $V_{FB1},V_{FB2}$ Pins for Each Output |                                                                                                                            | 59.90                    | 60.4            | 60.75 | kΩ                |

| V <sub>PGOOD1</sub> , V <sub>PGOOD2</sub><br>Low | PGOOD Voltage Low                                                                 | I <sub>PGOOD</sub> = 2mA                                                                                                   |                          | 0.1             | 0.3   | V                 |

| I <sub>PGOOD</sub>                               | PGOOD Leakage Current                                                             | V <sub>PG00D</sub> = 5V                                                                                                    |                          |                 | ±5    | μA                |

| V <sub>PGOOD</sub>                               | PGOOD Trip Level                                                                  | V <sub>FB</sub> with Respect to Set Output Voltage<br>V <sub>FB</sub> Ramping Negative<br>V <sub>FB</sub> Ramping Positive |                          | -10<br>10       |       | %                 |

| INTV <sub>CC</sub> Linear Regul                  | ator                                                                              |                                                                                                                            |                          |                 |       |                   |

| VINTVCC                                          | Internal V <sub>CC</sub> Voltage                                                  | 6V < V <sub>IN</sub> < 16V                                                                                                 | 4.8                      | 5               | 5.2   | V                 |

| V <sub>INTVCC</sub><br>Load Regulation           | INTV <sub>CC</sub> Load Regulation                                                | I <sub>CC</sub> = 0mA to 50mA                                                                                              |                          | 0.5             | 2     | %                 |

| V <sub>EXTVCC</sub>                              | EXTV <sub>CC</sub> Switchover Voltage                                             | EXTV <sub>CC</sub> Ramping Positive                                                                                        | 4.5                      | 4.7             |       | V                 |

| V <sub>EXTVCC(DROP)</sub>                        | EXTV <sub>CC</sub> Dropout                                                        | $I_{CC} = 20 \text{mA}, V_{EXTVCC} = 5 \text{V}$                                                                           |                          | 50              | 100   | mV                |

| V <sub>EXTVCC(HYST)</sub>                        | EXTV <sub>CC</sub> Hysteresis                                                     |                                                                                                                            |                          | 200             |       | mV                |

| Oscillator and Phase                             | e-Locked Loop                                                                     |                                                                                                                            |                          |                 |       |                   |

| Frequency Nominal                                | Nominal Frequency                                                                 | f <sub>SET</sub> = 1.2V                                                                                                    | 450                      | 500             | 550   | kHz               |

| Frequency Low                                    | Lowest Frequency                                                                  | f <sub>SET</sub> = 0V (Note 5)                                                                                             | 210                      | 250             | 290   | kHz               |

| Frequency High                                   | Highest Frequency                                                                 | $f_{SET}$ > 2.4V, Up to INTV <sub>CC</sub>                                                                                 | 700                      | 780             | 860   | kHz               |

| f <sub>SET</sub>                                 | Frequency Set Current                                                             |                                                                                                                            | 9                        | 10              | 11    | μA                |

| R <sub>MODE_PLLIN</sub>                          | MODE_PLLIN Input Resistance                                                       |                                                                                                                            |                          | 250             |       | kΩ                |

| CLKOUT                                           | Phase (Relative to V <sub>OUT1</sub> )                                            | PHASMD = GND<br>PHASMD = Float<br>PHASMD = INTV <sub>CC</sub>                                                              |                          | 60<br>90<br>120 |       | Deg<br>Deg<br>Deg |

| CLK High<br>CLK Low                              | Clock High Output Voltage<br>Clock Low Output Voltage                             |                                                                                                                            | 2                        |                 | 0.2   | V<br>V            |

| Differential Amplifie                            | r                                                                                 |                                                                                                                            |                          |                 |       |                   |

| A <sub>V</sub> Differential<br>Amplifier         | Gain                                                                              |                                                                                                                            |                          | 1               |       | V                 |

| R <sub>IN</sub>                                  | Input Resistance                                                                  | Measured at DIFFP Input                                                                                                    |                          | 80              |       | kΩ                |

| V <sub>OS</sub>                                  | Input Offset Voltage                                                              | V <sub>DIFFP</sub> = V <sub>DIFFOUT</sub> = 1.5V, I <sub>DIFFOUT</sub> = 100µA                                             |                          |                 | 3     | mV                |

| PSRR Differential<br>Amplifier                   | Power Supply Rejection Ratio                                                      | 5V < V <sub>IN</sub> < 16V                                                                                                 |                          | 90              |       | dB                |

| I <sub>CL</sub>                                  | Maximum Output Current                                                            |                                                                                                                            |                          | 2               |       | mA                |

| V <sub>OUT(MAX)</sub>                            | Maximum Output Voltage                                                            | I <sub>DIFFOUT</sub> = 300μA                                                                                               | INTV <sub>CC</sub> – 1.4 | 1               |       | V                 |

### **ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified internal

operating temperature range. Specified as each individual output channel.  $T_A = 25^{\circ}C$  (Note 2),  $V_{IN} = 12V$  and VRUN1, VRUN2 at 5V unless otherwise noted. Per the typical application in Figure 26.

| SYMBOL            | PARAMETER               | CONDITIONS |   | MIN | ТҮР   | MAX | UNITS |

|-------------------|-------------------------|------------|---|-----|-------|-----|-------|

| GBW               | Gain Bandwidth Product  |            |   |     | 3     |     | MHz   |

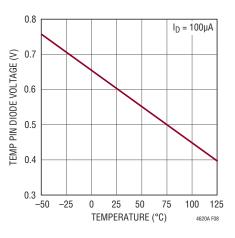

| V <sub>TEMP</sub> | Diode Connected PNP     | Ι = 100μΑ  |   |     | 0.598 |     | V     |

| TC                | Temperature Coefficient |            | ٠ |     | 2.0   |     | mV/C  |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTM4620A is tested under pulsed load conditions such that  $T_J \approx T_A$ . The LTM4620AE is guaranteed to meet specifications from 0°C to 125°C internal temperature. Specifications over the -40°C to 125°C internal operating temperature range are assured by design, characterization and correlation with statistical process controls. The LTM4620AI is guaranteed over the full -40°C to 125°C internal operating temperature range. The LTM4620AMP is tested and guaranteed over the -55°C to 125°C operating temperature range. For output current derating at high temperature, please refer to thermal conditions and output current derating discussion. Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance and other environmental factors.

**Note 3:** Two outputs are tested separately and the same testing condition is applied to each output.

**Note 4:** The switching frequency is programmable from 400kHz to 750kHz. **Note 5:** The LTM4620A is designed to operate from 400kHz to 750kHz

**Note 6:** These parameters are tested at wafer sort.

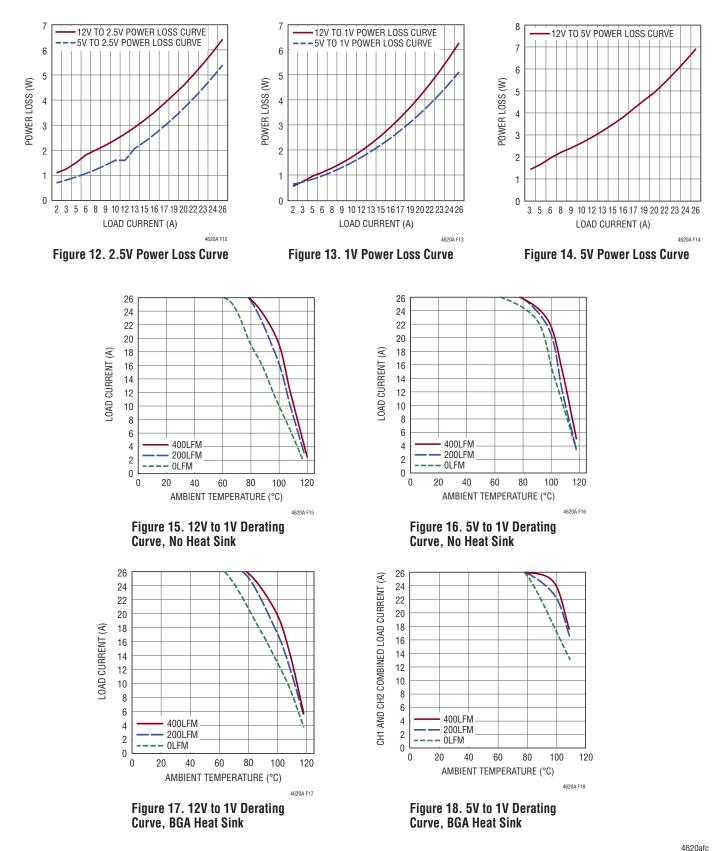

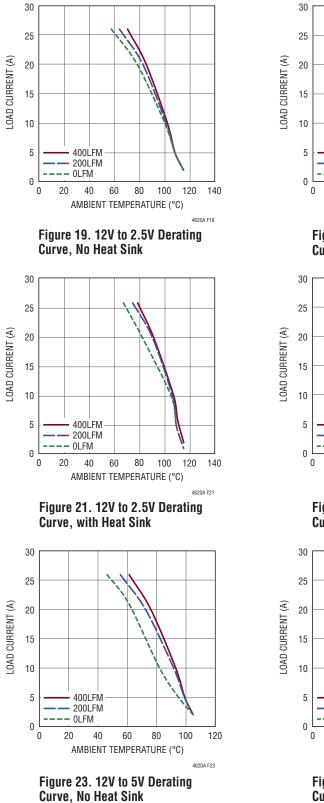

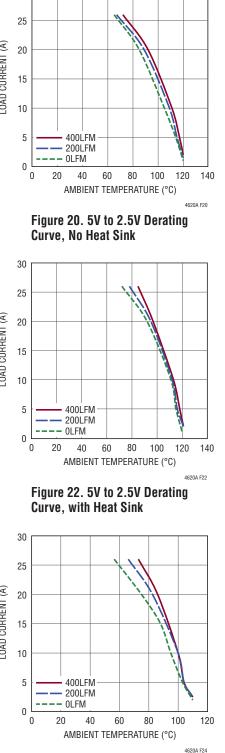

**Note 7:** See output current derating curves for different V<sub>IN</sub>, V<sub>OUT</sub> and T<sub>A</sub>. **Note 8:** Output current limitations. For 10V  $\leq$  V<sub>IN</sub>  $\leq$  16V, the 5V output current needs to be limited to 12A/channel, switching frequency = 750kHz. Derating curves apply. For 7V  $\leq$  V<sub>IN</sub>  $\leq$  9V, the 5V output current needs to be limited to 13A/channel, switching frequency = 750kHz. Derating curves apply. All other input and output combinations are 13A/channel with recommended switching frequency included in the efficiency graphs. Derating curves apply.

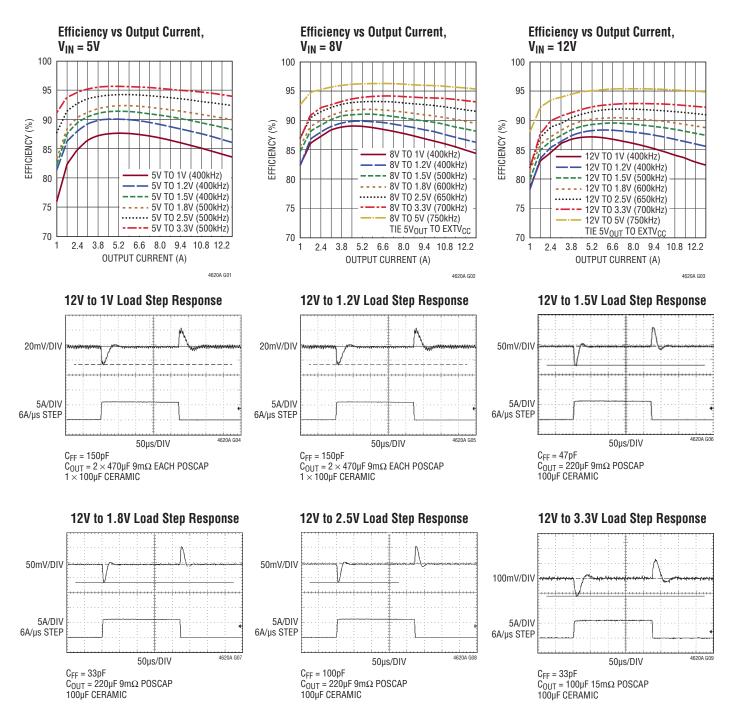

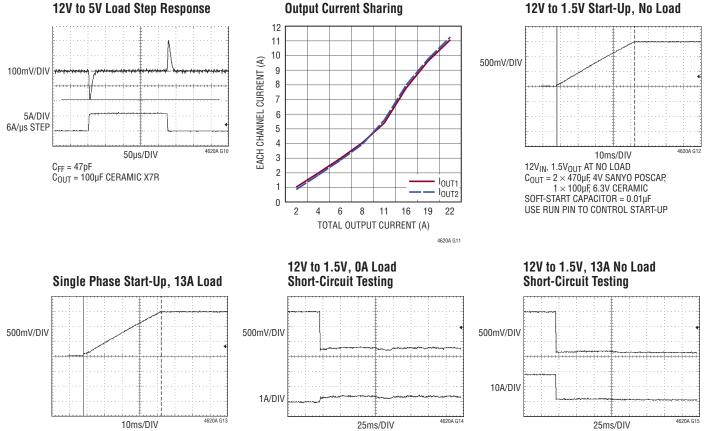

### **TYPICAL PERFORMANCE CHARACTERISTICS**

### **TYPICAL PERFORMANCE CHARACTERISTICS**

$\begin{array}{l} 12V_{IN},\,1.5V_{OUT}\,\text{AT}\,\,13A\,\,\text{LOAD}\\ C_{OUT}=2\times470\mu\text{F},\,4V\,\,\text{SANYO}\,\,\text{POSCAP},\\ 1\times100\mu\text{F},\,6.3V\,\,\text{CERAMIC} \end{array}$ SOFT-START CAPACITOR = 0.01µF USE RUN PIN TO CONTROL START-UP

### PIN FUNCTIONS (Recommended to Use Test Points to Monitor Signal Pin Connections.)

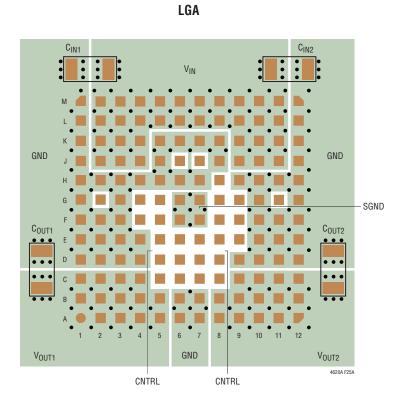

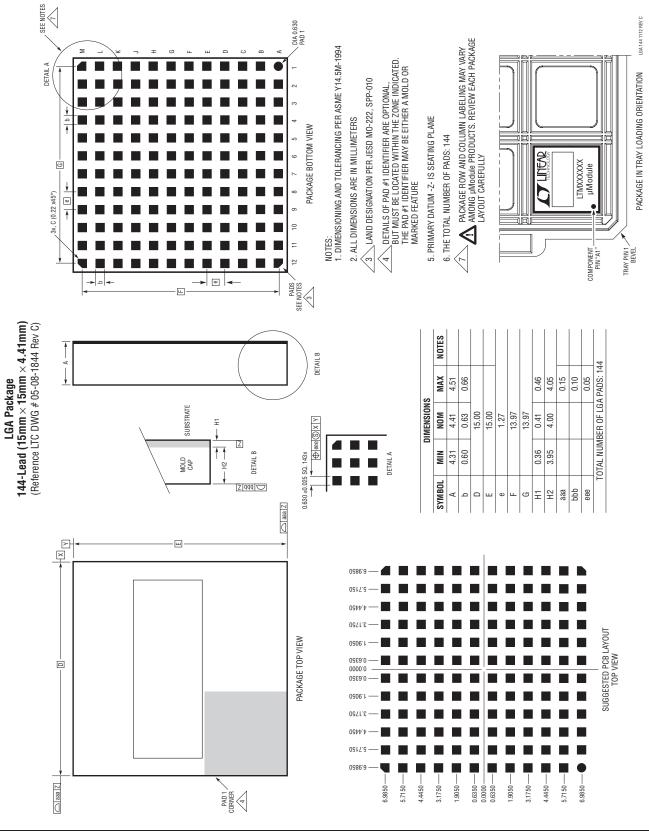

PACKAGE ROW AND COLUMN LABELING MAY VARY AMONG µModule PRODUCTS. REVIEW EACH PACKAGE LAYOUT CAREFULLY.

**V<sub>OUT1</sub> (A1-A5, B1-B5, C1-C4):** Power Output Pins. Apply output load between these pins and GND pins. Recommend placing output decoupling capacitance directly between these pins and GND pins. Review Table 5. See Note 8 in the Electrical Characteristics section for output current guideline.

**GND (A6-A7, B6-B7, D1-D4, D9-D12, E1-E4, E10-E12, F1-F3, F10-F12, G1, G3, G10, G12, H1-H7, H9-H12, J1, J5, J8, J12, K1, K5-K8, K12, L1, L12, M1, M12):** Power Ground Pins for Both Input and Output Returns.

**V<sub>OUT2</sub> (A8-A12, B8-B12, C9-C12):** Power Output Pins. Apply output load between these pins and GND pins. Recommend placing output decoupling capacitance directly between these pins and GND pins. Review Table 5. See Note 8 in the Electrical Characteristics section for output current guideline.

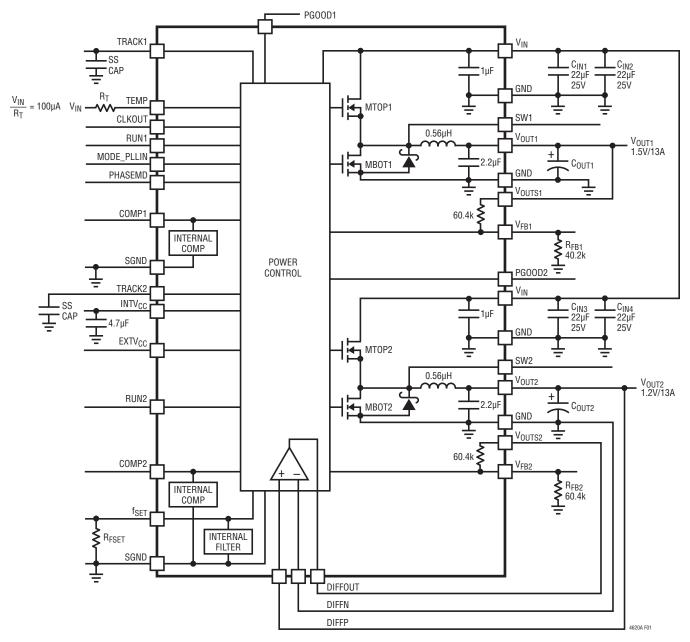

**V<sub>OUTS1</sub>**, **V<sub>OUTS2</sub>** (**C5**, **C8**): This pin is connected to the top of the internal top feedback resistor for each output. The pin can be directly connected to its specific output, or connected to DIFFOUT when the remote sense amplifier is used. In paralleling modules, one of the V<sub>OUTS</sub> pins is connected to the DIFFOUT pin in remote sensing or directly to V<sub>OUT</sub> with no remote sensing. It is very important to connect these pins to either the DIFFOUT or V<sub>OUT</sub> since this is the feedback path, and cannot be left open. See the Applications Information section.

$f_{SET}$  (C6): Frequency Set Pin. A 10µA current is sourced from this pin. A resistor from this pin to ground sets a voltage that in turn programs the operating frequency. Alternatively, this pin can be driven with a DC voltage that can set the operating frequency. See the Applications Information section.

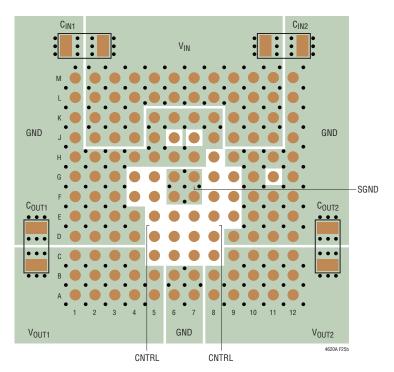

**SGND (C7, D6, G6-G7, F6-F7):** Signal Ground Pin. Return ground path for all analog and low power circuitry. Tie a single connection to the output capacitor GND in the application. See layout guidelines in Figure 25.

$V_{FB1}$ ,  $V_{FB2}$  (D5, D7): The Negative Input of the Error Amplifier for Each Channel. Internally, this pin is connected to  $V_{OUTS1}$  or  $V_{OUTS2}$  with a 60.4kΩ precision resistor. Different output voltages can be programmed with an additional resistor between  $V_{FB}$  and GND pins. In PolyPhase<sup>®</sup> operation, tying the  $V_{FB}$  pins together allows for parallel operation. See the Applications Information section for details.

**TRACK1, TRACK2 (E5, D8):** Output Voltage Tracking Pin and Soft-Start Inputs. Each channel has a  $1.3\mu$ A pull-up current source. When one channel is configured to be master of the two channels, then a capacitor from this pin to ground will set a soft-start ramp rate. The remaining channel can be set up as the slave, and have the master's output applied through a voltage divider to the slave output's track pin. This voltage divider is equal to the slave output's feedback divider for coincidental tracking. See the Applications Information section.

**COMP1, COMP2 (E6, E7):** Current control threshold and error amplifier compensation point for each channel. The current comparator threshold increases with this control voltage. Tie the COMP pins together for parallel operation. The device is internal compensated.

**DIFFP (E8):** Positive input of the remote sense amplifier. This pin is connected to the remote sense point of the output voltage. Diffamp can be used for  $\leq$ 3.3V outputs. See the Applications Information section.

**DIFFN (E9):** Negative input of the remote sense amplifier. This pin is connected to the remote sense point of the output GND. Diffamp can be used for  $\leq$ 3.3V outputs. See the Applications Information section.

**MODE\_PLLIN (F4):** Force Continuous Mode, Burst Mode Operation, or Pulse-Skipping Mode Selection Pin and External Synchronization Input to Phase Detector Pin. Connect this pin to SGND to force both channels into force continuous mode of operation. Connect to  $INTV_{CC}$ to enable pulse-skipping mode of operation. Leaving the pin floating will enable Burst Mode operation. A clock on the pin will force both channels into continuous mode of operation and synchronized to the external clock applied to this pin.

### **PIN FUNCTIONS** (Recommended to Use Test Points to Monitor Signal Pin Connections.)

**RUN1, RUN2 (F5, F9):** Run Control Pin. A voltage above 1.25V will turn on each channel in the module. A voltage below 1.25V on the RUN pin will turn off the related channel. Each RUN pin has a  $1\mu$ A pull-up current, once the RUN pin reaches 1.2V an additional 4.5 $\mu$ A pull-up current is added to this pin.

**DIFFOUT (F8):** Internal Remote Sense Amplifier Output. Connect this pin to  $V_{OUTS1}$  or  $V_{OUTS2}$  depending on which output is using remote sense. In parallel operation connect one of the  $V_{OUTS}$  pin to DIFFOUT for remote sensing. Diffamp can be used for  $\leq$ 3.3V outputs.

**SW1, SW2 (G2, G11):** Switching node of each channel that is used for testing purposes. Also an R-C snubber network can be applied to reduce or eliminate switch node ringing, or otherwise leave floating. See the Applications Information section.

**PHASMD (G4):** Connect this pin to SGND,  $INTV_{CC}$ , or floating this pin to select the phase of CLKOUT to 60 degrees, 120 degrees, and 90 degrees respectively.

**CLKOUT (G5):** Clock output with phase control using the PHASMD pin to enable multiphase operation between devices. See the Applications Information section.

**PGOOD1, PGOOD2 (G9, G8):** Output Voltage Power Good Indicator. Open drain logic output that is pulled to ground when the output voltage is not within  $\pm 7.5\%$  of the regulation point.

**INTV<sub>CC</sub> (H8):** Internal 5V Regulator Output. The control circuits and internal gate drivers are powered from this voltage. Decouple this pin to PGND with a  $4.7\mu$ F low ESR tantalum or ceramic. INTV<sub>CC</sub> is activated when either RUN1 or RUN2 is activated.

**TEMP (J6):** Onboard Temperature Diode for Monitoring the VBE Junction Voltage Change with Temperature. See the Applications Information section.

**EXTV<sub>CC</sub> (J7):** External power input that is enabled through a switch to INTV<sub>CC</sub> whenever EXTV<sub>CC</sub> is greater than 4.7V. Do not exceed 6V on this input, and connect this pin to  $V_{IN}$  when operating  $V_{IN}$  on 5V. An efficiency increase will occur that is a function of the ( $V_{IN} - INTV_{CC}$ ) multiplied by power MOSFET driver current. Typical current requirement is 30mA.  $V_{IN}$  must be applied before EXTV<sub>CC</sub>, and EXTV<sub>CC</sub> must be removed before  $V_{IN}$ . A 5V output can be tied to this pin to increase efficiency. See Applications Information section.

$V_{IN}$  (M2-M11, L2-L11, J2-J4, J9-J11, K2-K4, K9-K11): Power Input Pins. Apply input voltage between these pins and GND pins. Recommend placing input decoupling capacitance directly between  $V_{IN}$  pins and GND pins.

### SIMPLIFIED BLOCK DIAGRAM

Figure 1. Simplified LTM4620A Block Diagram

### **DECOUPLING REQUIREMENTS** $T_A = 25^{\circ}C$ . Use Figure 1 configuration.

| SYMBOL                                                                   | PARAMETER                                                                                                                                      | CONDITIONS                                                  | MIN TYP    | MAX | UNITS    |

|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------|-----|----------|

| C <sub>IN1,</sub> C <sub>IN2</sub><br>C <sub>IN3,</sub> C <sub>IN4</sub> | External Input Capacitor Requirement $(V_{IN1} = 4.75V \text{ to } 16V, V_{OUT1} = 1.5V)$ $(V_{IN2} = 4.75V \text{ to } 16V, V_{OUT2} = 1.2V)$ | I <sub>OUT1</sub> = 13A<br>I <sub>OUT2</sub> = 13A (Note 8) | 22<br>22   |     | μF<br>μF |

| C <sub>OUT1</sub><br>C <sub>OUT2</sub>                                   | External Output Capacitor Requirement ( $V_{IN1} = 4.75V$ to 16V, $V_{OUT1} = 1.5V$ ) ( $V_{IN2} = 4.75V$ to 16V, $V_{OUT2} = 1.2V$ )          | I <sub>OUT1</sub> = 13A<br>I <sub>OUT2</sub> = 13A (Note 8) | 300<br>300 |     | μF<br>μF |

### OPERATION

#### **Power Module Description**

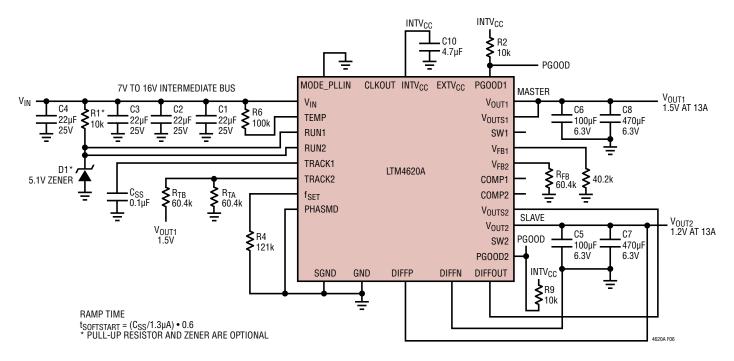

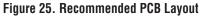

The LTM4620A is a dual-output standalone nonisolated switching mode DC/DC power supply. It can provide two 13A outputs with few external input and output capacitors and setup components. This module provides precisely regulated output voltages programmable via external resistors from  $0.6V_{DC}$  to  $5.3V_{DC}$  over 4.5V to 16V input voltages. The typical application schematic is shown in Figure 26. See Note 8 in the Electrical Characteristics section for output current guideline.

The LTM4620A has dual integrated constant-frequency current mode regulators and built-in power MOSFET devices with fast switching speed. The typical switching frequency is 500kHz. For switching-noise sensitive applications, it can be externally synchronized from 400kHz to 780kHz. A resistor can be used to program a free run frequency on the  $f_{SET}$  pin. See the Applications Information section.

With current mode control and internal feedback loop compensation, the LTM4620A module has sufficient stability margins and good transient performance with a wide range of output capacitors, even with all ceramic output capacitors.

Current mode control provides cycle-by-cycle fast current limit and foldback current limit in an overcurrent condition. Internal overvoltage and undervoltage comparators pull the open-drain PGOOD outputs low if the output feedback voltage exits a  $\pm 10\%$  window around the regulation point. As the output voltage exceeds 10% above regulation, the bottom MOSFET will turn on to clamp the output voltage. The top MOSFET will be turned off. This overvoltage protect is feedback voltage referred.

Pulling the RUN pins below 1.1V forces the regulators into a shutdown state, by turning off both MOSFETs.

The TRACK pins are used for programming the output voltage ramp and voltage tracking during start-up or used for soft-starting the regulator. See the Applications Information section.

The LTM4620A is internally compensated to be stable over all operating conditions. Table 5 provides a guide line for input and output capacitances for several operating conditions. LTpowerCAD<sup>®</sup> is available for transient and stability analysis. The V<sub>FB</sub> pin is used to program the output voltage with a single external resistor to ground. A differential remote sense amplifier is available for sensing the output voltage accurately on one of the outputs at the load point, or in parallel operation sensing the output voltage at the load point.

Multiphase operation can be easily employed with the MODE\_PLLIN, PHASMD, and CLKOUT pins. Up to 12 phases can be cascaded to run simultaneously with respect to each other by programming the PHMODE pin to different levels. See the Applications Information section.

High efficiency at light loads can be accomplished with selectable Burst Mode operation or pulse-skipping operation using the MODE pin. These light load features will accommodate battery operation. Efficiency graphs are provided for light load operation in the Typical Performance Characteristics section. See the Applications Information section for details.

A TEMP pin is provided to allow the internal device temperature to be monitored using an onboard diode connected PNP transistor. This diode connected PNP transistor is grounded in the module and can be used as a general temperature monitor using a device that is designed to monitor the single-ended connection.

The typical LTM4620A application circuit is shown in Figure 26. External component selection is primarily determined by the maximum load current and output voltage. Refer to Table 5 for specific external capacitor requirements for particular applications.

#### V<sub>IN</sub> to V<sub>OUT</sub> Step-Down Ratios

There are restrictions in the maximum V<sub>IN</sub> and V<sub>OUT</sub> stepdown ratio that can be achieved for a given input voltage. Each output of the LTM4620A is capable of 95% duty cycle at 500kHz, but the V<sub>IN</sub> to V<sub>OUT</sub> minimum dropout is still shown as a function of its load current and will limit output current capability related to high duty cycle on the top side switch. Minimum on-time t<sub>ON(MIN)</sub> is another consideration in operating at a specified duty cycle while operating at a certain frequency due to the fact that t<sub>ON(MIN)</sub> < D/f<sub>SW</sub>, where D is duty cycle and f<sub>SW</sub> is the switching frequency. t<sub>ON(MIN)</sub> is specified in the electrical parameters as 90ns. See Note 8 in the Electrical Characteristics section for output current guideline.

#### **Output Voltage Programming**

The PWM controller has an internal 0.6V reference voltage. As shown in the Block Diagram, a  $60.4k\Omega$  internal feedback resistor connects between the V<sub>OUTS1</sub> to V<sub>FB1</sub> and V<sub>OUTS2</sub> to V<sub>FB2</sub>. It is very important that these pins be connected to their respective outputs for proper feedback regulation. Overvoltage can occur if these V<sub>OUTS1</sub> and V<sub>OUTS2</sub> pins are left floating when used as individual regulators, or at least one of them is used in paralleled regulators. The output voltage will default to 0.6V with no feedback resistor on either V<sub>FB1</sub> or V<sub>FB2</sub>. Adding a resistor R<sub>FB</sub> from V<sub>FB</sub> pin to GND programs the output voltage:

$$V_{OUT} = 0.6V \bullet \frac{60.4k + R_{FB}}{R_{FB}}$$

| V <sub>OUT</sub> | 0.6V | 1.0V  | 1.2V  | 1.5V  | 1.8V  | 2.5V  | 3.3V  | 5V    |

|------------------|------|-------|-------|-------|-------|-------|-------|-------|

| R <sub>FB</sub>  | Open | 90.9k | 60.4k | 40.2k | 30.2k | 19.1k | 13.3k | 8.25k |

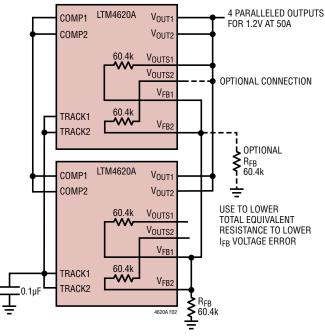

For parallel operation of multiple channels the same feedback setting resistor can be used for the parallel design. This is done by connecting the  $V_{OUTS1}$  to the output as shown in Figure 2, thus tying one of the internal 60.4k resistors to the output. All of the  $V_{FB}$  pins tie together with one programming resistor as shown in Figure 2.

In parallel operation, the V<sub>FB</sub> pins have an I<sub>FB</sub> current of 20nA maximum each channel. To reduce output voltage error due to this current, an additional  $V_{OUTS}$  pin can be tied to  $V_{OUT}$ , and an additional R<sub>FB</sub> resistor can be used to lower the total Thevenin equivalent resistance seen by this current. For example in Figure 2, the total Thevenin equivalent resistance of the V<sub>FB</sub> pin is  $(60.4 \text{k}//\text{R}_{FB})$ , which is 30.2k where R<sub>FB</sub> is equal to 60.4k for a 1.2V output. Four phases connected in parallel equates to a worse case feedback current of  $4 \cdot I_{FB} = 80$  nA maximum. The voltage error is 80 nA  $\cdot 30.2$  k = 2.4mV. If  $V_{OUTS2}$  is connected, as shown in Figure 2, to  $V_{OUT}$ , and another 60.4k resistor is connected from  $V_{FB2}$ to ground, then the voltage error is reduced to 1.2mV. If the voltage error is acceptable then no additional connections are necessary. The onboard 60.4k resistor is 0.5% accurate and the V<sub>FB</sub> resistor can be chosen by the user to be as accurate as needed. All COMP pins are tied together for current sharing between the phases. The TRACK pins can be tied together and a single soft-start capacitor can be used to soft-start the regulator. The soft-start equation will need to have the soft-start current parameter increased by the number of paralleled channels. See TRACK/Soft-Start Pin section.

#### **Input Capacitors**

The LTM4620A module should be connected to a low AC-impedance DC source. For the regulator input four  $22\mu$ F input ceramic capacitors are used for RMS ripple current. A  $47\mu$ F to  $100\mu$ F surface mount aluminum electrolytic bulk capacitor can be used for more input bulk capacitance. This bulk input capacitor is only needed if the input source impedance is compromised by long inductive leads, traces or not enough source capacitance. If low impedance power planes are used, then this bulk capacitor is not needed.

For a buck converter, the switching duty-cycle can be estimated as:

$$\mathsf{D} = \frac{\mathsf{V}_{\mathsf{OUT}}}{\mathsf{V}_{\mathsf{IN}}}$$

Without considering the inductor current ripple, for each output, the RMS current of the input capacitor can be estimated as:

$$I_{CIN(RMS)} = \frac{I_{OUT(MAX)}}{\eta\%} \bullet \sqrt{D \bullet (1-D)}$$

In the above equation,  $\eta\%$  is the estimated efficiency of the power module. The bulk capacitor can be a switcherrated electrolytic aluminum capacitor, Polymer capacitor.

#### **Output Capacitors**

The LTM4620A is designed for low output voltage ripple noise and good transient response. The bulk output capacitors defined as  $C_{OUT}$  are chosen with low enough effective series resistance (ESR) to meet the output voltage ripple and transient requirements.  $C_{OUT}$  can be a low ESR tantalum capacitor, the low ESR polymer capacitor or ceramic capacitor. The typical output capacitance range for each output is from 200µF to 470µF. Additional output filtering may be required by the system designer, if further reduction of output ripples or dynamic transient spikes is required. Table 5 shows a matrix of different output voltages and output capacitors to minimize the voltage droop and overshoot during a 7A/µs transient. The table optimizes total equivalent ESR and total bulk capacitance to optimize the transient performance. Stability criteria are considered in the Table 5 matrix, and the LTpowerCAD will be provided for stability analysis. Multiphase operation will reduce effective output ripple as a function of the number of phases. Application Note 77 discusses this noise reduction versus output ripple current cancellation, but the output capacitance should be considered carefully as a function of stability and transient response. The LTpowerCAD can calculate the output ripple reduction as the number of implemented phases increases by N times. A small value  $10\Omega$  to  $50\Omega$  resistor can be place in series from  $V_{OUT}$  to the  $V_{OUTS}$  pin to allow for a bode plot analyzer to inject a signal into the control loop and validate the regulator stability. The same resistor could be place in series from  $V_{OUT}$  to DIFFP and a bode plot analyzer could inject a signal into the control loop and validate the regulator stability.

#### **Burst Mode Operation**

The LTM4620A is capable of Burst Mode operation on each regulator in which the power MOSFETs operate intermittently based on load demand, thus saving quiescent current. For applications where maximizing the efficiency at very light loads is a high priority, Burst Mode operation should be applied. Burst Mode operation is enabled with the MODE/PLLIN pin floating. During this operation, the peak current of the inductor is set to approximately one third of the maximum peak current value in normal operation even though the voltage at the COMP pin indicates a lower value. The voltage at the COMP pin drops when the inductor's average current is greater than the load requirement. As the COMP voltage drops below 0.5V, the BURST comparator trips, causing the internal sleep line to go high and turn off both power MOSFETs.

In sleep mode, the internal circuitry is partially turned off, reducing the quiescent current to about  $450\mu$ A for each output<sup>22</sup>. The load current is now being supplied from the output capacitors. When the output voltage drops, causing COMP to rise above 0.5V, the internal sleep line goes low, and the LTM4620A resumes normal operation. The next oscillator cycle will turn on the top power MOSFET and the switching cycle repeats. Either regulator can be configured for Burst Mode operation.

#### Pulse-Skipping Mode Operation

In applications where low output ripple and high efficiency at intermediate currents are desired, pulse-skipping mode should be used. Pulse-skipping operation allows the LTM4620A to skip cycles at low output loads, thus increasing efficiency by reducing switching loss. Tying the MODE/PLLIN pin to INTV<sub>CC</sub> enables pulse-skipping operation. At light loads the internal current comparator may remain tripped for several cycles and force the top MOSFET to stay off for several cycles, thus skipping cycles. The inductor current does not reverse in this mode. This mode will maintain higher effective frequencies thus lower output ripple and lower noise than Burst Mode operation. Either regulator can be configured for pulse-skipping mode.

#### **Forced Continuous Operation**

In applications where fixed frequency operation is more critical than low current efficiency, and where the lowest output ripple is desired, forced continuous operation should be used. Forced continuous operation can be enabled by tying the MODE/PLLIN pin to GND. In this mode, inductor current is allowed to reverse during low output loads, the COMP voltage is in control of the current comparator threshold throughout, and the top MOSFET always turns on with each oscillator pulse. During startup, forced continuous mode is disabled and inductor current is prevented from reversing until the LTM4620A's output voltage is in regulation. Either regulator can be configured for force continuous mode.

#### **Multiphase Operation**

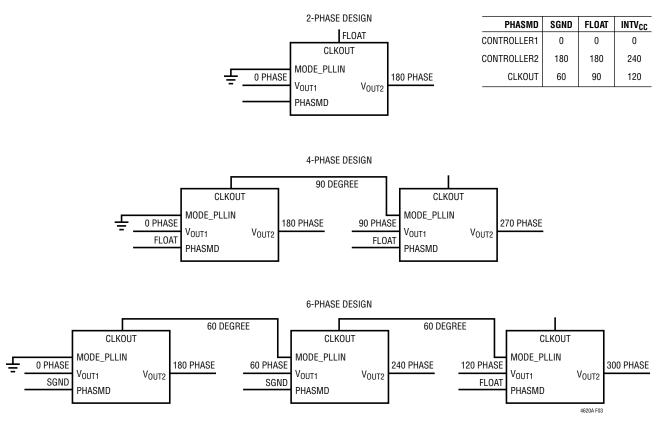

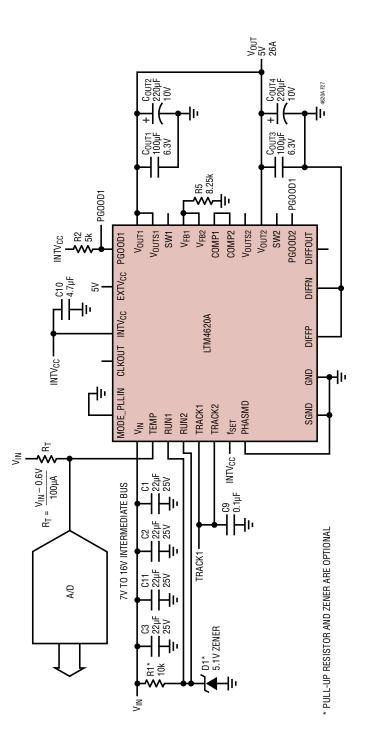

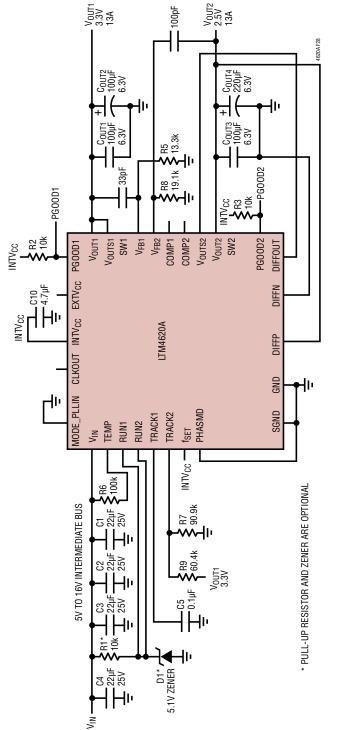

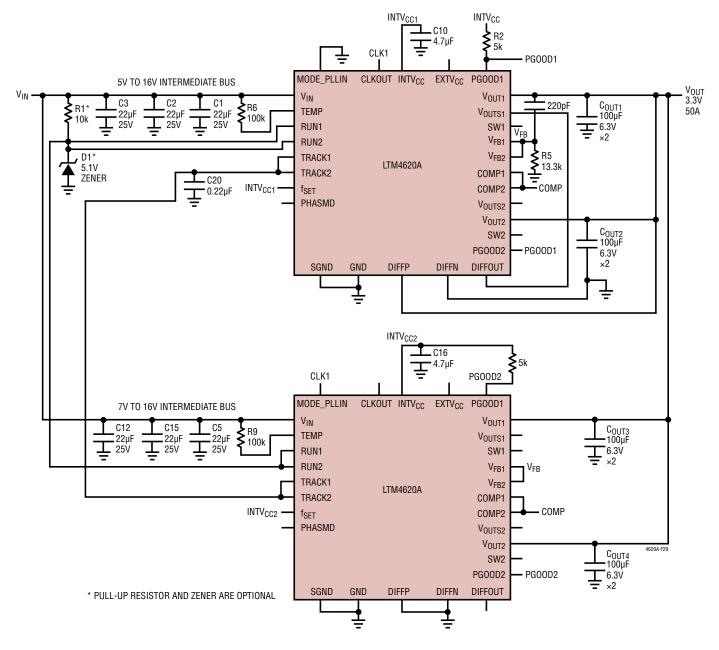

For output loads that demand more than 13A of current. two outputs in LTM4620A or even multiple LTM4620As can be paralleled to run out of phase to provide more output current without increasing input and output voltage ripples. The MODE/PLLIN pin allows the LTM4620A to synchronize to an external clock (between 400kHz and 780kHz) and the internal phase-locked-loop allows the LTM4620A to lock onto an incoming clock phase as well. The CLKOUT signal can be connected to the MODE/PLLIN pin of the following stage to line up both the frequency and the phase of the entire system. Tying the PHMODE pin to INTV<sub>CC</sub>, SGND, or (floating) generates a phase difference (between MODE/PLLIN and CLKOUT) of 120 degrees, 60 degrees, or 90 degrees respectively. A total of 12 phases can be cascaded to run simultaneously with respect to each other by programming the PHMODE pin of each LTM4620A channel to different levels. Figure 3 shows a 2-phase design, 4-phase design and a 6-phase design example for clock phasing with the PHASMD table.

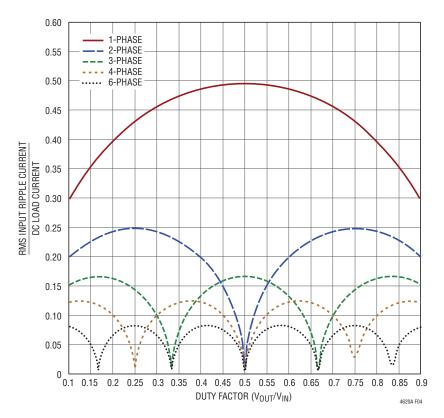

A multiphase power supply significantly reduces the amount of ripple current in both the input and output capacitors. The RMS input ripple current is reduced by, and the effective ripple frequency is multiplied by, the number of phases used (assuming that the input voltage

Figure 3. Examples of 2-Phase, 4-Phase, and 6-Phase Operation with PHASMD Table

is greater than the number of phases used times the output voltage). The output ripple amplitude is also reduced by the number of phases used when all of the outputs are tied together to achieve a single high output current design. The LTM4620A device is an inherently current mode controlled device, so parallel modules will have very good current sharing. This will balance the thermals on the design. Figure 26 shows an example of parallel operation and pin connection.

4620afr

#### Input RMS Ripple Current Cancellation

Application Note 77 provides a detailed explanation of multiphase operation. The input RMS ripple current cancellation mathematical derivations are presented, and a graph is displayed representing the RMS ripple current reduction as a function of the number of interleaved phases. Figure 4 shows this graph.

# Frequency Selection and Phase-Lock Loop (MODE/PLLIN and f<sub>SET</sub> Pins)

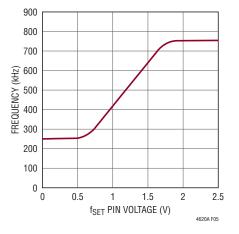

The LTM4620A device is operated over a range of frequencies to improve power conversion efficiency. It is recommended to operate the lower output voltages or lower duty cycle conversions at lower frequencies to improve efficiency by lowering power MOSFET switching losses. Higher output voltages or higher duty cycle conversions can be operated at higher frequencies to limit inductor ripple current. The efficiency graphs will show an operating frequency chosen for that condition. Select frequency in reference to the highest output voltage.

Figure 4. Input RMS Current Ratios to DC Load Current as a Function of Duty Cycle

Figure 5. Operating Frequency vs  $f_{\mbox{\scriptsize SET}}$  Pin Voltage

The LTM4620A switching frequency can be set with an external resistor from the  $f_{SET}$  pin to SGND. An accurate 10µA current source into the resistor will set a voltage that programs the frequency or a DC voltage can be applied. Figure 5 shows a graph of frequency setting verses programming voltage. An external clock can be applied to the MODE/PLLIN pin from 0V to INTV<sub>CC</sub> over a frequency range of 400kHz to 780kHz. The clock input high threshold is 1.6V and the clock input low threshold is 1V. The LTM4620A has the PLL loop filter components on board. The frequency setting resistor should always be present to set the initial switching frequency before locking to an external clock. Both regulators will operate in continuous mode while being externally clock.

The output of the PLL phase detector has a pair of complementary current sources that charge and discharge the internal filter network. When the external clock is applied then the  $f_{SET}$  frequency resistor is disconnected with an internal switch, and the current sources control the frequency adjustment to lock to the incoming external clock. When no external clock is applied, then the internal switch is on, thus connecting the external  $f_{SET}$  frequency set resistor for free run operation.

#### Minimum On-Time

Minimum on-time  $t_{ON}$  is the smallest time duration that the LTM4620A is capable of turning on the top MOSFET on either channel. It is determined by internal timing delays, and the gate charge required turning on the top MOSFET. Low duty cycle applications may approach this minimum on-time limit and care should be taken to ensure that:

$$\frac{V_{OUT}}{V_{IN} \bullet FREQ} > t_{ON(MIN)}$$

If the duty cycle falls below what can be accommodated by the minimum on-time, the controller will begin to skip cycles. The output voltage will continue to be regulated, but the output ripple will increase. The on-time can be increased by lowering the switching frequency. A good rule of thumb is to keep on-time longer than 110ns.

#### **Output Voltage Tracking**

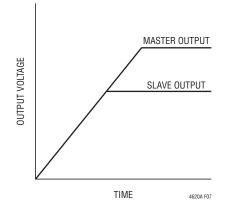

Output voltage tracking can be programmed externally using the TRACK pins. The output can be tracked up and down with another regulator. The master regulator's output is divided down with an external resistor divider that is the same as the slave regulator's feedback divider to implement coincident tracking. The LTM4620A uses an accurate 60.4k resistor internally for the top feedback resistor for each channel. Figure 6 shows an example of coincident tracking. Equations:

$$SLAVE = \left(1 + \frac{60.4k}{R_{TA}}\right) \bullet V_{TRACK}$$

$V_{TRACK}$  is the track ramp applied to the slave's track pin.  $V_{TRACK}$  has a control range of 0V to 0.6V, or the internal reference voltage. When the master's output is divided down with the same resistor values used to set the slave's output, then the slave will coincident track with the master until it reaches its final value. The master will continue to its final value from the slave's regulation point. Voltage tracking is disabled when  $V_{TRACK}$  is more than 0.6V.  $R_{TA}$ in Figure 6 will be equal to the  $R_{FB}$  for coincident tracking. Figure 7 shows the coincident tracking waveforms.

Figure 6. Example of Output Tracking Application Circuit

Figure 7. Output Coincident Tracking Waveform

The TRACK pin can be controlled by a capacitor placed on the regulator TRACK pin to ground. A 1.3 $\mu$ A current source will charge the TRACK pin up to the reference voltage and then proceed up to INTV<sub>CC</sub>. After the 0.6V ramp, the TRACK pin will no longer be in control, and the internal voltage reference will control output regulation from the feedback divider. Foldback current limit is disabled during this sequence of turn-on during tracking or soft-starting. The TRACK pins are pulled low when the RUN pin is below 1.2V. The total soft-start time can be calculated as:

$$t_{\text{SOFT-START}} = \left(\frac{C_{\text{SS}}}{1.3\mu\text{A}}\right) \bullet 0.6$$

Regardless of the mode selected by the MODE/PLLIN pin, the regulator channels will always start in pulseskipping mode up to TRACK = 0.5V. Between TRACK = 0.5V and 0.54V, it will operate in forced continuous mode and revert to the selected mode once TRACK > 0.54V. In order to track with another channel once in steady state operation, the LTM4620A is forced into continuous mode operation as soon as V<sub>FB</sub> is below 0.54V regardless of the setting on the MODE/PLLIN pin.

Ratiometric tracking can be achieved by a few simple calculations and the slew rate value applied to the master's TRACK pin. As mentioned above, the TRACK pin has a control range from 0 to 0.6V. The master's TRACK pin slew rate is directly equal to the master's output slew rate in Volts/Time. The equation:

$$\frac{MR}{SR} \bullet 60.4k = R_{TB}$$

where MR is the master's output slew rate and SR is the slave's output slew rate in Volts/Time. When coincident tracking is desired, then MR and SR are equal, thus  $R_{TB}$  is equal the 60.4k.  $R_{TA}$  is derived from equation:

$$R_{TA} = \frac{0.6V}{\frac{V_{FB}}{60.4k} + \frac{V_{FB}}{R_{FB}} - \frac{V_{TRACK}}{R_{TB}}}$$

where  $V_{FB}$  is the feedback voltage reference of the regulator, and  $V_{TRACK}$  is 0.6V. Since  $R_{TB}$  is equal to the 60.4k top feedback resistor of the slave regulator in equal slew

rate or coincident tracking, then  $R_{TA}$  is equal to  $R_{FB}$  with  $V_{FB} = V_{TRACK}$ . Therefore  $R_{TB} = 60.4k$ , and  $R_{TA} = 60.4k$  in Figure 6.

In ratiometric tracking, a different slew rate maybe desired for the slave regulator.  $R_{TB}$  can be solved for when SR is slower than MR. Make sure that the slave supply slew rate is chosen to be fast enough so that the slave output voltage will reach it final value before the master output.

For example, MR = 1.5V/1ms, and SR = 1.2V/1ms. Then R<sub>TB</sub> = 76.8k. Solve for R<sub>TA</sub> to equal to 49.9k.

Each of the TRACK pins will have the  $1.3\mu$ A current source on when a resistive divider is used to implement tracking on that specific channel. This will impose an offset on the TRACK pin input. Smaller values resistors with the same ratios as the resistor values calculated from the above equation can be used. For example, where the 60.4k is used then a 6.04k can be used to reduce the TRACK pin offset to a negligible value.

#### **Power Good**

The PGOOD pins are open drain pins that can be used to monitor valid output voltage regulation. This pin monitors a  $\pm 10\%$  window around the regulation point. A resistor can be pulled up to a particular supply voltage no greater than 6V maximum for monitoring.

#### **Stability Compensation**

The module has already been internally compensated for all output voltages. Table 5 is provided for most application requirements. The LTpowerCAD will be provided for other control loop optimization.

#### Run Enable

The RUN pins have an enable threshold of 1.4V maximum, typically 1.25V with 150mV of hysteresis. They control the turn on each of the channels and  $INTV_{CC}$ . These pins can be pulled up to  $V_{IN}$  for 5V operation, or a 5V Zener diode can be placed on the pins and a 10k to 100k resistor can be placed up to higher than 5V input for enabling the channels. The RUN pins can also be used for output voltage sequencing. In parallel operation the RUN pins can be tie together

and controlled from a single control. See the Typical Application circuits in Figure 26.

### $\mathsf{INTV}_{\mathsf{CC}}$ and $\mathsf{EXTV}_{\mathsf{CC}}$

The LTM4620A module has an internal 5V low dropout regulator that is derived from the input voltage. This regulator is used to power the control circuitry and the power MOSFET drivers. This regulator can source up to 70mA, and typically uses ~30mA for powering the device at the maximum frequency. This internal 5V supply is enabled by either RUN1 or RUN2.

$\mathsf{EXTV}_{\mathsf{CC}}$  allows an external 5V supply to power the LTM4620A and reduce power dissipation from the internal low dropout 5V regulator. The power loss savings can be calculated by:

$(V_{IN} - 5V) \bullet 30mA = PLOSS$

EXTV<sub>CC</sub> has a threshold of 4.7V for activation, and a maximum rating of 6V. When using a 5V input, connect this 5V input to EXTV<sub>CC</sub> also to maintain a 5V gate drive level. EXTV<sub>CC</sub> must sequence on after V<sub>IN</sub>, and EXTV<sub>CC</sub> must sequence off before V<sub>IN</sub>. When designing a 5V output, connect this 5V output to EXTV<sub>CC</sub>. Use an external 5V bias on EXTV<sub>CC</sub> to improve efficiency.

#### Differential Remote Sense Amplifier

An accurate differential remote sense amplifier is provided to sense low output voltages accurately at the remote load points. This is especially true for high current loads. The amplifier can be used on one of the two channels, or on a single parallel output. It is very important that the DIFFP and DIFFN are connected properly at the output, and DIFFOUT is connected to either V<sub>OUTS1</sub> or V<sub>OUTS2</sub>. In parallel operation, the DIFFP and DIFFN are connected properly at the output, and DIFFOUT is connected to either V<sub>OUTS1</sub> or V<sub>OUTS2</sub>. In parallel operation, the DIFFP and DIFFN are connected properly at the output, and DIFFOUT is connected to one of the V<sub>OUTS</sub> pins. Review the parallel schematics in Figure 29 and review Figure 2. The diffamp can only be used for output voltage  $\leq 3.3V$ .

#### SW Pins

The SW pins are generally for testing purposes by monitoring these pins. These pins can also be used to dampen out switch node ringing caused by LC parasitic in the switched current paths. Usually a series R-C combination is used called a snubber circuit. The resistor will dampen the resonance and the capacitor is chosen to only affect the high frequency ringing across the resistor. If the stray inductance or capacitance can be measured or approximated then a somewhat analytical technique can be used to select the snubber values. The inductance is usually easier to predict. It combines the power path board inductance in combination with the MOSFET interconnect bond wire inductance.

First the SW pin can be monitored with a wide bandwidth scope with a high frequency scope probe. The ring frequency can be measured for its value. The impedance Z can be calculated:

$Z(L) = 2\pi fL$ ,

where f is the resonant frequency of the ring, and L is the total parasitic inductance in the switch path. If a resistor is selected that is equal to Z, then the ringing should be dampened. The snubber capacitor value is chosen so that its impedance is equal to the resistor at the ring frequency. Calculated by:  $Z(C) = 1/(2\pi fC)$ . These values are a good place to start with. Modification to these components should be made to attenuate the ringing with the least amount of power loss.

#### Temperature Monitoring (TEMP)

A diode connected PNP transistor is used for the TEMP monitor function by monitoring its voltage over temperature. The temperature dependence of this diode can be understood in the equation:

$$\mathsf{D} = \mathsf{nVTIn}\left(\frac{\mathsf{ID}}{\mathsf{IS}}\right)$$

Where  $V_T$  is the thermal voltage (kT/q), and n, the ideality factor is 1 for the two diode connected PNPs being used in the LTM4620. Since  $I_D$  has an exponential temperature dependence that can be understood from the typical empirical equation for  $I_S$ :

$$I_{S} = I_{0} \exp \left(-VG0/VT\right),$$

Where  $I_0$  is some process and geometry dependent current ( $I_0$  is typically around 20 orders of magnitude larger than  $I_S$  at room temperature, so  $I_0$  is much larger than typical

values of I<sub>D</sub>), and VG0 is the band gap voltage of 1.2V extrapolated to absolute zero of  $-273^{\circ}$ C Kelvin. Figure 8 shows a plot of the diode temperature characteristic of the diode connected PNP transistor biased with a 100µA current source. This plot would extend to the left back to 1.2V at  $-273^{\circ}$ C Kelvin. This curve is stop at  $-55^{\circ}$ C due to the test system limits.

If we take the  $I_{\mbox{\scriptsize S}}$  equation and substitute into the  $V_{\mbox{\scriptsize D}}$  equation, then we get:

$$VD = VGO - \left(\frac{Kt}{q}\right) In \left(\frac{IO}{ID}\right), V_T = \left(\frac{kT}{q}\right)$$

The expression shows that the junction voltage of the PNP connected diode decreases linearly if  $I_0$  were constant from a value VG0 of 1.2V at absolute zero to a decreasing value with increased temperature.

If we take this equation and differentiate it with respect to temperature T, then:

$$\frac{dVD}{dT} = -(VG0 - VD) / T \text{ This } \frac{dVD}{dT}$$

change as a function of temperature is the typical ~-2mV/°C. This equation is simplified for the first order derivation.

Solving for T, T = -(VGO - VD)/dVD provide the temperature.

1st Example: Figure 4 for 27°C, or 300°C Kelvin the diode voltage is 0.598V, thus,  $300^{\circ}C = -(1200mV - 598mV)/$ -2mV/°C)

2nd Example: Figure 4 for 75°C, or 350°C Kelvin the diode voltage is 0.50V, thus, 350°C = -(1200mV - 500mV)/-2mV/°C)

Converting the Kelvin scale to Celsius is simply taking the Kelvin temp and subtracting –273°C Kelvin from it.

A typical forward voltage is measured and placed in the electrical characteristics section of the data sheet, and Figure 8 is the plot of this forward voltage. Measure this forward voltage at 27°C to establish a reference point. Then use the above expression while measuring the

Figure 8. Diode Voltage  $V_D$  vs Temperature  $T(^\circ C)$  for Different Bias Currents

forward voltage over temperature will provide a general temperature monitor.

The diode connected PNP transistor can be pulled up to  $V_{IN}$  with a resistor to set the current to 100µA for using this diode connected transistor as a general temperature monitor by monitoring the diode voltage drop with temperature. See Figure 27 for an example.

#### **Thermal Considerations and Output Current Derating**

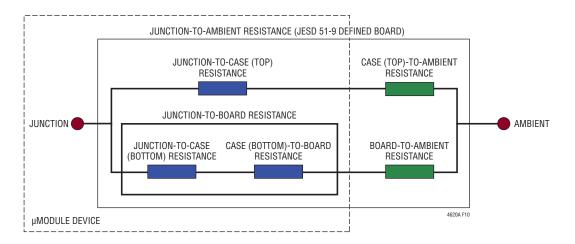

The thermal resistances reported in the Pin Configuration section of the data sheet are consistent with those parameters defined by JESD 51-9 and are intended for use with finite element analysis (FEA) software modeling tools that leverage the outcome of thermal modeling, simulation, and correlation to hardware evaluation performed on a  $\mu$ Module package mounted to a hardware test board also defined by JESD 51-9 ("Test Boards for Area Array Surface Mount Package Thermal Measurements"). The motivation for providing these thermal coefficients in found in JESD 51-12 ("Guidelines for Reporting and Using Electronic Package Thermal Information").

Many designers may opt to use laboratory equipment and a test vehicle such as the demo board to anticipate the  $\mu$ Module regulator's thermal performance in their application at various electrical and environmental operating

4620afc

conditions to compliment any FEA activities. Without FEA software, the thermal resistances reported in the Pin Configuration section are in-and-of themselves not relevant to providing guidance of thermal performance; instead, the derating curves provided in the data sheet can be used in a manner that yields insight and guidance pertaining to one's application-usage, and can be adapted to correlate thermal performance to one's own application.

The Pin Configuration section typically gives four thermal coefficients explicitly defined in JESD 51-12; these coefficients are quoted or paraphrased below:

- 1.  $\theta_{JA}$ , the thermal resistance from junction to ambient, is the natural convection junction-to-ambient air thermal resistance measured in a one cubic foot sealed enclosure. This environment is sometimes referred to as "still air" although natural convection causes the air to move. This value is determined with the part mounted to a JESD 51-9 defined test board, which does not reflect an actual application or viable operating condition.

- 2.  $\theta_{JCbottom}$ , the thermal resistance from junction to the bottom of the product case, is the junction-to-board thermal resistance with all of the component power dissipation flowing through the bottom of the package. In the typical µModule, the bulk of the heat flows out the bottom of the package, but there is always heat flow out into the ambient environment. As a result, this thermal resistance value may be useful for comparing packages but the test conditions don't generally match the user's application.

- 3.  $\theta_{JCtop}$ , the thermal resistance from junction to top of the product case, is determined with nearly all of the component power dissipation flowing through the top

of the package. As the electrical connections of the typical  $\mu$ Module are on the bottom of the package, it is rare for an application to operate such that most of the heat flows from the junction to the top of the part. As in the case of  $\theta_{JCbottom}$ , this value may be useful for comparing packages but the test conditions don't generally match the user's application.

4.  $\theta_{JB}$ , the thermal resistance from junction to the printed circuit board, is the junction-to-board thermal resistance where almost all of the heat flows through the bottom of the  $\mu$ Module and into the board, and is really the sum of the  $\theta_{JCbottom}$  and the thermal resistance of the bottom of the part through the solder joints and through a portion of the board. The board temperature is measured a specified distance from the package, using a two sided, two layer board. This board is described in JESD 51-9.

A graphical representation of the aforementioned thermal resistances is given in Figure 9; blue resistances are contained within the  $\mu$ Module regulator, whereas green resistances are external to the  $\mu$ Module.

As a practical matter, it should be clear to the reader that no individual or sub-group of the four thermal resistance parameters defined by JESD 51-12 or provided in the Pin Configuration section replicates or conveys normal operating conditions of a  $\mu$ Module. For example, in normal board-mounted applications, never does 100% of the device's total power loss (heat) thermally conduct exclusively through the top or exclusively through bottom of the  $\mu$ Module—as the standard defines for  $\theta_{JCtop}$  and  $\theta_{JCbottom}$ , respectively. In practice, power loss is thermally dissipated in both directions away from the package—granted, in the absence of a heat sink and airflow, a majority of the heat flow is into the board.

Within a SIP (system-in-package) module, be aware there are multiple power devices and components dissipating power, with a consequence that the thermal resistances relative to different junctions of components or die are not exactly linear with respect to total package power loss. To reconcile this complication without sacrificing modeling simplicity—but also, not ignoring practical realities—an approach has been taken using FEA software modeling along with laboratory testing in a controlled-environment chamber to reasonably define and correlate the thermal resistance values supplied in this data sheet: (1) Initially. FEA software is used to accurately build the mechanical geometry of the µModule and the specified PCB with all of the correct material coefficients along with accurate power loss source definitions; (2) this model simulates a software-defined JEDEC environment consistent with JESD 51-9 to predict power loss heat flow and temperature readings at different interfaces that enable the calculation of the JEDEC-defined thermal resistance values: (3) the model and FEA software is used to evaluate the

µModule with heat sink and airflow; (4) having solved for and analyzed these thermal resistance values and simulated various operating conditions in the software model. a thorough laboratory evaluation replicates the simulated conditions with thermocouples within a controlled-environment chamber while operating the device at the same power loss as that which was simulated. An outcome of this process and due-diligence yields a set of derating curves provided in other sections of this data sheet. After these laboratory test have been performed and correlated to the  $\mu$ Module model, then the  $\theta_{JB}$  and  $\theta_{BA}$  are summed together to correlate guite well with the µModule model with no airflow or heat sinking in a properly define chamber. This  $\theta_{IB} + \theta_{BA}$  value is shown in the Pin Configuration section and should accurately equal the  $\theta_{IA}$  value because approximately 100% of power loss flows from the junction through the board into ambient with no airflow or top mounted heat sink. Each system has its own thermal characteristics, therefore thermal analysis must be performed by the user in a particular system.

Figure 9. Graphical Representation of JESD 51-12 Thermal Coefficients

4620afr

The LTM4620A module has been designed to effectively remove heat from both the top and bottom of the package. The bottom substrate material has very low thermal resistance to the printed circuit board and the exposed top metal is thermally connected to the power devices and the power inductors. An external heat sink can be applied to the top of the device for excellent heat sinking with airflow. Basically all power dissipating devices are mounted directly to the substrate and the top exposed metal. This provides two low thermal resistance paths to remove heat.

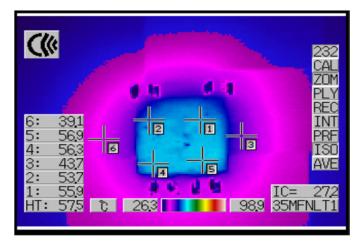

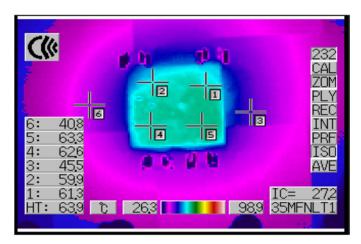

Figure 10 shows a temperature plot of the LTM4620A with BGA heat sink and 200LFM airflow with ~5.3W of internal dissipation.

Figure 11 shows a temperature plot of the LTM4620A with no heat sink and 200LFM airflow with ~6.5W of internal dissipation.

These plots equate to a paralleled 1.2V at 26A design, and a 5V at 25A design operating from a 12V input.

#### Safety Considerations

The LTM4620A modules do not provide isolation from  $V_{\rm IN}$  to  $V_{\rm OUT}$ . There is no internal fuse. If required, a slow blow fuse with a rating twice the maximum input current needs to be provided to protect each unit from catastrophic failure.

The fuse or circuit breaker should be selected to limit the current to the regulator during overvoltage in case of an internal top MOSFET fault. If the internal top MOSFET fails, then turning it off will not resolve the overvoltage, thus the internal bottom MOSFET will turn on indefinitely trying to protect the load. Under this fault condition, the input voltage will source very large currents to ground through the failed internal top MOSFET and enabled internal bottom MOSFET. This can cause excessive heat and board damage depending on how much power the input voltage can deliver to this system. A fuse or circuit breaker can be used as a secondary fault protector in this situation.

Figure 10. LTM4620A 12V to 1.2V at 26A with 200LFM Airflow

Figure 11. LTM4620A 12V to 5V at 25A with 200LFM Airflow

The device does support over current protection. A temperature diode is provided for monitoring internal temperature, and can be used to detect the need for thermal shutdown that can be done by controlling the RUN pin.

#### **Power Derating**