#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND                           | 0.3V to +6V                      |

|--------------------------------------------------|----------------------------------|

| OUT, SAG, SHDN to GND                            | 0.3V to (V <sub>CC</sub> + 0.3V) |

| IN to GND (Note 1)                               |                                  |

| IN Short-Circuit Duration from -0.3V to          | V <sub>CLP</sub> 1min            |

| Output Short-Circuit Duration to V <sub>CC</sub> | or GND Continuous                |

| Continuous Power Dissipation ( $T_A = +$         | +70°C)                           |

| 6-Pin SOT23 (derate 8.7mW/°C abo                 | ove +70°C)695mW                  |

| 6-Pin SC70 (derate 3.1mW/°C abov                 | /e +70°C)245mW                   |

| Operating Temperature Range  | 40°C to +85°C  |

|------------------------------|----------------|

| Junction Temperature         | +150°C         |

| Storage Temperature Range    | 65°C to +150°C |

| Lead Temperature (soldering, | 10s)+300°C     |

Note 1: V<sub>CLP</sub> is the input clamp voltage as defined in the *DC Electrical Characteristics* table.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = 5.0V, GND = 0V, C_{IN} = 0.1\mu F \text{ from IN to GND, R}_{L} = \text{infinity to GND, SAG shorted to OUT, } \overline{SHDN} = 5.0V, T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C.$  Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 2)

| PARAMETER                    | SYMBOL                            | CONDITIONS                                                        |                          | MIN                   | TYP   | MAX                   | UNITS |

|------------------------------|-----------------------------------|-------------------------------------------------------------------|--------------------------|-----------------------|-------|-----------------------|-------|

| Supply Voltage Range         | Vcc                               | Guaranteed by PSRR                                                |                          | 4.5                   |       | 5.5                   | V     |

| Quiescent Supply Current     | Icc                               | VIN = VCLP                                                        |                          |                       | 6.5   | 10                    | mΑ    |

| Shutdown Supply Current      | ISHDN                             | SHDN = 0V                                                         |                          |                       | 0.15  | 1                     | μΑ    |

| Input Clamp Voltage          | V <sub>CLP</sub>                  | Input referred                                                    |                          | 0.27                  | 0.38  | 0.47                  | V     |

| Input Voltage Range          | VIN                               | Inferred from voltage gain (Note 3)                               |                          | V <sub>CLP</sub>      |       | 1.45                  | V     |

| Input Bias Current           | IBIAS                             | V <sub>IN</sub> = 1.45V                                           |                          |                       | 22.5  | 35                    | μΑ    |

| Input Resistance             |                                   | V <sub>CLP</sub> + 0.5V < V <sub>IN</sub> < V <sub>CLP</sub> + 1V |                          |                       | 3     |                       | МΩ    |

| Voltage Gain                 | A <sub>V</sub>                    | $R_L = 150\Omega$ to GND, 0.5V < $V_{IN}$ < 1.45V (Note 4)        |                          | 1.9                   | 2     | 2.1                   | V/V   |

| Power-Supply Rejection Ratio | PSRR                              | 4.5V < V <sub>CC</sub> < 5.5V                                     |                          | 60                    | 80    |                       | dB    |

| Output Voltage High Swing    | Voh                               | $R_L = 150\Omega$ to GND                                          |                          | 4.3                   | 4.6   |                       | V     |

| Output Voltage Low Swing     | V <sub>OL</sub>                   | $R_L = 150\Omega$ to GND                                          |                          |                       | VCLP  | 0.47                  | V     |

|                              |                                   | Sourcing, $R_L = 20\Omega$ to GND                                 |                          | 45                    | 85    |                       | ^     |

| Output Current IO            |                                   | Sinking, $R_L = 20\Omega$ to $V_{CC}$                             |                          | 40                    | 85    |                       | mA    |

| Output Short-Circuit Current | Isc                               | OUT shorted to V <sub>CC</sub> or GND                             |                          |                       | 110   |                       | mA    |

| SHDN Logic-Low Threshold     | VIL                               |                                                                   |                          |                       |       | V <sub>CC</sub> x 0.3 | V     |

| SHDN Logic-High Threshold    | VIH                               |                                                                   |                          | V <sub>CC</sub> x 0.7 | 7     |                       | V     |

| SHDN Input Current           | I <sub>IH</sub> , I <sub>IL</sub> |                                                                   |                          |                       | 0.003 | 1                     | μΑ    |

| Shutdown Output Impedance    | R <sub>OUT</sub> (Disabled)       | SHDN = 0V                                                         | At DC                    |                       | 4     |                       |       |

|                              |                                   |                                                                   | At 3.58MHz or<br>4.43MHz |                       | 2     |                       | kΩ    |

#### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC}=5.0V,~GND=0V,~C_{OUT}=C_{SAG}=22\mu F,~C_{IN}=0.1\mu F,~R_{IN}=75\Omega$  to GND,  $R_{L}=150\Omega$  to GND,  $\overline{SHDN}=5.0V,~T_{A}=+25^{\circ}C,$  unless otherwise noted.)

| PARAMETER                        | SYMBOL                | CONDITIONS                                                                                                     | MIN | TYP | MAX | UNITS   |

|----------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------|-----|-----|-----|---------|

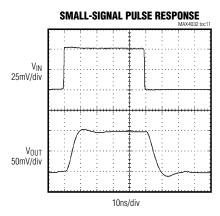

| Small-Signal -3dB Bandwidth      | BW <sub>SS</sub>      | $V_{OUT} = 100 \text{mV}_{P-P}$                                                                                |     | 55  |     | MHz     |

| Large-Signal -3dB Bandwidth      | BW <sub>LS</sub>      | V <sub>OUT</sub> = 2V <sub>P-P</sub>                                                                           |     | 45  |     | MHz     |

| Small-Signal 0.1dB Gain Flatness | BW <sub>0.1dBSS</sub> | $V_{OUT} = 100 \text{mV}_{P-P}$                                                                                |     | 18  |     | MHz     |

| Large-Signal 0.1dB Gain Flatness | BW <sub>0.1dBLS</sub> | V <sub>OUT</sub> = 2V <sub>P-P</sub>                                                                           |     | 17  |     | MHz     |

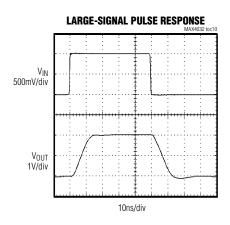

| Slew Rate                        | SR                    | V <sub>OUT</sub> = 2V step                                                                                     |     | 275 |     | V/µs    |

| Settling Time to 0.1%            | ts                    | V <sub>OUT</sub> = 2V step                                                                                     |     | 25  |     | ns      |

| Power-Supply Rejection Ratio     | PSRR                  | f = 100kHz                                                                                                     |     | 50  |     | dB      |

| Output Impedance                 | Zout                  | f = 5MHz                                                                                                       |     | 2.5 |     | Ω       |

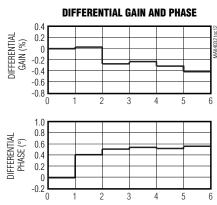

| Differential Gain                | DG                    | NTSC                                                                                                           |     | 0.4 |     | %       |

| Differential Phase               | DP                    | NTSC                                                                                                           |     | 0.6 |     | Degrees |

| Group Delay                      | D/dT                  | f = 3.58MHz or 4.43MHz                                                                                         |     | 20  |     | ns      |

| Peak Signal to RMS Noise         | SNR                   | V <sub>IN</sub> = 1V <sub>P-P</sub> , 10MHz BW                                                                 |     | 65  |     | dB      |

| Droop                            |                       | $C_{IN} = 0.1 \mu F \text{ (Note 4)}$                                                                          |     | 2   | 3   | %       |

| SHDN Enable Time                 | ton                   | $V_{IN} = V_{CLP} + 1V$ , $\overline{SHDN} = 5V$ , $V_{OUT}$ settled to within 1% of the final voltage         |     | 250 |     | ns      |

| SHDN Disable Time                | toff                  | V <sub>IN</sub> = V <sub>CLP</sub> + 1V, SHDN = 0V, V <sub>OUT</sub> settled to below 1% of the output voltage |     | 50  |     | ns      |

Note 2: All devices are 100% production tested at TA = +25°C. Specifications over temperature limits are guaranteed by design.

Note 3: Voltage gain (A<sub>V</sub>) is referenced to the clamp voltage, i.e., an input voltage of V<sub>IN</sub> = V<sub>CLP</sub> + VI would produce an output voltage of V<sub>OUT</sub> = V<sub>CLP</sub> + A<sub>V</sub> x VI.

**Note 4:** Droop is guaranteed by the input bias current specification.

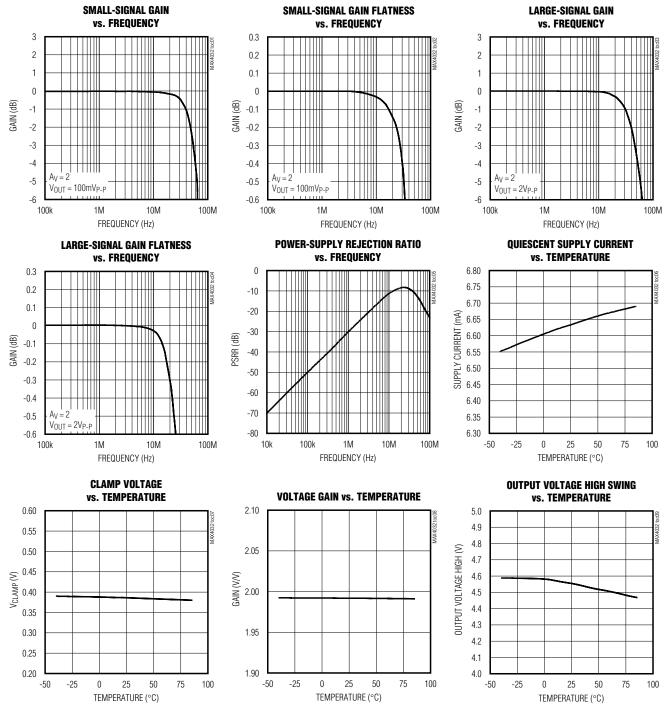

### Typical Operating Characteristics

$(V_{CC}=5.0V,~GND=0V,~C_{OUT}=C_{SAG}=22\mu F,~C_{IN}=0.1\mu F,~R_{IN}=75\Omega$  to GND,  $R_{L}=150\Omega$  to GND,  $\overline{SHDN}=V_{CC},~T_{A}=+25^{\circ}C,~unless~otherwise~noted.)$

### **Typical Operating Characteristics (continued)**

$(V_{CC}=5.0V,~GND=0V,~C_{OUT}=C_{SAG}=22\mu F,~C_{IN}=0.1\mu F,~R_{IN}=75\Omega$  to GND,  $R_{L}=150\Omega$  to GND,  $\overline{SHDN}=V_{CC},~T_{A}=+25^{\circ}C,~unless$  otherwise noted.)

### **Pin Description**

| PIN | NAME | FUNCTION                                                                                       |

|-----|------|------------------------------------------------------------------------------------------------|

| 1   | OUT  | Video Output                                                                                   |

| 2   | GND  | Ground                                                                                         |

| 3   | IN   | Video Input                                                                                    |

| 4   | Vcc  | Power-Supply Voltage. Bypass with a 0.1µF capacitor to ground as close to the pin as possible. |

| 5   | SHDN | Shutdown. Pull SHDN low to place the MAX4032 in low-power shutdown mode.                       |

| 6   | SAG  | Sag Correction                                                                                 |

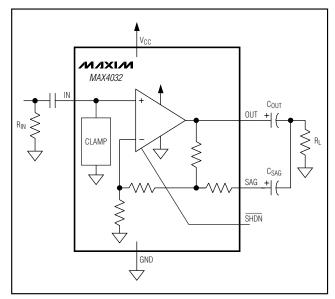

### **Typical Application Circuit**

### **Detailed Description**

The MAX4032 5V, 6dB video buffer with sync-tip clamp, output sag correction, and low-power shutdown mode is available in tiny SOT23 and SC70 packages. The sag-corrected output of the MAX4032 is designed to drive AC-coupled,  $150\Omega$  back-terminated video loads in portable video applications such as digital still cams, portable DVD players, digital camcorders, PDAs, video-enabled cell phones, portable game systems, and notebook computers. The sag correction feature introduces low-frequency compensation that reduces the value of the normally bulky and expensive  $330\mu\text{F}$  AC-coupling capacitor to two small, less expensive  $22\mu\text{F}$  capacitors. The input clamp positions the video waveform at the output and allows the MAX4032 to be used as either an AC- or DC-coupled output driver.

The MAX4032 operates from a single 5V supply and consumes only 6.5mA of supply current. The low-power shutdown mode reduces the supply current to 150nA, making the MAX4032 ideal for low-voltage, battery-powered video applications.

The input signal to the MAX4032 is AC-coupled through a capacitor into an active sync-tip clamp circuit, which places the minimum of the video signal at approximately 0.38V. The output buffer amplifies the video signal while still maintaining the 0.38V clamp voltage at the output. For example, if  $V_{IN} = 0.38V$ , then  $V_{OUT} = 0.38V$ . If  $V_{IN} = (0.38V + 1V) = 1.38V$ , then  $V_{OUT} = (0.38V + 2 X (1V)) = 2.38V$  when SAG is shorted OUT.

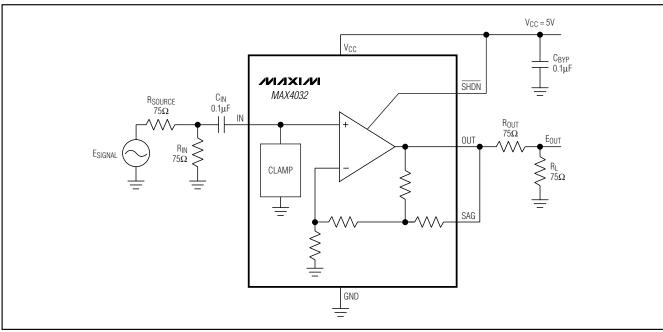

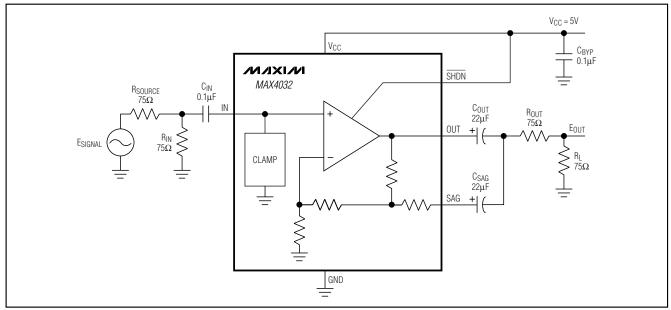

There are two common output connections for the MAX4032:

- 1) SAG is shorted to OUT and  $150\Omega$  is directly connected from OUT to ground (see Figure 2).

- 2) Two capacitors and  $150\Omega$  are connected between OUT, SAG, and ground (see Figure 3).

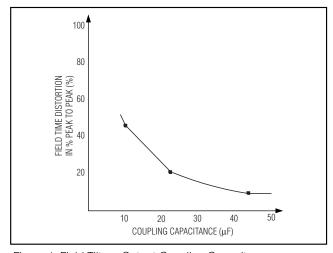

#### Sag Correction

Sag correction refers to the low-frequency compensation of the highpass filter formed by the  $150\Omega$  load of a back-terminated coax and the output-coupling capacitor. This break point must be low enough in frequency to pass the Vertical Sync Interval (<25Hz for PAL and <30Hz for NTSC) to avoid Field Tilt. Traditionally, the break point is made <3~5Hz, and the coupling capacitor must be very large, typically >330µF. The MAX4032 reduces the value of this coupling capacitor, replacing it with a pair of 22µF capacitors. This is done by putting a resistor network in series with the feedback, raising the gain, and creating a high-impedance node at the SAG output. This node is AC-coupled to the load in par-

allel with the normal output, as shown in Figure 3. This allows the use of two smaller capacitors ( $C_{OUT}$  and  $C_{SAG}$ ), typically 22 $\mu$ F, substantially reducing the size of the interface caps and their cost while retaining the low-frequency response.

The minimum value of the output-coupling capacitor is a function of the acceptable Field Tilt. In Figure 1, the Field Tilt is given for several values of capacitance from  $10\mu F$  to  $47\mu F$  for comparison. Although values lower than  $22\mu F$  may have acceptable Field Tilt, they are not recommended, since tolerance, aging, and voltage and temperature coefficients reduce the capacitance in actual applications. Increasing the output-coupling capacitors beyond  $47\mu F$  does not improve performance.

#### **Shutdown Mode**

The MAX4032 features a low-power shutdown mode (ISHDN = 150nA) for battery-powered/portable applications. Pulling the SHDN pin high enables the output. Connecting the SHDN pin to ground (GND) disables the output and places the MAX4032 into a low-power shutdown mode.

# Applications Information Input Coupling the MAX4032

The MAX4032 input must be AC-coupled because the input capacitor stores the clamp voltage. The MAX4032 requires a typical value of 0.1µF for the input clamp to meet the Line Droop specification. A minimum of a ceramic capacitor with an X7R temperature coefficient is recommended to avoid temperature-related problems with Line Droop. For extended temperature operation, such as outdoor applications, or where the impressed

Figure 1. Field Tilt vs. Output-Coupling Capacitance

Figure 2. DC-Coupling the MAX4032

Figure 3. AC-Coupling the MAX4032

voltage is close to the rated voltage of the capacitor, a film dielectric is recommended. Increasing the capacitor value slows the clamp capture time. Values above  $0.5\mu F$  should be avoided since they do not improve the clamp's performance.

The active sync-tip clamp also requires that the input impedance seen by the input capacitor be less than  $100\Omega$  typically to function properly. This is easily met by the  $75\Omega$  input resistor prior to the input-coupling capacitor and the back termination from a prior stage. Insufficient input resistance to ground causes the MAX4032 to appear to oscillate. Never operate the MAX4032 in this mode.

#### **Output Coupling the MAX4032**

The output of the MAX4032 can be AC- or DC-coupled to the load. In the DC-coupled mode, the MAX4032 provides accurate sync-tip clamping for single-supply operation and still can drive a  $150\Omega$ , back-terminated load. In the AC-coupled mode, the MAX4032 allows the use of minimal size capacitors to drive a back-terminated video load of  $150\Omega$ .

#### DC-Coupling the Output

By shorting SAG to OUT, the device becomes an amplifier with DC restore, optimally placing the video within the dynamic range of the output. In this mode, the MAX4032 can be used as the input conditioner for a video signal, providing gain and biasing in single-supply applications. DC-coupling also improves the MAX4032's performance in terms of differential gain and phase. This reflects the improvement in the low-frequency response due to DC-coupling.

AC-Coupling the Output

The MAX4032's output is configured to support AC-coupling with minimal capacitance. This is called "sag correction." It refers to the improved bandwidth achieved by using two smaller capacitors to replace a single large capacitor shown in Figure 3.

#### **Layout and Power-Supply Bypassing**

The MAX4032 operates from a single 5V supply. Bypass the supply with a 0.1µF capacitor as close to the pin as possible. Maxim recommends using microstrip and stripline techniques to obtain full bandwidth. To ensure that the PC board does not degrade the device's performance, design it for a frequency greater than 1GHz. Pay careful attention to inputs and outputs to avoid large parasitic capacitance. Whether or not you use a constant-impedance board, observe the following design guidelines:

- Do not use wire-wrap boards; they are too inductive.

- Do not use IC sockets; they increase parasitic capacitance and inductance.

- Use surface-mount instead of through-hole components for better, high-frequency performance.

- Use a PC board with at least two layers; it should be as free from voids as possible.

- Keep signal lines as short and as straight as possible.

Do not make 90° turns; round all corners.

**Chip Information**

TRANSISTOR COUNT: 755

PROCESS: BICMOS

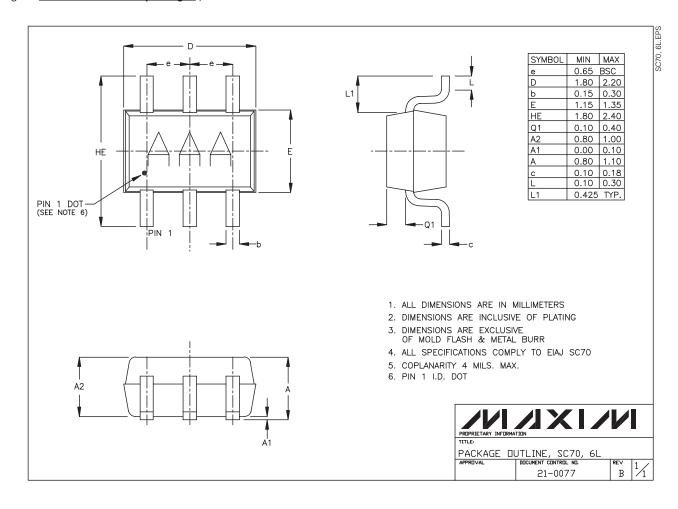

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

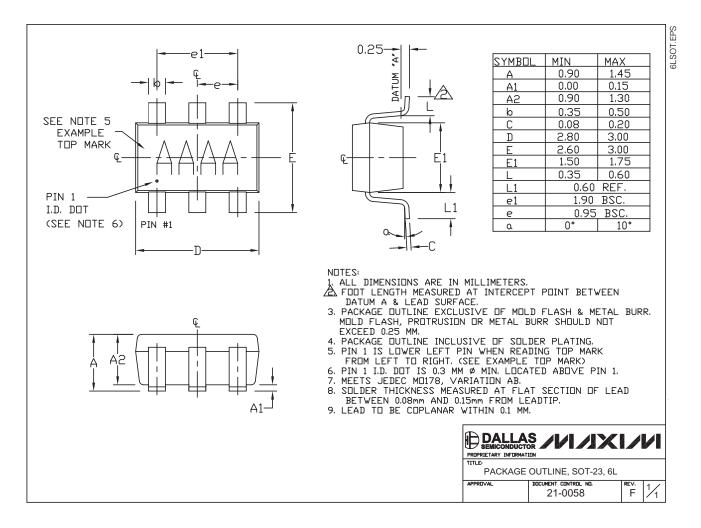

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated:

MAX4032ELT+T MAX4032EUT+T MAX4032EXT+T