#### ABSOLUTE MAXIMUM RATINGS

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                      |                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| AGND to PGND0.3V to +0.3V Operating Temperature Range40°C to +1 AVGLIMIT, REG, RT/CLKIN, CSP_, CSN_ to AGND0.3V to +6V Storage Temperature Range60°C to +1 | 17mW<br>62mW<br>125°C<br>150°C |

| All Other Pins to AGND0.3V to (V <sub>REG</sub> + 0.3V) Lead Temperature (soldering, 10s)+3  Soldering Temperature (reflow)+2                              |                                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### PACKAGE THERMAL CHARACTERISTICS (Note 1)

| TSSOP                                                        | TSSOP-EP                                           |

|--------------------------------------------------------------|----------------------------------------------------|

| Junction-to-Ambient Thermal Resistance (θJA)71.6°C/W         | Junction-to-Ambient Thermal Resistance (θJA)37°C/W |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> )13°C/W | Junction-to-Case Thermal Resistance (θJC)2°C/W     |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = V_{REG} = V_{DD} = V_{EN} = +5V, T_A = T_J = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted, circuit of Figure 6. Typical values are at  $T_A = +25$ °C.) (Note 2)

| PARAMETER                            | SYMBOL            | CONE                                               | DITIONS                                                        | MIN   | TYP    | MAX   | UNITS           |

|--------------------------------------|-------------------|----------------------------------------------------|----------------------------------------------------------------|-------|--------|-------|-----------------|

| SYSTEM SPECIFICATIONS                |                   |                                                    |                                                                |       |        |       |                 |

|                                      |                   |                                                    |                                                                | 5     |        | 28    |                 |

| Input Voltage Range                  | VIN               | IN and REG shorted operation                       | IN and REG shorted together for +5V operation                  |       |        | 5.50  | V               |

| Quiescent Supply Current             | I <sub>IN</sub>   | f <sub>OSC</sub> = 500kHz, DH_                     | or DL_ = open                                                  |       | 7      | 17    | mA              |

| STARTUP/INTERNAL REGULATO            | OR OUTPUT         | (REG)                                              |                                                                |       |        |       |                 |

| REG Undervoltage Lockout             | UVLO              | V <sub>REG</sub> rising                            |                                                                | 4.0   | 4.15   | 4.5   | V               |

| Hysteresis                           | V <sub>HYST</sub> |                                                    |                                                                |       | 200    |       | mV              |

| REG Output Accuracy                  |                   | $V_{IN} = 5.8V \text{ to } 28V, I_{S0}$            | V <sub>IN</sub> = 5.8V to 28V, I <sub>SOURCE</sub> = 0 to 65mA |       | 5.10   | 5.30  | V               |

| REG Dropout                          |                   | V <sub>IN</sub> < 5.8V, I <sub>SOURCE</sub> = 60mA |                                                                |       |        | 0.5   | V               |

| INTERNAL REFERENCE                   |                   |                                                    |                                                                |       |        |       |                 |

| Internal Reference Voltage           | VEAN_             | EAN_ connected to EAOUT_ (Note 3)                  | $T_A = -40^{\circ}\text{C to } + 125^{\circ}\text{C}$          | 0.605 | 0.6125 | 0.620 | V               |

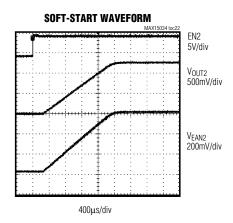

| Digital Ramp Period for Soft-Start   |                   |                                                    |                                                                |       | 1024   |       | Clock<br>cycles |

| Soft-Start Voltage Steps             |                   |                                                    |                                                                |       | 64     |       | Steps           |

| MOSFET DRIVERS                       |                   |                                                    |                                                                |       |        |       |                 |

| p-Channel Output Driver<br>Impedance | R <sub>ON_P</sub> |                                                    |                                                                |       | 1.35   | 3     | Ω               |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = V_{REG} = V_{DD} = V_{EN} = +5V, T_A = T_J = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted, circuit of Figure 6. Typical values are at } T_A = +25^{\circ}\text{C.})$  (Note 2)

| PARAMETER                                                  | SYMBOL                               | CONDITIONS                                                                           | MIN  | TYP                   | MAX   | UNITS           |

|------------------------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------|------|-----------------------|-------|-----------------|

| n-Channel Output Driver<br>Impedance                       | R <sub>ON_N</sub>                    |                                                                                      |      | 0.45                  | 1.35  | Ω               |

| Output Driver Source Current                               | I <sub>DH</sub> _, I <sub>DL</sub> _ |                                                                                      |      | 2.5                   |       | А               |

| Output Driver Sink Current                                 | I <sub>DH_</sub> , I <sub>DL_</sub>  |                                                                                      |      | 5                     |       | А               |

| Nonoverlap Time (Dead Time)                                | tNO                                  | C <sub>DH</sub> _ or C <sub>DL</sub> _ = 5nF                                         | -7.5 |                       | +7.5  | . %             |

| Nonovenap Time (Dead Time)                                 | tNO                                  | $f_{SW} = 1MHz$ nominal, $R_{RT} = 12.4k\Omega$                                      | -10  |                       | +10   | /0              |

| RT/CLKIN Output Voltage                                    | V <sub>RT/CLKIN</sub>                |                                                                                      |      | 1.225                 |       | V               |

| RT/CLKIN Current Sourcing Capability                       | IRT/CLKIN                            |                                                                                      |      | 0.5                   |       | mA              |

| RT/CLKIN Logic-High Threshold                              | V <sub>RT/CLKIN</sub> H              |                                                                                      | 2.4  |                       |       | V               |

| RT/CLKIN Logic-Low Threshold                               | VRT/CLKIN_L                          |                                                                                      |      |                       | 0.8   | V               |

| RT/CLKIN High Pulse Width                                  | trt/clkin                            |                                                                                      |      | 30                    |       | ns              |

| RT/CLKIN Synchronization<br>Frequency Range                | fRT/CLKIN                            |                                                                                      | 200  |                       | 2000  | kHz             |

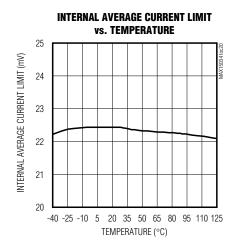

| CURRENT LIMIT                                              |                                      |                                                                                      |      |                       |       |                 |

| Internal Average Current-Limit Threshold                   | V <sub>CL</sub> _                    | VCSP VCSN_                                                                           | 20.4 | 22.5                  | 24.75 | mV              |

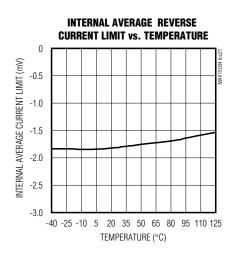

| Reverse Average Current-Limit<br>Threshold                 | V <sub>RCL</sub>                     | VCSP VCSN_                                                                           | -3.0 | -1.53                 | -0.1  | mV              |

| External Average Current-Limit Threshold Adjustment        | V <sub>CL_ADJ</sub>                  | Resistor-divider connected from REG to AVGLIMIT to AGND                              | \    | VAVGLIMIT -<br>0.6/36 |       | V               |

| AVGLIMIT Ground Threshold Voltage                          | VAVGLIMIT_GND                        |                                                                                      |      | 550                   |       | mV              |

| Leakage Current at AVGLIMIT                                | IAVGLIMIT                            | VAVGLIMIT = 3V                                                                       |      |                       | 100   | nA              |

| DIGITAL FAULT INTEGRATION                                  | (DF_)                                |                                                                                      |      |                       |       |                 |

| Number of Switching Cycles to<br>Shutdown in Current Limit | NS <sub>DF</sub> _                   |                                                                                      |      | 32,768                |       | Clock<br>cycles |

| Number of Switching Cycles to Recover from Shutdown        | NR <sub>DF</sub> _                   |                                                                                      |      | 524,288               |       | Clock<br>cycles |

| CURRENT-SENSE AMPLIFIER                                    | ı                                    | '                                                                                    | ı    |                       |       |                 |

| CSP_ to CSN_ Input Resistance                              | Rcs_                                 |                                                                                      |      | 3.8                   |       | kΩ              |

|                                                            | V <sub>CMR</sub> (CS)                | V <sub>IN</sub> = V <sub>REG</sub> = 4.75V to 5.5V or<br>V <sub>IN</sub> = 5V to 10V | -0.3 |                       | +3.6  | V               |

| Common-Mode Range                                          | V CIVIR(CS)                          |                                                                                      |      |                       |       |                 |

| Common-Mode Range                                          | VCIVIR(CS)                           | V <sub>IN</sub> = 7V to 28V                                                          | -0.3 |                       | +5.5  | V               |

| Common-Mode Range Input Offset Voltage                     | VOS(CS)                              | V <sub>IN</sub> = 7V to 28V                                                          | -0.3 | 100                   | +5.5  | V<br>µV         |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = V_{REG} = V_{DD} = V_{EN} = +5V, T_A = T_J = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted, circuit of Figure 6. Typical values are at  $T_A = +25$ °C.) (Note 2)

| PARAMETER                                                                                 | SYMBOL                     | CONDITIONS                         | MIN  | TYP    | MAX   | UNITS           |  |

|-------------------------------------------------------------------------------------------|----------------------------|------------------------------------|------|--------|-------|-----------------|--|

| -3dB Bandwidth                                                                            | f <sub>-3dB</sub>          |                                    |      | 4      |       | MHz             |  |

| CCD Innut Dies Courset                                                                    | 1                          | V <sub>CSP</sub> _ = 5.5V, sinking |      |        | 120   |                 |  |

| CSP_ Input Bias Current                                                                   | ICSA(IN)                   | V <sub>CSP</sub> _ = 0V, sourcing  |      |        | 30    | μΑ              |  |

| <b>CURRENT-ERROR AMPLIFIER (</b>                                                          | CEA_)                      |                                    |      |        |       |                 |  |

| Transconductance                                                                          | Яm                         |                                    |      | 550    |       | μS              |  |

| Open-Loop Gain                                                                            | AVOL(CEA)                  | No load                            |      | 50     |       | dB              |  |

| <b>VOLTAGE-ERROR AMPLIFIER (</b>                                                          | EAOUT_)                    |                                    |      |        |       |                 |  |

| Open-Loop Gain                                                                            | AVOL(EA)                   |                                    |      | 70     |       | dB              |  |

| Unity-Gain Bandwidth                                                                      | fUGEA                      |                                    |      | 3      |       | MHz             |  |

| EAN_ Input Bias Current                                                                   | IBIAS(EA)                  | V <sub>EAN</sub> _ = 2.0V          |      | 100    |       | nA              |  |

| Error-Amplifier Output Clamping<br>High Voltage                                           | V <sub>CLMP</sub> _HI (EA) | With respect to V <sub>CM</sub>    |      | 1      |       | V               |  |

| Error-Amplifier Output Clamping<br>Low Voltage                                            | V <sub>CLMP_LO</sub> (EA)  | With respect to V <sub>CM</sub>    |      | -0.234 |       | V               |  |

| EN_ INPUTS                                                                                |                            |                                    | •    |        |       |                 |  |

| EN_ Input High Voltage                                                                    | V <sub>ENH</sub>           | EN rising                          | 1.2  | 1.222  | 1.245 |                 |  |

| EN_ Hysteresis                                                                            |                            |                                    |      | 0.05   |       | V               |  |

| EN_ Input Leakage Current                                                                 | I <sub>EN</sub>            |                                    | -200 |        | +200  | nA              |  |

| Startup Delay Time to OUT_                                                                | tstart_delay               | From EN_ rising to VOUT_ rising    |      | 1      |       | ms              |  |

| MODE INPUT                                                                                |                            | •                                  |      |        | •     |                 |  |

| MODE Logic-High Threshold                                                                 | V <sub>MODE</sub> _H       |                                    | 2.4  |        |       | V               |  |

| MODE Logic-Low Threshold                                                                  | V <sub>MODE_L</sub>        |                                    |      |        | 0.8   | V               |  |

| MODE Input Pulldown                                                                       | Ipulldwn                   |                                    |      | 5      |       | μA              |  |

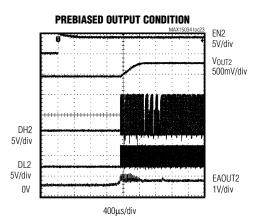

| PREBIASED OUTPUT                                                                          |                            |                                    |      |        |       |                 |  |

| Peak Sink Current-Limit<br>Threshold during Reference<br>Soft-Start                       |                            | VCSP VCSN_                         |      | -2.1   |       | mV              |  |

| Digital Ramp Period for<br>Stepping Peak Sink Current<br>Limit after Reference Soft-Start |                            |                                    |      | 448    |       | Clock<br>cycles |  |

| THERMAL SHUTDOWN                                                                          |                            |                                    |      |        |       |                 |  |

| Thermal Shutdown                                                                          | T <sub>SHDN</sub>          |                                    |      | 160    |       | °C              |  |

| Thermal Shutdown Hysteresis                                                               | THYST                      |                                    |      | 10     |       | °C              |  |

Note 2: The device is 100% production tested at  $T_A = T_J = +125$ °C. Limits at  $T_A = -40$ °C and  $T_A = +25$ °C are guaranteed by design.

**Note 3:** The internal reference voltage accuracy is measured at the negative input of the error amplifiers (EAN\_). Output voltage accuracy must include external resistor-divider tolerances.

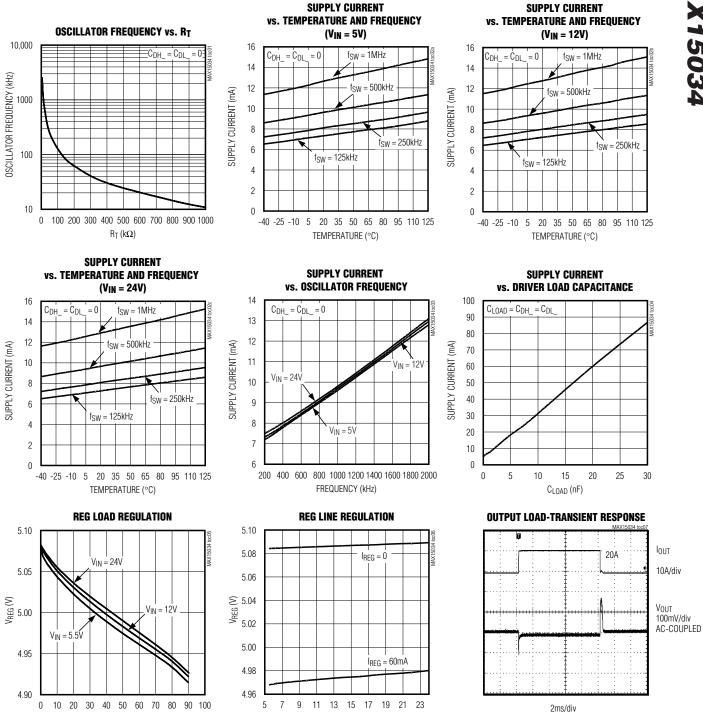

## Typical Operating Characteristics

(Circuit of Figure 6, TA = +25°C, unless otherwise noted. VIN = 12V, VOUT1 = 0.8V, VOUT2 = 1.3V, fSW = 500kHz per phase.)

V<sub>IN</sub> (V)

I<sub>REG</sub> (mA)

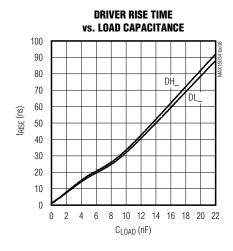

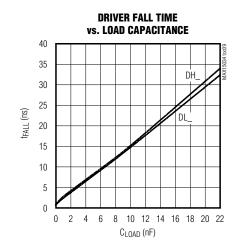

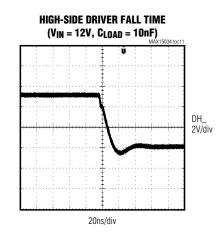

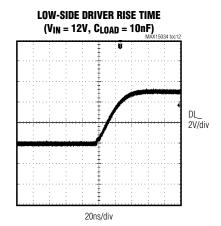

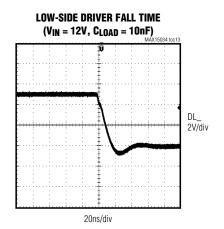

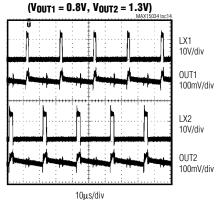

## Typical Operating Characteristics (continued)

(Circuit of Figure 6, T<sub>A</sub> = +25°C, unless otherwise noted. V<sub>IN</sub> = 12V, V<sub>OUT1</sub> = 0.8V, V<sub>OUT2</sub> = 1.3V, f<sub>SW</sub> = 500kHz per phase.)

## Typical Operating Characteristics (continued)

(Circuit of Figure 6, TA = +25°C, unless otherwise noted. VIN = 12V, VOUT1 = 0.8V, VOUT2 = 1.3V, fsw = 500kHz per phase.)

## OUT1/OUT2 OUT-OF-PHASE WAVEFORMS

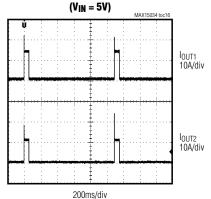

## SHORT-CIRCUIT CURRENT WAVEFORMS

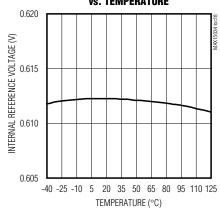

## INTERNAL REFERENCE VOLTAGE vs. TEMPERATURE

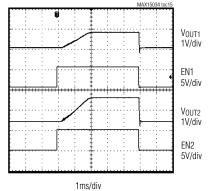

#### TURN-ON/TURN-OFF WAVEFORM

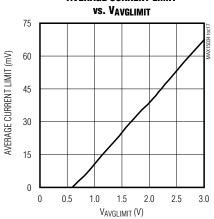

#### **AVERAGE CURRENT LIMIT**

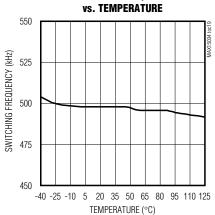

## SWITCHING FREQUENCY

## Typical Operating Characteristics (continued)

(Circuit of Figure 6, T<sub>A</sub> = +25°C, unless otherwise noted. V<sub>IN</sub> = 12V, V<sub>OUT1</sub> = 0.8V, V<sub>OUT2</sub> = 1.3V, f<sub>SW</sub> = 500kHz per phase.)

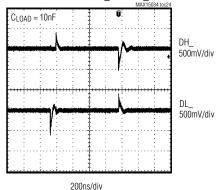

#### PEAK PULLUP AND PULLDOWN CURRENT OR DRIVER AT DH AND DL

8 \_\_\_\_\_\_\_ /N/XI/VI

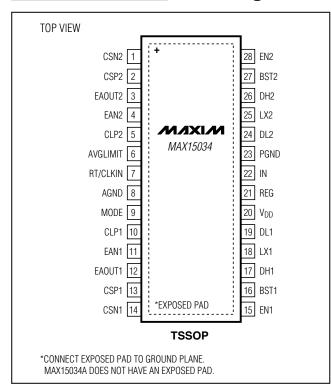

## **Pin Description**

| PIN | NAME     | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | CSN2     | Current-Sense Differential Amplifier Negative Input for Output 2. Connect CSN2 to the negative terminal of the sense resistor. The differential voltage between CSP2 and CSN2 is internally amplified by the current-sense amplifier ( $A_{V(CS)} = 36V/V$ ).                                                                                                                                                                                                                                               |

| 2   | CSP2     | Current-Sense Differential Amplifier Positive Input for Output 2. Connect CSP2 to the positive terminal of the sense resistor. The differential voltage between CSP2 and CSN2 is internally amplified by the current-sense amplifier (Av(CS) = 36V/V).                                                                                                                                                                                                                                                      |

| 3   | EAOUT2   | Voltage Error-Amplifier Output 2. Connect to an external gain-setting feedback resistor. The error-amplifier gain determines the output voltage load regulation for adaptive voltage positioning. This output also serves as the compensation network connection from EAOUT2 to EAN2. A resistive network results in a drooped output-voltage-regulation characteristic. An integrator configuration results in very tight output-voltage regulation (see the <i>Adaptive Voltage Positioning</i> section). |

| 4   | EAN2     | Voltage Error-Amplifier Inverting Input for Output 2. Connect a resistive divider from V <sub>OUT2</sub> to EAN2 to AGND to set the output voltage. A compensation network connects from EAOUT2 to EAN2. A resistive network results in a drooped output-voltage-regulation characteristic. An integrator configuration results in very tight output-voltage regulation (see the <i>Adaptive Voltage Positioning</i> section).                                                                              |

| 5   | CLP2     | Current-Error Amplifier Output 2. Compensate the current loop by connecting an R-C network from CLP2 to AGND.                                                                                                                                                                                                                                                                                                                                                                                               |

| 6   | AVGLIMIT | Average Current-Limit Programming. Connect a resistor-divider between REG, AVGLIMIT, and AGND to set the average current-limit value (see the <i>Programming Average the Current Limit</i> section).                                                                                                                                                                                                                                                                                                        |

| 7   | RT/CLKIN | External Clock Input or Internal Frequency-Setting Connection. Connect a resistor from RT/CLKIN to AGND to set the switching frequency. Connect an external clock at RT/CLKIN for external frequency synchronization.                                                                                                                                                                                                                                                                                       |

| 8   | AGND     | Analog Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 9   | MODE     | Mode Function Input. MODE selects between a single-output dual phase or a dual-output buck regulator. When MODE is grounded, VEA1 and VEA2 connect to CEA1 and CEA2, respectively (see Figure 1) and the device operates as a two-output, out-of-phase buck regulator. When MODE is connected to REG (logic high), VEA2 is disconnected and VEA1 is routed to both CEA1 and CEA2.                                                                                                                           |

| 10  | CLP1     | Current-Error Amplifier Output 1. Compensate the current loop by connecting an R-C network from CLP1 to AGND.                                                                                                                                                                                                                                                                                                                                                                                               |

| 11  | EAN1     | Voltage Error-Amplifier Inverting Input for Output 1. Connect a resistive divider from V <sub>OUT1</sub> to EAN1 to regulate the output voltage. A compensation network connects from EAOUT1 to EAN1. A resistive network results in a drooped output-voltage-regulation characteristic. An integrator configuration results in very tight output-voltage regulation (see the <i>Adaptive Voltage Positioning</i> section).                                                                                 |

| 12  | EAOUT1   | Voltage Error-Amplifier Output 1. Connect to an external gain-setting feedback resistor. The error-amplifier gain determines the output-voltage-load regulation for adaptive voltage positioning. This output also serves as the compensation network connection from EAOUT1 to EAN1. A resistive network results in a drooped output-voltage-regulation characteristic. An integrator configuration results in very tight output-voltage regulation (see the <i>Adaptive Voltage Positioning</i> section). |

| 13  | CSP1     | Current-Sense Differential Amplifier Positive Input for Output 1. Connect CSP1 to the positive terminal of the sense resistor. The differential voltage between CSP1 and CSN1 is internally amplified by the current-sense amplifier (Av(CS) = 36V/V).                                                                                                                                                                                                                                                      |

| 14  | CSN1     | Current-Sense Differential Amplifier Negative Input for Output 1. Connect CSN1 to the negative terminal of the sense resistor. The differential voltage between CSP1 and CSN1 is internally amplified by the current-sense amplifier ( $A_{V(CS)} = 36V/V$ ).                                                                                                                                                                                                                                               |

### Pin Description (continued)

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                                    |

|-----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | EN1             | Output 1 Enable. A logic-low shuts down channel 1's MOSFET drivers. EN1 can be used for output sequencing.                                                                                                                                                                                  |

| 16  | BST1            | Boost Flying-Capacitor Connection. Reservoir capacitor connection for the high-side MOSFET driver supply. Connect a 0.47µF ceramic capacitor between BST1 and LX1.                                                                                                                          |

| 17  | DH1             | High-Side Gate Driver Output 1. DH1 drives the gate of the high-side MOSFET.                                                                                                                                                                                                                |

| 18  | LX1             | External Inductor Connection and Source Connection for the High-Side MOSFET for Output 1. LX1 also serves as the return terminal for the high-side MOSFET driver.                                                                                                                           |

| 19  | DL1             | Low-Side Gate Driver Output 1. Gate driver output for the synchronous MOSFET.                                                                                                                                                                                                               |

| 20  | V <sub>DD</sub> | Supply Voltage for Low-Side Drivers. REG powers $V_{DD}$ . Connect a parallel combination of $0.1\mu F$ and $1\mu F$ ceramic capacitors from $V_{DD}$ to PGND and a $1\Omega$ resistor from $V_{DD}$ to REG to filter out the high-peak currents of the driver from the internal circuitry. |

| 21  | REG             | Internal 5V Regulator Output. REG is derived internally from IN and is used to power the internal bias circuitry. Bypass REG to AGND with a 4.7µF ceramic capacitor.                                                                                                                        |

| 22  | IN              | Supply Voltage Connection. Connect IN to a 5V to 28V input supply.                                                                                                                                                                                                                          |

| 23  | PGND            | Power Ground. Source connection for the low-side MOSFET. Connect V <sub>DD</sub> 's bypass capacitor returns to PGND.                                                                                                                                                                       |

| 24  | DL2             | Low-Side Gate Driver Output 2. Gate driver for the synchronous MOSFET.                                                                                                                                                                                                                      |

| 25  | LX2             | External Inductor Connection and Source Connection for the High-Side MOSFET for Output 2. Also serves as the return terminal for the high-side MOSFET driver.                                                                                                                               |

| 26  | DH2             | High-Side Gate Driver Output 2. DH2 drives the gate of the high-side MOSFET.                                                                                                                                                                                                                |

| 27  | BST2            | Boost Flying-Capacitor Connection. Reservoir capacitor connection for the high-side MOSFET driver supply. Connect a 0.47µF ceramic capacitor between BST2 and LX2.                                                                                                                          |

| 28  | EN2             | Output 2 Enable. A logic-low shuts down channel 2's MOSFET drivers. EN2 can be used for output sequencing.                                                                                                                                                                                  |

| _   | EP              | Exposed Pad. Connect exposed pad to ground plane (MAX15034BAUI only).                                                                                                                                                                                                                       |

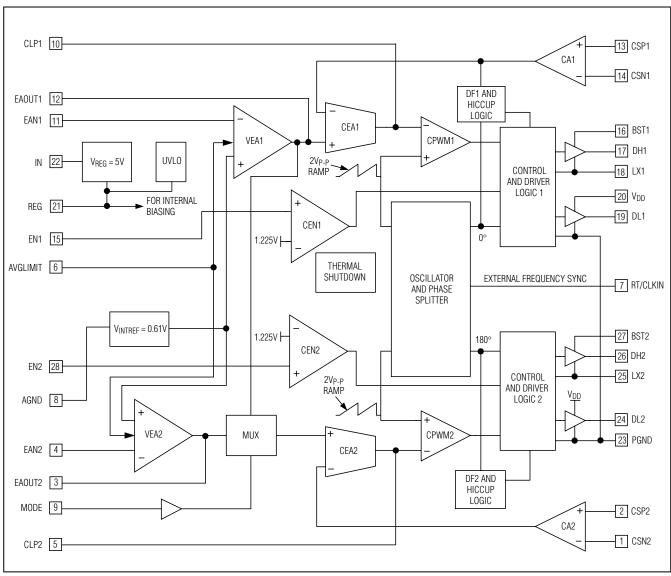

## **Detailed Description**

The MAX15034 switching power-supply controller can be configured two ways. With the MODE input high, this device operates as single-output, dual-phase, step-down switching regulators where each output is 180° out of phase. With MODE connected low, the MAX15034 operates as a dual-output, step-down switching regulator. The average current-mode control topology of the MAX15034 offers high-noise immunity while having benefits similar to those of peak current-mode control. Average current-mode control has the intrinsic ability to accurately limit the average current sourced by the converter during a fault condition. When a fault condition occurs, the error-amplifier output voltage (EAOUT1 or EAOUT2) that connects to the positive

input of the transconductance amplifier (CA1 or CA2) is clamped, thus limiting the output current.

The MAX15034 has internal logic to ensure each output's monotonic startup under prebias load conditions. This facilitates glitch-free output voltage power-up in the presence of another redundant/parallel voltage regulator.

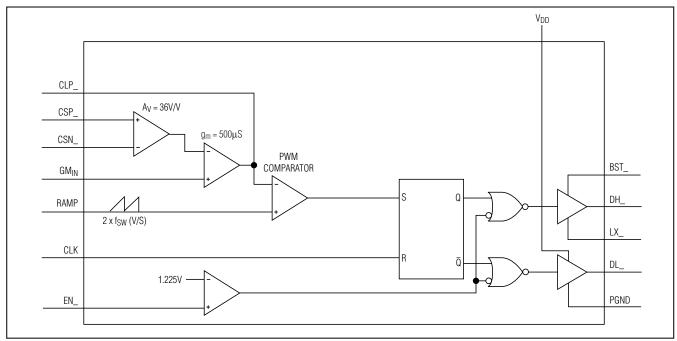

The MAX15034 contains all blocks necessary for two independently regulated average current-mode PWM regulators. This device has two voltage error amplifiers (VEA1 and VEA2), two current-error amplifiers (CEA1 and CEA2), two current-sensing amplifiers (CA1 and CA2), two PWM comparators (CPWM1 and CPWM2), and drivers for both low- and high-side power MOSFETs (see Figure 1). Each PWM section is also equipped with a pulse-by-pulse, current-limit protection and a fault integration block for hiccup protection.

10 \_\_\_\_\_\_ **///XI///**

Figure 1. Block Diagram

Two enable comparators (CEN1 and CEN2) are available to control and sequence the two PWM sections through the enable (EN1 or EN2) inputs. An oscillator, with an externally programmable frequency generates two clock pulse trains and two ramps for both PWM sections. The two clocks and the two ramps are 180° out of phase with each other.

A linear regulator (REG) generates the 5V to supply the device. This regulator has the output-current capability necessary to provide for the MAX15034's internal

circuitry and the power for the external MOSFET's gate drivers. Internal UVLO circuitry ensures that the MAX15034 starts up when V<sub>REG</sub> is at the correct voltage levels to guarantee safe operation of the IC and of the power MOSFETs.

Finally, a thermal-shutdown feature protects the device during thermal faults and shuts down the MAX15034 when the die temperature exceeds +160°C.

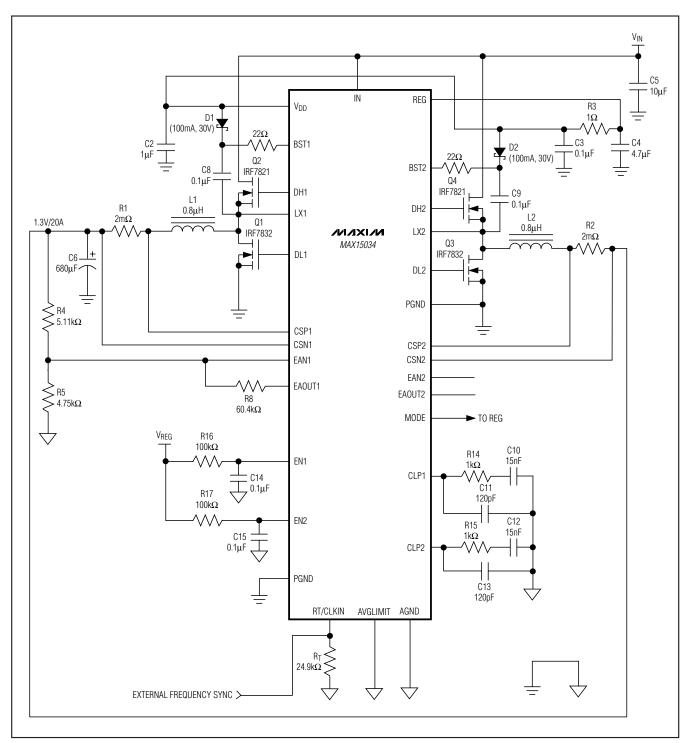

#### Dual-Output/Dual-Phase Select (MODE)

The MAX15034 can operate as a dual-output, independently regulated buck converter, or as a dual-phase, single-output buck converter. The MODE input selects between the two operating modes. When MODE is grounded (logic-low), VEA1 and VEA2 connect to CEA1 and CEA2, respectively (see Figure 1), and the device operates as a two-output DC-DC converter. When MODE is connected to REG (logic-high), VEA2 is disconnected and VEA1 is routed to both CEA1 and CEA2 and the device works as a dual-phase, single-output buck regulator with each output 180° out of phase with respect to each other.

#### Supply Voltage Connections (VIN/VREG)

The MAX15034 accepts a wide input voltage range at IN of 5V to 28V. An internal linear regulator steps down V<sub>IN</sub> to 5.1V (typ) and provides power to the MAX15034. The output of this regulator is available at REG. For V<sub>IN</sub> = 4.75V to 5.5V, connect IN and REG together externally. REG can supply up to 65mA for external loads. Bypass REG to AGND with a 4.7µF ceramic capacitor for high-frequency noise rejection and stable operation.

REG supplies the current for the MAX15034's internal circuitry and for the MOSFET gate drivers (when connected externally to V<sub>DD</sub>), and can source up to 65mA. Calculate the maximum bias current (I<sub>BIAS</sub>) for the MAX15034:

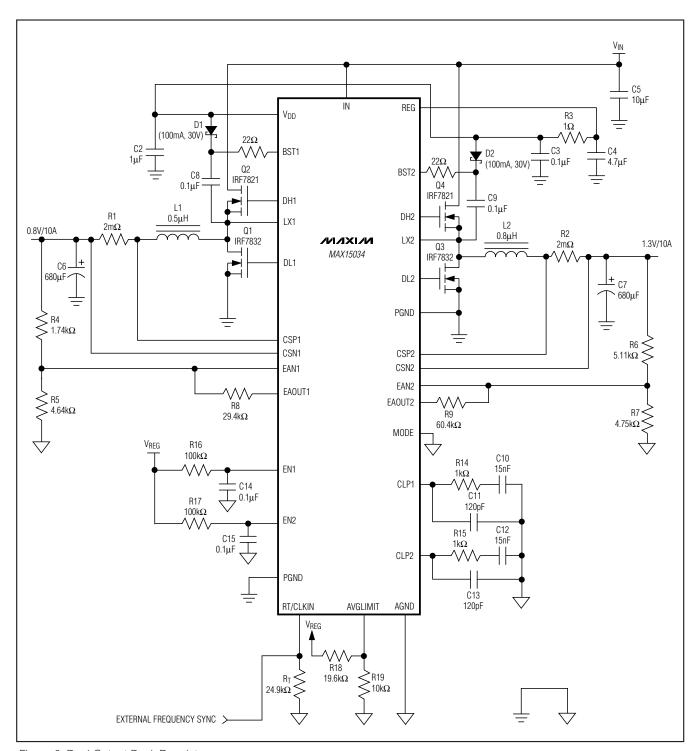

$$I_{BIAS} = I_{IN} + f_{SW} \times (Q_{GQ1} + Q_{GQ2} + Q_{GQ3} + Q_{GQ4})$$

where I<sub>IN</sub> is the quiescent supply current into IN (4mA, typ),  $Q_{GQ1}$ ,  $Q_{GQ2}$ ,  $Q_{GQ3}$ ,  $Q_{GQ4}$  are the total gate charges of MOSFETs Q1 through Q4 at V<sub>GS</sub> = 5V (see Figure 6), and f<sub>SW</sub> is the switching frequency of each individual phase.

#### Low-Side MOSFET Driver Supply (VDD)

VDD is the power input for the low-side MOSFET drivers. Connect the regulator output REG externally to VDD through an R-C lowpass filter. Use a  $1\Omega$  resistor and a parallel combination of  $1\mu F$  and  $0.1\mu F$  ceramic capacitors to filter out the high peak currents of the MOSFET drivers from the sensitive internal circuitry.

#### **High-Side MOSFET Drive Supply (BST\_)**

BST1 and BST2 supply the power for the high-side MOSFET drivers for output 1 and output 2, respectively. Connect BST1 and BST2 to  $V_{DD}$  through rectifier diodes D1 and D2 (see Figure 6). Connect a  $0.1\mu F$  ceramic capacitor between BST and LX .

Minimize the trace inductance from BST\_ and  $V_{DD}$  to the rectifier diodes, D1 and D2, and from BST\_ and LX\_ to the boost capacitors, C8 and C9 (see Figure 6). This is accomplished by using short, wide trace lengths.

#### Undervoltage Lockout (UVLO)/ Power-On Reset (POR)/Soft-Start

The MAX15034 includes an undervoltage lockout (UVLO) with hysteresis, and a power-on reset circuit for converter turn-on and monotonic rise of the output voltage. The UVLO threshold monitors VREG and is internally set between 4.0V and 4.5V with 200mV of hysteresis. Hysteresis eliminates chattering during startup. Most of the internal circuitry, including the oscillator, turns on when VREG reaches 4.5V. The MAX15034 draws up to 4mA (typ) of current before VREG reaches the UVLO threshold.

The compensation network at the current-error amplifiers (CLP1 and CLP2) provides an inherent soft-start of the output voltage. It includes (R14 and C10) in parallel with C11 at CLP1 and (R15 and C12) in parallel with C13 at CLP2 (see Figure 6). The voltage at the current-error amplifier output limits the maximum current available to charge the output capacitors. The capacitor at CLP\_ in conjunction with the finite output-drive current of the current-error amplifier yields a finite rise time for the output current and thus, the output voltage.

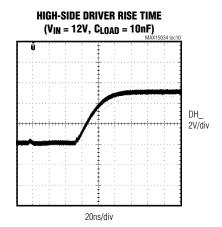

#### **Setting the Switching Frequency (fsw)**

An internal oscillator generates the 180° out-of-phase clock signals required for both PWM modulators. The oscillator also generates the 2VP-P voltage ramps necessary for the PWM comparators. The oscillator frequency can be set from 200kHz to 2MHz by an external resistor (RT) connected from RT/CLKIN to AGND (see Figure 6). The equation below shows the relationship between RT and the switching frequency:

$$f_{OSC} = \frac{2.5 \times 10^{10}}{R_{BT}} Hz$$

where  $R_{RT}$  is in ohms and the per-phase switching frequency is  $f_{SW} = f_{OSC}/2$ .

Use RT/CLKIN as a clock input to synchronize the MAX15034 to an external frequency (fRT/CLKIN). Applying an external clock to RT/CLKIN allows each PWM section to work at a frequency equal to fRT/CLKIN/2. An internal comparator with a 1.6V threshold detects fRT/CLKIN. If fRT/CLKIN is present, internal logic switches from the internal oscillator clock, to the clock present at RT/CLKIN.

12 \_\_\_\_\_\_ /I/XI/VI

#### **Hiccup Fault Protection**

The MAX15034 includes overload fault protection circuitry that prevents damage to the power MOSFETs. The fault protection consists of two digital fault integration blocks that enable hiccuping under overcurrent conditions. This circuit works as follows: for every clock cycle the currentlimit threshold is exceeded, the fault integration counter increments by one count. Thus, if the current-limit condition persists, the counter reaches its shutdown threshold in 32,768 counts and shuts down the external MOSFETs. When the MAX15034 shuts down due to a fault, the counter begins to count down (since the current-limit condition has ended), once every 16 clock cycles. Thus, the device counts down for 524,288 clock cycles. At this point, switching resumes. This produces an effective duty cycle of 6.25% power-up and 93.75% power-down under fault conditions. With a switching frequency set to 250kHz, power-up and power-down times are approximately 131ms and 2.09s, respectively.

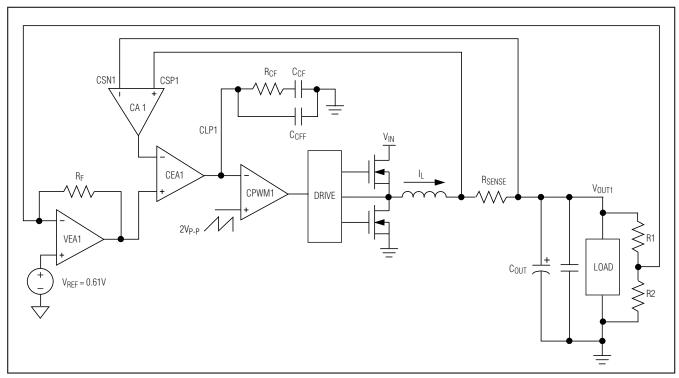

#### **Control Loop**

The MAX15034 uses an average current-mode control topology to regulate the output voltage. The control loop consists of an inner current loop and an outer voltage loop. The inner current loop controls the output

current, while the outer voltage loop controls the output voltage. The inner current loop absorbs the inductor pole, reducing the order of the outer voltage loop to that of a single-pole system. Figure 2 is the block diagram of OUT1's control loop.

The current loop consists of a current-sense resistor, RSENSE, a current-sense amplifier (CA1), a currenterror amplifier (CEA1), an oscillator providing the carrier ramp, and a PWM comparator (CPWM1). The precision current-sense amplifier (CA1) amplifies the sense voltage across RSFNSF by a factor of 36. The inverting input to CEA1 senses the output of CA1. The output of CEA1 is the difference between the voltageerror amplifier output (EAOUT1) and the gained-up voltage from CA1. The RC compensation network connected to CLP1 provides external frequency compensation for the respective CEA1 (see the Compensation section). The start of every clock cycle enables the high-side driver and initiates a PWM oncycle. Comparator CPWM1 compares the output voltage from CEA1 against a 0 to 2V ramp from the oscillator. The PWM on-cycle terminates when the ramp voltage exceeds the error voltage from the current-error amplifier (CEA1).

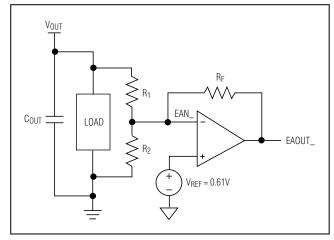

Figure 2. Current and Voltage Loops

The outer voltage control loop consists of the voltage-error amplifier (VEA1). The noninverting input (EAN1) is externally connected to the midpoint of a resistive voltage-divider from OUT1 to EAN1 to AGND. The voltage loop gain is set by using an external resistor from the output of this amplifier (EAOUT1) to its inverting input (EAN1). The noninverting input of (VEA1) is connected to the 0.61V internal reference.

#### **Current-Error Amplifier**

The MAX15034 features two dedicated transconductance current-error amplifiers CEA1 and CEA2 with a typical  $g_m$  of  $550\mu S$  and  $320\mu A$  output sink and source capability. The current-error amplifier outputs (CLP1 and CLP2) serve as the inverting input to the PWM comparators. CLP1 and CLP2 are externally accessible to provide frequency compensation for the inner current loops (see CCFF, CCF, and RCF in Figure 2). Compensate the current-error amplifier so that the inductor current down slope, which becomes the up slope at the inverting input of the PWM comparator, is less than the slope of the internally generated voltage ramp (see the Compensation section).

#### **PWM Comparator and R-S Flip-Flop**

The PWM comparator (CPWM1 or CPWM2) sets the duty cycle for each cycle by comparing the current-error amplifier output to a 2V<sub>P-P</sub> ramp. At the start of each clock cycle an R-S flip-flop resets and the high-side drivers (DH1 and DH2) turn on. The comparator sets the flip-flop as soon as the ramp voltage exceeds the current-error amplifier output voltage, thus terminating the on-cycle.

#### **Voltage-Error Amplifier**

The voltage-error amplifier (VEA\_) sets the gain of the voltage control loop. Its output clamps to 1.14V and -0.234V relative to  $V_{CM} = 0.61V$ . Set the MAX15034 output voltage by connecting a voltage-divider from the output to EAN\_ to GND (see Figure 4). At no load, the output of the voltage error amplifier is zero.

Use the equation below to calculate the no load voltage:

$$V_{OUT(NL)} = 0.6125 \times \left(1 + \frac{R_1}{R_2}\right)$$

The voltage at full load is given by:

$$V_{OUT(FL)} = 0.6125 \times \left(1 + \frac{R_1}{R_2}\right) - \Delta V_{OUT}$$

where  $\Delta V_{OUT}$  is the voltage-positioning window described in the *Adaptive Voltage Positioning* section.

#### **Adaptive Voltage Positioning**

Powering new-generation ICs requires new techniques to reduce cost, size, and power dissipation. Voltage positioning (Figure 5) reduces the total number of output capacitors to meet a given transient response requirement. Setting the no-load output voltage slightly higher than the output voltage during nominally loaded conditions allows a larger downward voltage excursion when the output current suddenly increases. Regulating at a lower output voltage under a heavy load allows a larger upward-voltage excursion when the output current suddenly decreases. A larger allowed voltage-step excursion reduces the required number of output capacitors and/or allows the use of higher ESR capacitors.

The MAX15034 internal 0.6125V reference provides a tolerance of  $\pm 1.25\%$ . Using 0.1% resistors for R1 and R2 allows a 4% variation from the nominal output voltage. This available voltage range allows the reduction of the total number of output capacitors to meet a given transient response requirement resulting in a voltage-positioning window as shown in Figure 5.

From the allowable voltage-positioning window calculate the value of R<sub>F</sub> from the equation below.

$$R_F = \frac{I_{OUT} \times R_{SENSE} \times 36 \times R_1}{\Delta V_{OUT}}$$

where  $\Delta V_{OUT}$  is the allowable voltage-positioning window, RSENSE is the sense resistor, 36 is the current-sense amplifier gain, and R<sub>1</sub> is as shown in Figure 4.

Figure 3. Current Comparator and MOSFET Driver Logic

Figure 4. Voltage Error Amplifier

# V<sub>CNTR</sub> + ΔV<sub>OUT</sub>/2 V<sub>CNTR</sub> - ΔV<sub>OUT</sub>/2 V<sub>CNTR</sub> - ΔV<sub>OUT</sub>/2 NO LOAD 1/2 LOAD LOAD (A)

Figure 5. Defining the Voltage-Positioning Window

#### **MOSFET Gate Drivers (DH\_, DL\_)**

The high-side drivers (DH1 and DH2) and low-side drivers (DL1 and DL2) drive the gates of external n-channel MOSFETs. The high-peak sink and source current capability of these drivers provides ample drive for the fast rise and fall times of the switching MOSFETs. Faster rise and fall times result in reduced switching losses. For low-output, voltage-regulating applications where the duty

cycle is less than 50%, choose high-side MOSFETs (Q2 and Q4, Figure 6) with a moderate RDS(ON) and a very low gate charge. Choose low-side MOSFETs (Q1 and Q3, Figure 6) with very low RDS(ON) and moderate gate charge. The driver block also includes a logic circuit that provides an adaptive nonoverlap time (30ns typ) to prevent shoot-through currents during transition. Figure 7 shows the dual-phase, single-output buck regulator.

Figure 6. Dual-Output Buck Regulator

Figure 7. Dual-Phase, Single-Output Buck Regulator

## **Design Procedures**

#### **Inductor Selection**

The switching frequency per phase, peak-to-peak ripple current in each phase, and allowable voltage ripple at the output, determine the inductance value. Selecting higher switching frequencies reduces the inductance requirement, but at the cost of lower efficiency due to the charge/discharge cycle of the gate and drain capacitances in the switching MOSFETs. The situation worsens at higher input voltages, since capacitive switching losses are proportional to the square of the input voltage. Lower switching frequencies on the other hand increase the peak-to-peak inductor ripple current ( $\Delta I_L$ ), and therefore, increase the MOSFET conduction losses (see the *Power MOSFET Selection* section for a detailed description of MOSFET power loss).

When using higher inductor ripple current, the ripple cancellation in the multiphase topology, reduces the input and output capacitor RMS ripple current. Use the following equation to determine the minimum inductance value:

$$L = \frac{V_{OUT}(V_{IN(MAX)} - V_{OUT})}{V_{IN} \times f_{SW} \times \Delta I_L}$$

Choose  $\Delta I_{\perp}$  to be equal to approximately 30% of the output current per channel. Since  $\Delta I_{\perp}$  affects the output-ripple voltage, the inductance value may need minor adjustment after choosing the output capacitors for fullrated efficiency. Choose inductors from the standard high-current, surface-mount inductor series available from various manufacturers. Particular applications may require custom-made inductors. Use high-frequency core material for custom inductors. High ΔI<sub>1</sub> causes large peak-to-peak flux excursion increasing the core losses at higher frequencies. The high-frequency operation coupled with high  $\Delta I_L$ , reduces the required minimum inductance and even makes the use of planar inductors possible. The advantages of using planar magnetics include low-profile design, excellent current sharing between phases due to the tight control of parasitics, and low cost. For example, the minimum inductance at VIN = 12V,  $V_{OUT} = 0.8V$ ,  $\Delta I_{L} = 3A$ , and  $f_{SW} = 500$ kHz is  $0.5\mu$ H.

The average current-mode control feature of the MAX15034 limits the maximum inductor current, which prevents the inductor from saturating. Choose an inductor with a saturating current greater than the worst-case peak inductor current:

$$I_{L\_PEAK} = \frac{24.75 \times 10^{-3}}{R_{SENSE}} + \frac{\Delta I_L}{2}$$

where 24.75mV is the maximum average current-limit threshold for the current-sense amplifier and RSENSE is the sense resistor.

#### **Power MOSFET Selection**

When choosing the MOSFETs, consider the total gate charge, RDS(ON), power dissipation, the maximum drain-to-source voltage, and package thermal impedance. The product of the MOSFET gate charge and onresistance is a figure of merit, with a lower number signifying better performance. Choose MOSFETs optimized for high-frequency switching applications. The average gate-drive current from the MAX15034's output is proportional to the total capacitance it drives at DH1, DH2, DL1, and DL2. The power dissipated in the MAX15034 is proportional to the input voltage and the average drive current. See the Supply Voltage Connections (VIN/VREG) and the Low-Side MOSFET Drives Supply (VDD) sections to determine the maximum total gate charge allowed from all driver outputs together.

The losses may be broken into four categories: conduction loss, gate drive loss, switching loss, and output loss. The following simplified power loss equation is true for both MOSFETs in the synchronous buck-converter:

For the low-side MOSFET, the P<sub>SWITCH</sub> term becomes virtually zero because the body diode of the MOSFET is conducting before the MOSFET is turned on.

Tables 1 and 2 describe the different losses and shows an approximation of the losses during that period.

#### **Input Capacitance**

The discontinuous input-current waveform of the buck converter causes large ripple currents in the input capacitor. The switching frequency, peak inductor current, and the allowable peak-to-peak voltage ripple reflected back to the source, dictate the capacitance requirement. Increasing the number of phases increases the effective switching frequency and lowers the peak-to-average current ratio, yielding lower input capacitance requirement. It can be shown that the worst-case RMS current occurs when only one controller section is operating. The controller section with the highest output power needs to be used in determining the maximum input RMS ripple current requirement. Increasing the output current drawn from the other out-of-phase controller section results in reducing the input

Table 1. High-Side MOSFET Losses

| LOSS            | DESCRIPTION                                                                                                                                                                                                                                                                        | SEGMENT LOSS                                                                                                            |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Conduction Loss | Losses associated with MOSFET on-time and on-resistance. IRMS is a function of load current and duty cycle.                                                                                                                                                                        | $P_{CONDUCTION} = I_{RMS} 2 \times R_{DS(ON)}$<br>where $I_{RMS} \approx \sqrt{\frac{V_{OUT}}{V_{IN}}} \times I_{LOAD}$ |

| Gate Drive Loss | Losses associated with charging and discharging the gate capacitance of the MOSFET every cycle. Use the MOSFET's (QG) specification.                                                                                                                                               | $P_{GATEDRIVE} = V_{DD} \times (Q_{G} - Q_{GD}) \times f_{SW}$                                                          |

| Switching Loss  | Losses during the drain voltage and drain current transitions for every switching cycle. Losses occur only during the QGS2 and QGD time period and not during the initial QGS1 period. The initial QGS1 period is the rise in the                                                  | $P_{SWITCH} = V_{IN} \times I_{LOAD} \times f_{SW} \times \frac{(Q_{GS2} + Q_{GD})}{I_{GATE}}$                          |

| Switching Loss  | gate voltage from zero to V <sub>TH</sub> . R <sub>DH</sub> _ is the high-<br>side MOSFET driver's on-resistance and R <sub>GATE</sub><br>is the internal gate resistance of the high-side<br>MOSFET (Q <sub>GD</sub> and Q <sub>GS2</sub> are found in the<br>MOSFET data sheet). | where $I_{GATE} = \frac{V_{DD}}{2 \times (R_{DH} + R_{GATE})}$                                                          |

| Output Loss     | Losses associated with QOSS of the MOSFET occur every cycle when the high-side MOSFET turns on. The losses are caused by both MOSFETs, but are dissipated in the high-side MOSFET.                                                                                                 | $P_{OUTPUT} = \frac{Q_{OSS(HS)} + Q_{OSS(LS)}}{2} \times V_{IN} \times f_{SW}$                                          |

ripple current. A low-ESR input capacitor that can handle the maximum input RMS ripple current of one channel must be used. The maximum RMS capacitor ripple current is given by:

$$I_{CIN(RMS)} \approx I_{MAX} \, \frac{\sqrt{V_{OUT}(V_{IN} - V_{OUT})}}{V_{IN}}$$

where  $I_{MAX}$  is the full load current of the regulator.  $V_{OUT}$  is the output voltage of the same regulator and  $C_{IN}$  is C5 in Figure 6. The ESR of the input capacitors wastes power from the input and heats up the capacitor. Reducing the ESR is important to maintain a high overall efficiency and in reducing the heating of the capacitors.

#### **Output Capacitors**

The worst-case peak-to-peak inductor ripple current, the allowable peak-to-peak output ripple voltage, and the maximum deviation of the output voltage during step loads determine the capacitance and the ESR requirements for the output capacitors. The output ripple can be approximated as the inductor current ripple multiplied by the output capacitor's ESR (Resr\_out). The peak-to-peak inductor current ripple is given by:

$$\Delta I_{L} = \frac{V_{OUT}(1-D)}{L \times f_{SW}}$$

During a load step, the allowable deviation of the output voltage during the fast transient load dictates the output capacitance and ESR. The output capacitors supply the load step until the controller responds with a greater duty cycle. The response time (tresponse) depends on the closed-loop bandwidth of the regulator. The resistive drop across the capacitor's ESR and capacitor discharge causes a voltage drop during a load step. Use a combination of SP polymer and ceramic capacitors for better transient load and ripple/noise performance.

Table 2. Low-Side MOSFET Losses

| LOSS            | DESCRIPTION                                                                                                                                                                                              | SEGMENT LOSSES                                                                                                                |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Conduction Loss | Losses associated with MOSFET on-time, I <sub>RMS</sub> is a function of load current and duty cycle.                                                                                                    | $P_{CONDUCTION} = I_{RMS} 2 \times R_{DS(ON)}$ where $I_{RMS} \approx \sqrt{\frac{V_{IN} - V_{OUT}}{V_{IN}}} \times I_{LOAD}$ |

| Gate Drive Loss | Losses associated with charging and discharging the gate of the MOSFET every cycle. There is no QGD charging involved in this MOSFET due to the zero-voltage turn-on. The charge involved is (QG - QGD). | $P_{GATEDRIVE} = V_{DD} \times (Q_{G} - Q_{GD}) \times f_{SW}$                                                                |

**Note:** The gate drive losses are distributed between the drivers and the MOSFETs in the ratio of the gate driver's resistance and the MOSFET's internal gate resistance.

Keep the maximum output-voltage deviation less than or equal to the adaptive voltage-positioning window ( $\Delta V_{OUT}$ ). During a load step, assume a 50% contribution each from the output capacitance discharge and the voltage drop across the ESR ( $\Delta V_{OUT} = \Delta V_{ESR_OUT} + \Delta V_{Q_OUT}$ ). Use the following equations to calculate the required ESR and capacitance value:

$$\begin{split} R_{ESR\_OUT} &= \frac{\Delta V_{ESR\_OUT}}{I_{LOAD\_STEP}} \\ C_{OUT} &= \frac{I_{LOAD\_STEP} \times I_{RESPONSE}}{\Delta V_{Q\_OUT}} \end{split}$$

where I<sub>LOAD\_STEP</sub> is the step in load current and tresponse is the response time of the controller. Controller response time depends on the control-loop bandwidth. Cout is C6 and C7 in Figure 6.

#### **Current Limit**

The MAX15034 incorporates two forward current-limit protection mechanisms, average current limit and hiccup fault current limit, which accurately limit the output current per phase. The average current-mode control technique of the MAX15034 accurately limits the maximum average output current per phase. The MAX15034 senses the voltage across either a sense resistor or can implement lossless inductor sense, sensing the voltage across the parasitic resistance of the inductor (DCR). Use either mechanism to limit the maximum inductor current.

The minimum average voltage, at which the voltage across the current-sense resistor is clamped, is either internally set to 20.4mV or is controlled by the voltage at AVGLIMIT. The AVGLIMIT ground threshold of 550mV (typ) is the threshold above which the control of the average current-limit voltage is transferred from the internal 20.4mV (min) reference to the externally set VAVGLIMIT. For using the internal average current-limit value, short AVGLIMIT to AGND. The minimum (internally set) average current limit is set at:

$$I_{LIMIT(MIN)} = \frac{20.4mV}{R_{SENSE}}$$

For example, the current-sense resistor:

$$R_{SENSE} = \frac{20.4mV}{10A} = 2.04m\Omega$$

for a maximum output current limit of 10A. A standard value is  $2m\Omega$ . Also, adjust the value of the current-sense resistor to compensate for parasitics associated with the PCB. Select a noninductive resistor with an appropriate wattage rating.

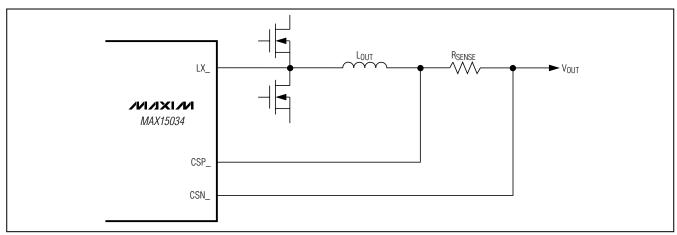

The implementation is shown in Figure 8.

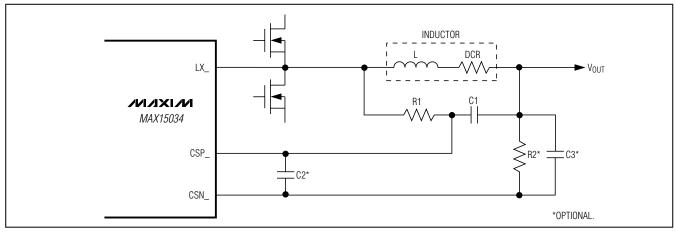

When sensing directly across the inductor, connect an RC circuit directly across the shunt or inductor (see Figure 9).

20 \_\_\_\_\_\_\_\_/N/XI/VI

Figure 8. Noninductive Resistive Sense

Figure 9. Lossless Inductor Sense

Set the RC time constant to be 1.1 to 1.2 times the inductor time constant (L/DCR). Select C1 to be in the  $0.1\mu\text{F}$  to  $0.47\mu\text{F}$  range, and then calculate R1 from:

$$R1[k\Omega] = \frac{1.2 \times L[\mu H]}{DCR[m\Omega] \times C1[\mu F]}$$

In some applications, it may be useful to add a resistor (R2 in Figure 9) in series with the CSN\_ connection to minimize input offset error. Set R2 equal to R1. It may also prove useful to add capacitor C3 (Figure 9) in

parallel with R2 to aid in short-circuit recovery. Set C3 equal to C1. Finally, it may be helpful to add a 100pF (C2) capacitor immediately across the CSP\_ and CSN\_ inputs to minimize high-frequency noise pick-up at the IC in some applications.

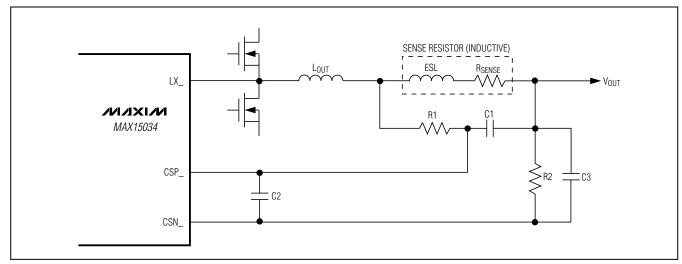

For current-sense resistors that have a noticeable inductance component, use lossless inductor sense implementation (and design procedure). See Figure 10. Table 3 highlights the tradeoffs of each current-sense

**Table 3. Current-Sense Configurations**

| METHOD                            | CURRENT-SENSE<br>ACCURACY | INDUCTOR-SATURATION PROTECTION | CURRENT-SENSE POWER LOSS (EFFICIENCY)              |

|-----------------------------------|---------------------------|--------------------------------|----------------------------------------------------|

| Output Current-Sense Resistor     | High                      | Allowed (highest accuracy)     | R <sub>SENSE</sub> x I <sub>OUT</sub> <sup>2</sup> |

| Equivalent Inductor DC Resistance | Low                       | Allowed                        | No additional loss                                 |

method.

Figure 10. Inductive Sense Resistor

The MAX15034 provides precision average current-limit programmability while using standard sense resistors or shunts. Use the equation below to determine the appropriate VAVGLIMIT external reference voltage at AVGLIMIT:

$$V_{AVGLIMIT} = (56 \times R_{SENSE}[m\Omega] \times I_{LOAD(MAX)}[A]) + 612.5mV$$

For example, assuming the desired average current limit is 18A, and RSENSE =  $2m\Omega$ .

$$V_{AVGLIMIT} = (2m\Omega \times 36 \times 18A) + 612.5mV$$

= 1910mV = 1.91V

where RSENSE is determined from maximum load current, wattage rating, and circuit parasitics (see above) and ILOAD(MAX) from circuit requirements. VAVGLIMIT is the average current-limit reference voltage selected for a desired ILOAD(MAX) and is set by a resistive voltage-divider from REG to AGND. See the *Programming the Average Current Limit* section.

The second current-protection circuit is the hiccup fault protection as explained in the *Hiccup Fault Protection* section. The average current during a short at the output is given by:

$$I_{AVG(SHORT)} = 0.0625 \times I_{LOAD(MAX)}$$

#### **Programming the Average Current Limit**

The MAX15034 average current-limit reference voltage is set by connecting a resistor-divider network from REG to AGND, the center node is connected to AVGLIMIT. The resistive divider's upper resistor, R1, is connected between REG and the AVGLIMIT. The resistive divider's lower resistor, R2, is connected between the AVGLIMIT and AGND.

The resistor-divider values are determined by first, choosing R2. To minimize reference noise select R2 such that (R1 + R2) <  $100k\Omega$ ; a typical value is  $10k\Omega$ . Next. determine R1 from:

R1 = R2 ×

$$\left(\frac{V_{REG}}{V_{AVGLIMIT}} - 1\right)$$

= 10k $\Omega$  ×  $\left(\frac{5V}{V_{AVGLIMT(MAX)}[V]} - 1\right)$

From the example above, assuming VAVGLIMIT = 1.91V:

$$R1 = 10k\Omega \times \left(\frac{5V}{1.91V} - 1\right) = 16.18k\Omega$$

A standard value for R1 is 16.2k $\Omega$ . Connect AVGLIMIT to AGND for default current limit  $\left(\frac{20.4\text{mV}}{\text{R}_{\text{SFNSF}}}\right)$ .

#### **Reverse Current Limit**

The MAX15034 limits the reverse current when the output capacitor voltage is higher than the preset output voltage. Calculate the maximum reverse current limit based on VCLMP\_LO and the current-sense resistor RSFNSF.

$$I_{REVERSE} = \frac{1.55 \times 10^{-3}}{R_{SENSE}}$$

#### **Output-Voltage Setting**

The output voltage is set by the combination of resistors R1, R2, and RF as described in the *Voltage-Error Amplifier* section. First select a value for resistor R2. Then calculate the value of R1 from the following equation:

$$R1 = \frac{(V_{OUT(NL)} - 0.6125)}{0.6125} \times R2$$

where V<sub>OUT(NL)</sub> is the voltage at no load. Then find the value of R<sub>F</sub> from the following equation:

$$R_F = \frac{I_{OUT} \times R_{SENSE} \times 36 \times R_1}{\Delta V_{OUT}}$$

where  $\Delta V_{OUT}$  is the allowable drop in voltage from no load to full load. R<sub>F</sub> is R8 and R9, R1 is R4 and R6, R2 is R5 and R7 in Figure 6.

#### Compensation

The MAX15034 uses an average current-mode control scheme to regulate the output voltage (see Figure 2). The main control loop consists of an inner current loop and an outer voltage loop. The voltage error amplifier (VEA1 and VEA2) provides the controlling voltage for the current loop in each phase. The output inductor is hidden inside the inner current loop. This simplifies the design of the outer voltage control loop and also improves the power-supply dynamics. The objective of the inner current loop is to control the average inductor current. The gain-bandwidth characteristic of the current loop can be tailored for optimum performance by the compensation network at the output of the currenterror amplifier (CEA1 or CEA2). Compared with peak current-mode control, the current-loop gain crossover frequency, fc, can be made approximately the same, but the gain at low frequencies is much higher. This results in the following advantages over peak currentmode control.

- The average current tracks the programmed current with a high degree of accuracy.

- 2) Slope compensation is not required, but there is a limit to the loop gain at the switching frequency to achieve stability.

- 3) Noise immunity is excellent.

- 4) The average current-mode method can be used to sense and control the current in any circuit branch.

For stability of the current loop, the amplified inductor-current downslope at the negative input of the PWM comparator (CPWM1 and CPWM2) must not exceed the ramp slope at the comparator's positive input. This puts an upper limit on the current-error amplifier gain at the switching frequency. The inductor current downslope is given by VOUT/L where L is the value of the inductor (L1 and L2 in Figure 6) and VOUT is the output voltage. The amplified inductor current downslope at the negative input of the PWM comparator is given by:

$$\frac{\Delta V_L}{\Delta t} = \frac{V_{OUT}}{L} \times R_{SENSE} \times 36 \times g_m \times R_{CF}$$

where RSENSE is the current-sense resistor (R1 and R2 in Figure 6) and gM x RCF is the gain of the current-error amplifier (CEA\_) at the switching frequency. The slope of the ramp at the positive input of the PWM comparator is 2V x fsw. Use the following equation to calculate the maximum value of RCF (R14 or R15 in Figure 6).

$$R_{CF} \le \frac{2 \times f_{SW} \times L}{V_{OUT} \times R_{SENSE} \times 36 \times g_m}$$

(1)

The highest crossover frequency fcmax is given by:

$$f_{CMAX} = \frac{f_{SW} \times V_{IN}}{2\pi \times V_{OUT}}$$

or alternatively:

$$f_{SW} = \frac{f_{CMAX} \times 2\pi \times V_{OUT}}{V_{IN}}$$

Equation (1) can now be rewritten as:

$$R_{CF} = \frac{\pi \times f_C \times L}{V_{IN} \times R_S \times 9 \times g_m}$$

(2)

In practical applications, pick the crossover frequency (fc) in the range of:

$$\frac{f_{SW}}{10} < f_C < \frac{f_{SW}}{2}$$

First calculate R<sub>CF</sub> in equation 2 above. Calculate C<sub>CF</sub> so that:

$$C_{CF} = \frac{10}{2 \times \pi \times f_C \times R_{CF}}$$

where C<sub>CF</sub> is C10 and C12 in Figure 6.

Calculate CCFF so that:

$$C_{CFF} = \frac{1}{2 \times \pi \times f_C \times 10 \times R_{CF}}$$

where CCFF is C11 and C13 in Figure 6.

## Applications Information

#### **Independent Turn-On and Turn-Off**

The MAX15034 can be used to regulate two outputs from one controller. Each of the two outputs can be turned on and off independently of one another by controlling the enable input of each phase (EN1 and EN2). A logic-low on each enable pin shuts down the MOSFET drivers for that phase. When the voltage on the enable pin exceeds 1.2V, the drivers are turned on and the output can come up to regulation. This method of turning on the outputs allows the MAX15034 to be used for power sequencing.

#### **PCB Layout Guidelines**

Careful PCB layout is critical to achieve low losses, low output noise, and clean and stable operation. This is

especially true for dual-phase converters where one channel can affect the other. Use the following guidelines for PCB layout:

- 1) Place the  $V_{DD}$ , REG, and the BST1 and BST2 bypass capacitors close to the MAX15034.

- 2) Minimize all high-current switching loops.

- Keep the power traces and load connections short.

This practice is essential for high efficiency. Use thick copper PCBs (2oz or higher) to enhance efficiency and minimize trace inductance and resistance.

- 4) Run the current-sense lines CSP\_ and CSN\_ very close to each other to minimize loop areas. Do not cross these critical signal lines through power circuitry. Sense the current right at the pads of the current-sense resistors.

- 5) Place the bank of output capacitors close to the load.

- 6) Isolate the power components on the top side from the analog components on the bottom side with a ground plane in between.

- 7) Provide enough copper area around the switching MOSFETs, inductors, and sense resistors to aid in thermal dissipation and reducing resistance.

- 8) Distribute the power components evenly across the top side for proper heat dissipation.

- Keep AGND and PGND isolated and connect them at one single point close to the IC. Do not connect them together anywhere else.

- 10) Place all input bypass capacitors for each input as close to each other as is practical.

## **Pin Configuration**

**Chip Information**

PROCESS: BiCMOS

## Package Information

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE<br>NO. | LAND<br>PATTERN NO. |

|-----------------|-----------------|----------------|---------------------|

| 28 TSSOP        | U28+2           | <u>21-0066</u> | <u>90-0171</u>      |

| 28 TSSOP-EP     | U28E+4          | <u>21-0108</u> | 90-0146             |

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                   | PAGES<br>CHANGED |

|--------------------|------------------|-------------------------------|------------------|

| 0                  | 7/08             | Initial release               | _                |

| 1                  | 10/11            | Updated Ordering Information. | 1                |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

26