emulator and protopak. The Z90233/Z90234 masked ROM supports a 16/32-KB system ROM (selectable through a mask option).

The eZVision 200 family takes full advantage of the Z8 microcontroller's expanded register file space to offer greater flexibility in OSD creations that simulate bitmap graphics, icons, and animation.

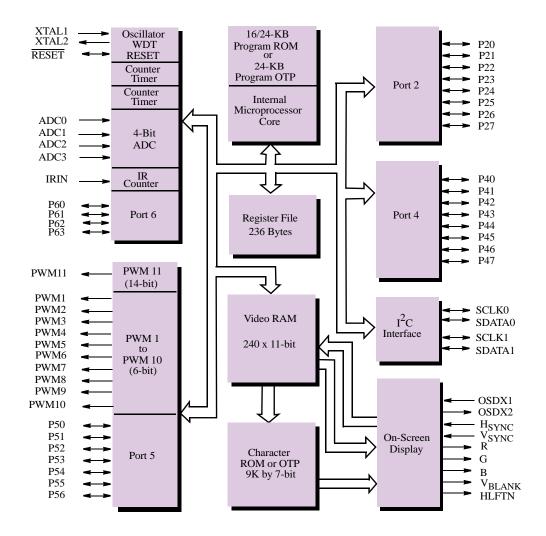

## **Block Diagram of eZVision 200**

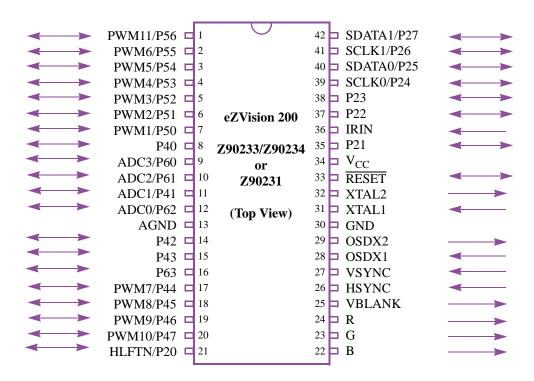

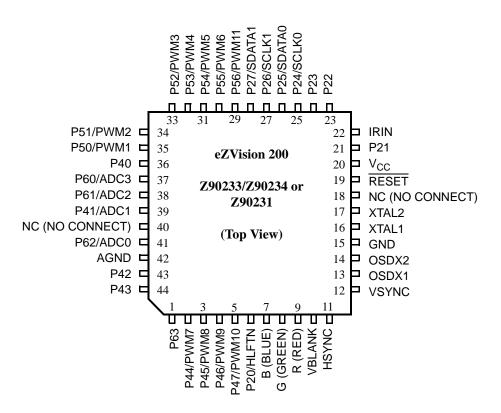

#### **Pin-Outs and Pin Direction**

Figure 1. 42-Pin Shrink DIP

Figure 2. 44-Pin Plastic Quad Flatpack (PQFP)

Table 1 Pin Descriptions for the Z90233, Z90234, and Z90231

| Name       | 42-Pin SDIP<br>Pin Number           | 44-Pin PQFP<br>Pin Number             | Function                             | Direction | Reset<br>State |

|------------|-------------------------------------|---------------------------------------|--------------------------------------|-----------|----------------|

| $V_{CC}$   | 34                                  | 20                                    | +5 Volts                             | PWR       | PWR            |

| GND, AGND  | 30, 13                              | 15, 42                                | 0 Volts                              | PWR       | PWR            |

| IRIN       | 36                                  | 22                                    | Infrared remote capture input        | I         | I              |

| PWM11      | 1                                   | 29                                    | 14-bit pulse width modulator output* | 0         | I              |

| PWM10-PWM1 | 20, 19, 18, 17, 2, 3,<br>4, 5, 6, 7 | 5, 4, 3, 2, 30, 31,<br>32, 33, 34, 35 | 6-bit pulse width modulator output*  | 0         | I              |

Table 1 Pin Descriptions for the Z90233, Z90234, and Z90231 (Continued)

| Name      | 42-Pin SDIP<br>Pin Number         | 44-Pin PQFP<br>Pin Number        | Function                                | Direction | Reset<br>State |

|-----------|-----------------------------------|----------------------------------|-----------------------------------------|-----------|----------------|

| P56–P50   | 7, 6, 5, 4, 3, 2, 1               | 29, 30, 31, 32, 33,<br>34, 35    | Bit-programmable input/<br>output ports | I/O       | I              |

| P27–P20   | 42, 41, 40, 39, 38,<br>37, 35, 21 | 28, 27, 26, 25, 24,<br>23, 21, 6 | Bit-programmable input/<br>output ports | I/O       | 1              |

| HLFTN     | 21                                | 6                                | Half tone output                        | 0         | I              |

| SDATA0, 1 | 40, 42                            | 26, 28                           | I <sup>2</sup> C data                   | I/O       | I              |

| SCLK0, 1  | 39, 41                            | 25, 27                           | I <sup>2</sup> C clock                  | I/O       | I              |

| P63–P60   | 16, 12, 10, 9                     | 1, 41, 38, 37                    | Bit-programmable input/<br>output ports | I/O       | I              |

| P47–P40   | 20, 19, 18, 17, 15,<br>14, 11, 8  | 5, 4, 3, 2, 44, 43,<br>39, 36    | Bit-programmable input/<br>output ports | I/O       | I              |

| XTAL1     | 31                                | 16                               | Crystal oscillator input                | I         | I              |

| XTAL2     | 32                                | 17                               | Crystal oscillator output               | 0         | 0              |

| OSDX1     | 28                                | 13                               | Dot clock oscillator input              | I         | I              |

| OSDX2     | 29                                | 14                               | Dot clock oscillator output             | 0         | 0              |

| HSYNC     | 26                                | 11                               | Horizontal sync                         | I         | I              |

| VSYNC     | 27                                | 12                               | Vertical sync                           | I         | I              |

| VBLANK    | 25                                | 10                               | Video blank                             | 0         | 0              |

| R, G, B   | 24, 23, 22                        | 9, 8, 7                          | Video R, G, B                           | 0         | 0              |

| ADC3-ADC0 | 9, 10, 11, 12                     | 37, 38, 39, 41                   | 4-bit analog-to-digital converter input | AI        | I              |

| RESET     | 33                                | 19                               | Device reset                            | I/O       | I              |

**Note:** \*These pins are input on POR. They must be configured to be output ports for PWM applications.

## **Development Tools and Support**

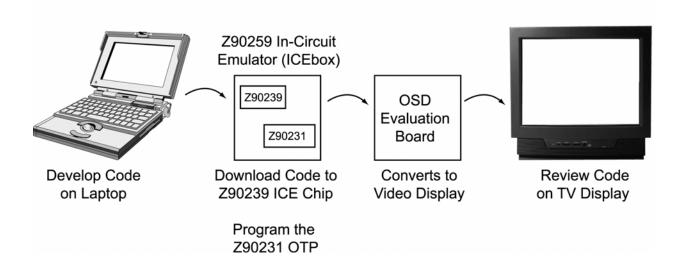

Available in OTP and masked ROM versions, the Z90231 and Z90233/Z90234 fulfill prototype and production requirements. The Z90231 uses ICEbox<sup>TM</sup> (In-Circuit Emulator) tools (Z9025900ZEM) to make programming and debugging applications easy and convenient.

The ZiLOG Developer Studio (ZDS) is a complete software program that provides easy code generation and program management.

For code development, ZiLOG offers its specialized application program interface (API) for OSD. The API deals directly with proper sequencing and timing when interfacing with hardware, shielding the user application programmer from tedious and error-prone details.

The Z8933200ZCO, an OSD evaluation board, is used to synchronize the emulator with a video display. Refer to the diagram below for a suggested code development environment.

ZiLOG also offers the Z9020900TSC Protopak to verify code on a television.

### **Related Products**

TV controllers and vertical blanking interval (VBI) decoders include the following:

| Z9037x | eZVision 300 dual-scan TV controller for progressive scan and standard interlaced scan |

|--------|----------------------------------------------------------------------------------------|

| Z9036x | eZVision 300 advanced TV controller with 32 KWords of ROM                              |

| Z86129 | eZSelect closed caption decoder (CCD)                                                  |

| Z86229 | eZSelect CCD with second I <sup>2</sup> C address select                               |

| Z86131 | eZSelect auto time set                                                                 |

| Z86130 | eZSelect smart V-chip                                                                  |

| Z86230 | eZSelect smart V-chip with second I <sup>2</sup> C address select                      |

# **Electrical Features Summary**

- 40 mA maximum supply current

- 4.50 V to 5.50 V operating range

## **eZVision 200 Device Selection**

| Device | Application            | ROM<br>(Bytes) | RAM<br>(Bytes) | Pkg                        | I <sup>2</sup> C | IR<br>Capture | ADC   | Bit I/O<br>(max) | PWM<br>(6/14-bit) |

|--------|------------------------|----------------|----------------|----------------------------|------------------|---------------|-------|------------------|-------------------|

| Z90233 | TV receiver controller | 16K            | 236            | 42-pin SDIP<br>44-pin PQFP | Yes              | Yes           | 4 Ch. | 27               | 10/2              |

| Z90234 | TV receiver controller | 24K            | 236            | 42-pin SDIP<br>44-pin PQFP | Yes              | Yes           | 4 Ch. | 27               | 10/2              |

| Z90231 | TV receiver controller | 24K<br>OTP     | 236            | 42-pin SDIP<br>44-pin PQFP | Yes              | Yes           | 4 Ch. | 27               | 10/2              |

| Z90255 | TV receiver controller | 32K            | 300            | 42-pin SDIP                | Yes              | Yes           | 4 Ch. | 27               | 10/2              |

| Z90251 | TV receiver controller | 32K<br>OTP     | 300            | 42-pin SDIP                | Yes              | Yes           | 4 Ch. | 27               | 10/2              |

|        |                        |                |                |                            |                  |               |       |                  |                   |

# **Ordering Information**

| Part                     | PSI                                  | Description                    |

|--------------------------|--------------------------------------|--------------------------------|

| Z90233                   | Z9023306PSC Rxxxx*                   | 16 KB masked ROM 42 SDIP       |

|                          | Z9023306FSC Rxxxx*                   | 16 KB masked ROM 44 PQFP       |

| Z90234                   | Z9023406PSC Rxxxx*                   | 24 KB masked ROM 42 SDIP       |

|                          | Z9023406FSC Rxxxx*                   | 24 KB masked ROM 44 PQFP       |

| Z90231                   | Z9023106PSC                          | 24 KB OTP 42 SDIP              |

|                          | Z9023106FSC                          | 24 KB OTP 44 PQFP              |

| Z90251                   | Z9025106PSC                          | 32 KB OTP TV controller        |

| Z90255                   | Z9025506PSC Rxxxx*                   | 32 KB masked ROM TV controller |

| Z9025900ZEM              | Z9025900ZEM                          | Emulator/programmer            |

| Z9020900TSC              | Z9020900TSC                          | Protopak                       |

| Z8933200ZCO              | Z8933200ZCO                          | OSD evaluation board           |

| * xxxx is a unique ROM r | number assigned to each customer cod | e.                             |

#### **Document Disclaimer**

© 2003 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Except with the express written approval ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses or other rights are conveyed, implicitly or otherwise, by this document under any intellectual property rights.