## **TABLE OF CONTENTS**

| Specifications                                             |

|------------------------------------------------------------|

| Electrical Characteristics—5 k $\Omega$ Version            |

| Electrical Characteristics—10 kΩ, 50 kΩ, 100 kΩ Versions 4 |

| Timing Characteristics                                     |

| Absolute Maximum Ratings                                   |

| ESD CAUTION                                                |

| Pin Configuration and Function Descriptions                |

| Typical Performance Characteristics                        |

| Test Circuits                                              |

| I <sup>2</sup> C Interface                                 |

| Operation13                                                |

### **REVISION HISTORY**

#### 5/12-Rev. B to Rev. C

| Changes to Features and General Description Sections | 1  |

|------------------------------------------------------|----|

| Changes to IDD Parameters, Table 1                   | 3  |

| Changes to IDD Parameters, Table 2                   | 4  |

| Changes to Figure 10                                 | 9  |

| Removed Evaluation Board Section                     | 15 |

| Changes to Ordering Guide                            | 16 |

#### 8/09—Rev. A to Rev. B

| Changes to Power Supply Sensitivity Parameter | 3  |

|-----------------------------------------------|----|

| Updated Outline Dimensions                    | 16 |

| Changes to Ordering Guide                     | 16 |

### 7/05—Rev. 0 to Rev. A

| Changes to Table 1                                | 3  |

|---------------------------------------------------|----|

| Changes to Table 2                                | 4  |

| Changes to Absolute Maximum Ratings               | 6  |

| Moved Pin Configuration and Function Descriptions | 7  |

| Deleted Table 7                                   | 12 |

| Changes to Operation Section                      | 13 |

| Deleted Figure 31                                 | 14 |

| Changes to Figure 30 and Figure 32                | 14 |

9/03—Revision 0: Initial Version

|   | Programming the Variable Resistor             | . 13 |

|---|-----------------------------------------------|------|

|   | I <sup>2</sup> C Compatible 2-Wire Serial Bus | . 13 |

|   | Level Shifting for Bidirectional Interface    | . 14 |

|   | ESD Protection                                | . 14 |

|   | Terminal Voltage Operating Range              | . 14 |

|   | Maximum Operating Current                     | . 14 |

|   | Power-Up Sequence                             | . 14 |

|   | Layout and Power Supply Bypassing             | . 15 |

|   | Constant Bias to Retain Resistance Setting    | . 15 |

| C | Outline Dimensions                            | . 16 |

|   | Ordering Guide                                | . 16 |

### **SPECIFICATIONS**

### **ELECTRICAL CHARACTERISTICS—5 kΩ VERSION**

$V_{DD} = 5 \text{ V} \pm 10\%$  or  $3 \text{ V} \pm 10\%$ ;  $V_A = +V_{DD}$ ;  $-40^{\circ}C < T_A < +125^{\circ}C$ , unless otherwise noted.

#### Table 1.

| Parameter                                       | Symbol                            | Conditions                                                            | Min  | Typ¹  | Max    | Unit   |

|-------------------------------------------------|-----------------------------------|-----------------------------------------------------------------------|------|-------|--------|--------|

| DC CHARACTERISTICS—RHEOSTAT MODE                |                                   |                                                                       |      |       |        |        |

| Resistor Differential Nonlinearity <sup>2</sup> | R-DNL                             | R <sub>WB</sub>                                                       | -1.5 | ±0.1  | +1.5   | LSB    |

| Resistor Integral Nonlinearity <sup>2</sup>     | R-INL                             | R <sub>WB</sub>                                                       | -4   | ±0.75 | +4     | LSB    |

| Nominal Resistor Tolerance <sup>3</sup>         | $\Delta R_{AB}$                   | $T_A = 25^{\circ}C$                                                   | -30  |       | +30    | %      |

| Resistance Temperature Coefficient              | $(\Delta R_{AB}/R_{AB})/\Delta T$ | Wiper = no connect                                                    |      | 45    |        | ppm/°C |

| R <sub>wb</sub>                                 | R <sub>WB</sub>                   | $Code = 0x00, V_{DD} = 5 V$                                           |      | 75    | 150    | Ω      |

|                                                 |                                   | $Code = 0x00, V_{DD} = 2.7 V$                                         |      | 150   | 400    | Ω      |

| RESISTOR TERMINALS                              |                                   |                                                                       |      |       |        |        |

| Voltage Range⁴                                  | V <sub>B, W</sub>                 |                                                                       | GND  |       | VDD    | V      |

| Capacitance <sup>5</sup> B                      | CB                                | f = 1 MHz, measured to GND, code = 0x40                               |      | 45    |        | рF     |

| Capacitance⁵ W                                  | Cw                                | f = 1 MHz, measured to GND, code = 0x40                               |      | 60    |        | pF     |

| Common-Mode Leakage                             | I <sub>CM</sub>                   |                                                                       |      | 1     |        | nA     |

| DIGITAL INPUTS AND OUTPUTS                      |                                   |                                                                       |      |       |        |        |

| Input Logic High                                | VIH                               | $V_{DD} = 5 V$                                                        | 2.4  |       |        | V      |

| Input Logic Low                                 | VIL                               | $V_{DD} = 5 V$                                                        |      |       | 0.8    | V      |

| Input Logic High                                | VIH                               | $V_{DD} = 3 V$                                                        | 2.1  |       |        | V      |

| Input Logic Low                                 | VIL                               | $V_{DD} = 3 V$                                                        |      |       | 0.6    | V      |

| Input Current                                   | l <sub>IL</sub>                   | $V_{IN} = 0 V \text{ or } 5 V$                                        |      |       | ±1     | μΑ     |

| Input Capacitance <sup>5</sup>                  | C⊫                                |                                                                       |      | 5     |        | pF     |

| POWER SUPPLIES                                  |                                   |                                                                       |      |       |        |        |

| Power Supply Range                              | V <sub>DD RANGE</sub>             |                                                                       | 2.7  |       | 5.5    | V      |

| Supply Current                                  | I <sub>DD</sub>                   | $V_{DD} = 5.5 \text{ V}; V_{IH} = V_{DD} \text{ or } V_{IL} = GND$    |      | 3     | 7      | μΑ     |

|                                                 |                                   | $V_{DD} = 5 \text{ V}; V_{IH} = V_{DD} \text{ or } V_{IL} = GND$      |      | 2.5   | 5.2    | μΑ     |

|                                                 |                                   | $V_{DD} = 3.3 \text{ V}; V_{H} = V_{DD} \text{ or } V_{IL} = GND$     |      | 0.9   | 2      | μΑ     |

| Power Dissipation <sup>6</sup>                  | PDISS                             | $V_{IH} = 5 \text{ V or } V_{IL} = 0 \text{ V}, V_{DD} = 5 \text{ V}$ |      |       | 40     | μW     |

| Power Supply Sensitivity                        | PSSR                              | $V_{DD}$ = +5 V ± 10%, code = midscale                                |      | ±0.01 | ±0.025 | %/%    |

| DYNAMIC CHARACTERISTICS <sup>5, 7</sup>         |                                   |                                                                       |      |       |        |        |

| Bandwidth –3 dB                                 | BW_5K                             | $R_{AB} = 5 k\Omega$ , code = 0x40                                    |      | 1.2   |        | MHz    |

| Total Harmonic Distortion                       | THDw                              | $V_A = 1 V rms$ , $V_B = 0 V$ , $f = 1 kHz$                           |      | 0.05  |        | %      |

| V <sub>w</sub> Settling Time                    | ts                                | $V_A = 5 V$ , $\pm 1 LSB$ error band                                  |      | 1     |        | μs     |

| Resistor Noise Voltage Density                  | e <sub>N_WB</sub>                 | $R_{WB} = 2.5 \text{ k}\Omega, R_S = 0 \Omega$                        |      | 6     |        | nV/√Hz |

<sup>1</sup> Typical specifications represent average readings at 25°C and  $V_{DD} = 5$  V.

positions. R-DNL measures the relative step change from ideal between successive tap positions. Parts are guaranteed monotonic. <sup>3</sup> Code = 0x7F. <sup>2</sup> Resistor position nonlinearity error R-INL is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper

<sup>4</sup> Resistor Terminal A and Resistor Terminal W have no limitations on polarity with respect to each other.

<sup>5</sup> Guaranteed by design; not subject to production test.

$^{6}$  P<sub>DISS</sub> is calculated from (I<sub>DD</sub> × V<sub>DD</sub>). CMOS logic level inputs result in minimum power dissipation.

$^{7}$  V<sub>DD</sub> = 5 V.

### ELECTRICAL CHARACTERISTICS—10 k $\Omega$ , 50 k $\Omega$ , 100 k $\Omega$ VERSIONS

$V_{DD}$  = 5 V ± 10% or 3 V ± 10%;  $V_A$  =  $V_{DD}$ ; -40°C <  $T_A$  < +125°C, unless otherwise noted.

Table 2.

| Parameter                                                           | Symbol                            | Conditions                                                                         | Min | Тур¹       | Max   | Unit   |

|---------------------------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------|-----|------------|-------|--------|

| DC CHARACTERISTICS, RHEOSTAT MODE                                   |                                   |                                                                                    |     |            |       |        |

| Resistor Differential Nonlinearity <sup>2</sup>                     | R-DNL                             | $R_{WB}$ , $V_A = no \ connect$                                                    | -1  | ±0.1       | +1    | LSB    |

| Resistor Integral Nonlinearity <sup>2</sup>                         | R-INL                             | $R_{WB}$ , $V_A$ = no connect                                                      | -2  | ±0.25      | +2    | LSB    |

| Nominal Resistor Tolerance <sup>3</sup>                             | $\Delta R_{AB}$                   | $T_A = 25^{\circ}C$                                                                | -20 |            | +20   | %      |

| Resistance Temperature Coefficient                                  | $(\Delta R_{AB}/R_{AB})/\Delta T$ | Wiper = no connect                                                                 |     | 45         |       | ppm/°C |

| R <sub>WB</sub>                                                     | R <sub>WB</sub>                   | $Code=0x00, V_{DD}=5 V$                                                            |     | 75         | 150   | Ω      |

|                                                                     |                                   | Code=0x00, V <sub>DD</sub> = 2.7 V                                                 |     | 150        | 400   | Ω      |

| RESISTOR TERMINALS                                                  |                                   |                                                                                    |     |            |       |        |

| Voltage Range⁴                                                      | V <sub>B, W</sub>                 |                                                                                    | GND |            | VDD   | V      |

| Capacitance <sup>5</sup> B                                          | CB                                | f = 1 MHz, measured to GND, code = 0x40                                            |     | 45         |       | рF     |

| Capacitance⁵ W                                                      | Cw                                | f = 1 MHz, measured to GND, code = 0x40                                            |     | 60         |       | рF     |

| Common-Mode Leakage                                                 | Ісм                               |                                                                                    |     | 1          |       | nA     |

| DIGITAL INPUTS AND OUTPUTS                                          |                                   |                                                                                    |     |            |       |        |

| Input Logic High                                                    | VIH                               | $V_{DD} = 5 V$                                                                     | 2.4 |            |       | V      |

| Input Logic Low                                                     | VIL                               | $V_{DD} = 5 V$                                                                     |     |            | 0.8   | V      |

| Input Logic High                                                    | VIH                               | $V_{DD} = 3 V$                                                                     | 2.1 |            |       | V      |

| Input Logic Low                                                     | VIL                               | $V_{DD} = 3 V$                                                                     |     |            | 0.6   | V      |

| Input Current                                                       | h <sub>L</sub>                    | $V_{IN} = 0 V \text{ or } 5 V$                                                     |     |            | ±1    | μA     |

| Input Capacitance⁵                                                  | CIL                               |                                                                                    |     | 5          |       | рF     |

| POWER SUPPLIES                                                      |                                   |                                                                                    |     |            |       |        |

| Power Supply Range                                                  | VDD RANGE                         |                                                                                    | 2.7 |            | 5.5   | V      |

| Supply Current                                                      | IDD                               | $V_{DD} = 5.5 \text{ V}; V_{IH} = V_{DD} \text{ or } V_{IL} = GND$                 |     | 3          | 7     | μA     |

|                                                                     |                                   | $V_{DD} = 5 \text{ V}; V_{IH} = V_{DD} \text{ or } V_{IL} = GND$                   |     | 2.5        | 5.2   | μA     |

|                                                                     |                                   | $V_{\text{DD}}$ = 3.3 V; $V_{\text{H}}$ = $V_{\text{DD}}$ or $V_{\text{IL}}$ = GND |     | 0.9        | 2     | μA     |

| Power Dissipation <sup>6</sup>                                      | P <sub>DISS</sub>                 | $V_{IH} = 5 \text{ V or } V_{IL} = 0 \text{ V}, V_{DD} = 5 \text{ V}$              |     |            | 40    | μW     |

| Power Supply Sensitivity                                            | PSSR                              | $V_{DD} = +5 V \pm 10\%$ , code = midscale                                         |     | ±0.01      | ±0.02 | %/%    |

| DYNAMIC CHARACTERISTICS <sup>5, 7</sup>                             |                                   |                                                                                    |     |            |       |        |

| Bandwidth –3 dB                                                     | BW                                | $R_{AB} = 10 \text{ k}\Omega/50 \text{ k}\Omega/100 \text{ k}\Omega$ , code = 0x40 |     | 600/100/40 |       | kHz    |

| Total Harmonic Distortion                                           | THDw                              | $V_A = 1 \text{ V rms}, f = 1 \text{ kHz}, R_{AB} = 10 \text{ k}\Omega$            |     | 0.05       |       | %      |

| $V_W$ Settling Time (10 k $\Omega$ /50 k $\Omega$ /100 k $\Omega$ ) | ts                                | $V_A = 5 V \pm 1 LSB$ error band                                                   |     | 2          |       | μs     |

| Resistor Noise Voltage Density                                      | en_wb                             | $R_{WB} = 5 k\Omega$ , $R_S = 0$                                                   |     | 9          |       | nV/√Hz |

<sup>1</sup> Typical specifications represent average readings at 25°C and  $V_{DD} = 5$  V. <sup>2</sup> Resistor position nonlinearity error R-INL is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions. R-DNL measures the relative step change from ideal between successive tap positions. Parts are guaranteed monotonic.

$^{3}$  Code = 0x7F.

<sup>4</sup> Resistor Terminal A and Resistor Terminal W have no limitations on polarity with respect to each other.

<sup>5</sup> Guaranteed by design; not subject to production test. <sup>6</sup> P<sub>DISS</sub> is calculated from ( $I_{DD} \times V_{DD}$ ). CMOS logic level inputs result in minimum power dissipation.

<sup>7</sup> All dynamic characteristics use  $V_{DD} = 5$  V.

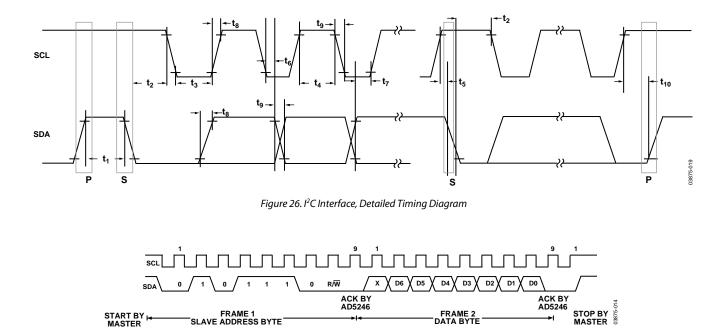

### **TIMING CHARACTERISTICS**

$V_{\rm DD}$  = 5 V  $\pm$  10% or 3 V  $\pm$  10%;  $V_{\rm A}$  =  $V_{\rm DD};$  –40°C <  $T_{\rm A}$  < +125°C, unless otherwise noted.

#### Table 3.

| Parameter                                                            | Symbol                  | Conditions                                  | Min | Typ <sup>1</sup> | Max | Unit |

|----------------------------------------------------------------------|-------------------------|---------------------------------------------|-----|------------------|-----|------|

| I <sup>2</sup> C INTERFACE TIMING CHARACTERISTICS <sup>2, 3, 4</sup> |                         |                                             |     |                  |     |      |

| SCL Clock Frequency                                                  | <b>f</b> <sub>SCL</sub> |                                             |     |                  | 400 | kHz  |

| t <sub>BUF</sub> Bus Free Time Between STOP and START                | t1                      |                                             | 1.3 |                  |     | μs   |

| t <sub>HD;sta</sub> Hold Time (Repeated START)                       | t <sub>2</sub>          | After this period, the first clock pulse is |     |                  |     |      |

|                                                                      |                         | generated                                   | 0.6 |                  |     | μs   |

| tLOW Low Period of SCL Clock                                         | t <sub>3</sub>          |                                             | 1.3 |                  |     | μs   |

| thigh High Period of SCL Clock                                       | t4                      |                                             | 0.6 |                  | 50  | μs   |

| tsu;sta Setup Time for Repeated START Condition                      | t <sub>5</sub>          |                                             | 0.6 |                  |     | μs   |

| t <sub>HD;DAT</sub> Data Hold Time                                   | t <sub>6</sub>          |                                             |     |                  | 0.9 | μs   |

| t <sub>su;DAT</sub> Data Setup Time                                  | t <sub>7</sub>          |                                             | 100 |                  |     | ns   |

| t <sub>F</sub> Fall Time of Both SDA and SCL Signals                 | t <sub>8</sub>          |                                             |     |                  | 300 | ns   |

| $t_R$ Rise Time of Both SDA and SCL Signals                          | t9                      |                                             |     |                  | 300 | ns   |

| tsu;sto Setup Time for STOP Condition                                | t10                     |                                             | 0.6 |                  |     | μs   |

$^1$  Typical specifications represent average readings at 25°C and V<sub>DD</sub> = 5 V.  $^2$  Guaranteed by design; not subject to production test.  $^3$  See timing diagrams (Figure 26, Figure 27, and Figure 28) for locations of measured values.  $^4$  Specifications apply to all parts.

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 4.

| Parameter                                                | Value                          |

|----------------------------------------------------------|--------------------------------|

| V <sub>DD</sub> to GND                                   | –0.3 V to +7 V                 |

| V <sub>A</sub> , V <sub>W</sub> to GND                   | V <sub>DD</sub>                |

| Terminal Current, A–B, A–W, B–W                          |                                |

| Pulsed <sup>1</sup>                                      | ±20 mA                         |

| Continuous                                               | ±5 mA                          |

| Digital Inputs and Output Voltage to GND                 | 0 V to $V_{\text{DD}}$ + 0.3 V |

| Operating Temperature Range                              | -40°C to +125°C                |

| Maximum Junction Temperature (T <sub>JMAX</sub> )        | 150°C                          |

| Storage Temperature                                      | –65°C to +150°C                |

| Lead Temperature (Soldering, 10 sec)                     | 300°C                          |

| Thermal Resistance <sup>2</sup> θ <sub>JA</sub> : SC70-6 | 340°C/W                        |

<sup>1</sup> Maximum terminal current is bounded by the maximum current handling of the switches, maximum power dissipation of the package, and maximum applied voltage across any two of the A, B, and W terminals at a given resistance.

<sup>2</sup> Package power dissipation =  $(T_{JMAX} - T_A)/\theta_{JA.}$

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

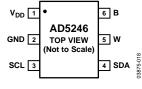

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 2. Pin Configuration

#### **Table 5. Pin Function Descriptions**

| Pin No. | Mnemonic        | Description                                  |

|---------|-----------------|----------------------------------------------|

| 1       | V <sub>DD</sub> | Positive Power Supply.                       |

| 2       | GND             | Digital Ground.                              |

| 3       | SCL             | Serial Clock Input. Positive edge triggered. |

| 4       | SDA             | Serial Data Input/Output.                    |

| 5       | W               | W Terminal.                                  |

| 6       | В               | B Terminal.                                  |

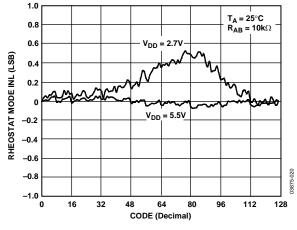

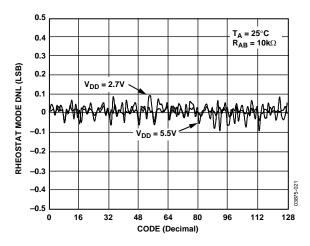

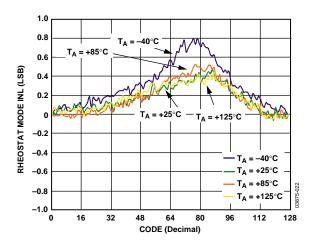

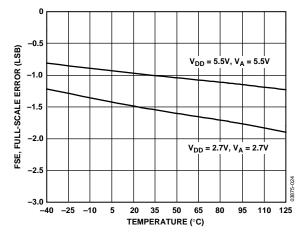

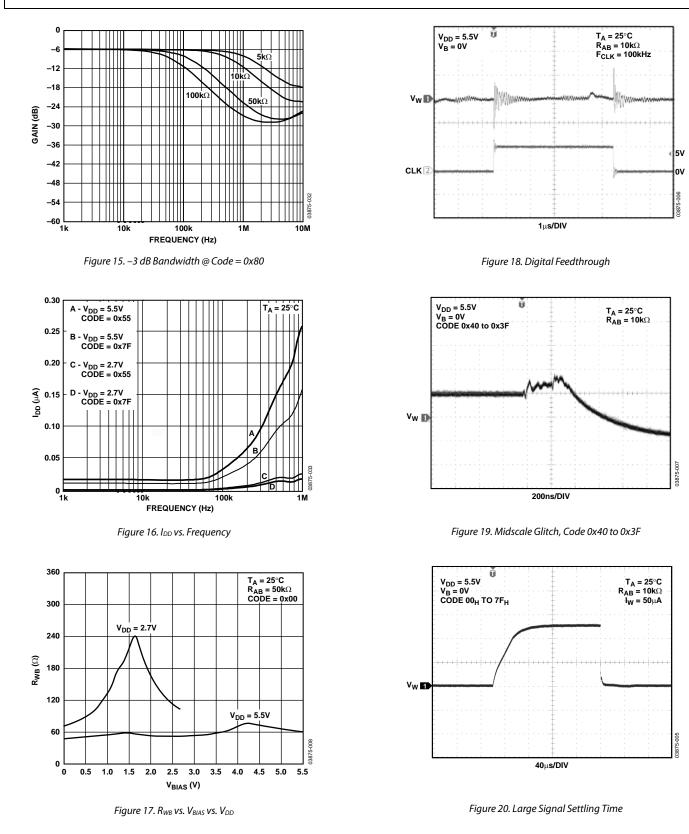

## **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 3. R-INL vs. Code vs. Supply Voltages

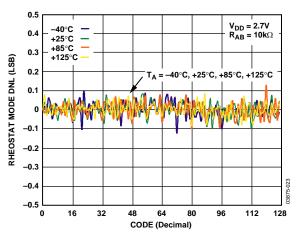

Figure 4. R-DNL vs. Code vs. Supply Voltages

Figure 5. R-INL vs. Code vs. Temperature

Figure 6. R-DNL vs. Code vs. Temperature

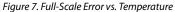

Figure 8. Zero-Scale Error vs. Temperature

## **Data Sheet**

#### 100 DIGITAL INPUTS = 0V CODE = 0x40 10 I<sub>DD</sub>, SUPPLY CURRENT (μA) V<sub>DD</sub> = 5.5V 1 V<sub>DD</sub> = 2.7V 0.1 33875 0.01 -40 -25 -10 35 5 20 50 65 80 95 110 125 TEMPERATURE (°C)

Figure 9. Supply Current vs. Temperature

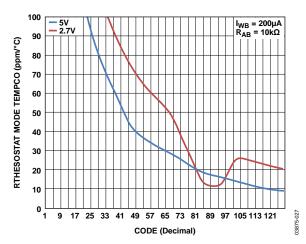

Figure 10. Rheostat Mode Tempco ΔR<sub>WB</sub>/ΔT vs. Code

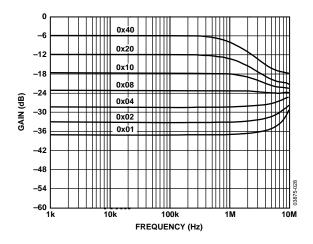

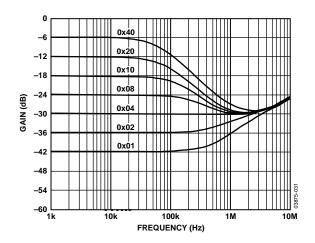

Figure 11. Gain vs. Frequency vs. Code,  $R_{AB} = 5 k\Omega$

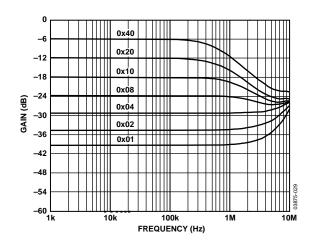

Figure 12. Gain vs. Frequency vs. Code,  $R_{AB} = 10 k\Omega$

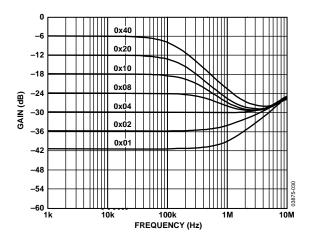

Figure 13. Gain vs. Frequency vs. Code,  $R_{AB} = 50 \text{ k}\Omega$

Figure 14. Gain vs. Frequency vs. Code,  $R_{AB} = 100 \text{ k}\Omega$

## AD5246

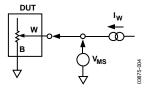

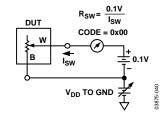

## **TEST CIRCUITS**

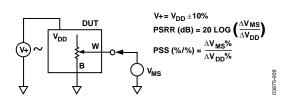

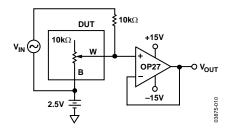

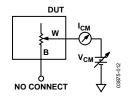

Figure 21 to Figure 25 define the test conditions used in the product Specification tables.

Figure 21. Test Circuit for Resistor Position Nonlinearity Error (Rheostat Operation; R-INL, R-DNL)

Figure 24. Test Circuit for Incremental On Resistance

Figure 22. Test Circuit for Power Supply Sensitivity (PSS, PSSR)

Figure 23. Test Circuit for Gain vs. Frequency

Figure 25. Test Circuit for Common-Mode Leakage Current

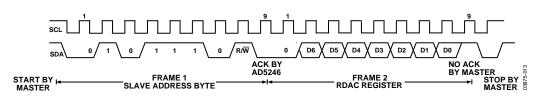

## I<sup>2</sup>C INTERFACE

| S | 0 | 1 | 0     | 1       | 1        | 1 | 0 | W | А | Х         | D6 | D5 | D4 | D3 | D2 | D1 | D0 | А | Р |

|---|---|---|-------|---------|----------|---|---|---|---|-----------|----|----|----|----|----|----|----|---|---|

|   |   |   | Slave | e Addre | ess Byte | 5 |   |   |   | Data Byte |    |    |    |    |    |    |    |   |   |

#### Table 7. Read Mode

| S | 0                  | 1 | 0 | 1 | 1 | 1 | 0         | R | А | 0 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | А | Р |

|---|--------------------|---|---|---|---|---|-----------|---|---|---|----|----|----|----|----|----|----|---|---|

|   | Slave Address Byte |   |   |   |   |   | Data Byte |   |   |   |    |    |    |    |    |    |    |   |   |

S = Start Condition.

P = Stop Condition.

A = Acknowledge.

X = Don't Care.

$\overline{W} = Write.$

R = Read.

D6, D5, D4, D3, D2, D1, D0 = Data Bits.

Figure 27. Writing to the RDAC Register

Figure 28. Reading from the RDAC Register

## **OPERATION**

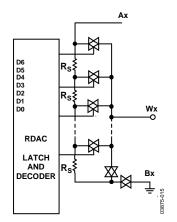

The AD5246 is a 128-position, digitally controlled variable resistor (VR) device.

# PROGRAMMING THE VARIABLE RESISTOR *Rheostat Operation*

The nominal resistance of the RDAC between Terminal A and Terminal B is available in 5 k $\Omega$ , 10 k $\Omega$ , 50 k $\Omega$ , and 100 k $\Omega$ . The final two or three digits of the part number determine the nominal resistance value, that is, 10 k $\Omega$  = 10, 50 k $\Omega$  = 50. The nominal resistance (R<sub>AB</sub>) of the VR has 128 contact points accessed by the wiper terminal. The 7-bit data in the RDAC latch is decoded to select one of the 128 possible settings.

The general equation determining the digitally programmed output resistance between W and B is

$$R_{WB}(D) = \frac{D}{128} \times R_{AB} + 2 \times R_{W} \tag{1}$$

where:

*D* is the decimal equivalent of the binary code loaded in the 7-bit RDAC register.

$R_{AB}$  is the end-to-end resistance.

$R_W$  is the wiper resistance contributed by the on resistance of each internal switch.

Figure 29. AD5246 Equivalent RDAC Circuit

Note that in the zero-scale condition, there is a relatively small finite wiper resistance. Care should be taken to limit the current flow between W and B in this state to a maximum pulse current of no more than 20 mA. Otherwise, degradation or possible destruction of the internal switch contact can occur.

Typical device-to-device matching is process lot dependent and may vary by up to  $\pm 30\%$ . Since the resistance element is processed in thin-film technology, the temperature coefficient of  $R_{AB}$  is only 45 ppm/°C.

### I<sup>2</sup>C COMPATIBLE 2-WIRE SERIAL BUS

The first byte of the AD5246 is a slave address byte (see Table 6 and Table 7). It has a 7-bit slave address and an  $R/\overline{W}$  bit. The seven MSBs of the slave address are 0101110 followed by 0 for a write command or 1 to place the device in read mode.

The 2-wire I<sup>2</sup>C serial bus protocol operates as follows:

1. The master initiates data transfer by establishing a START condition, which is when a high-to-low transition on the SDA line occurs while SCL is high (see Figure 27). The following byte is the slave address byte, which consists of the 7-bit slave address followed by an  $R/\overline{W}$  bit (this bit determines whether data will be read from or written to the slave device).

The slave whose address corresponds to the transmitted address responds by pulling the SDA line low during the ninth clock pulse (this is termed the acknowledge bit). At this stage, all other devices on the bus remain idle while the selected device waits for data to be written to or read from its serial register. If the R/W bit is high, the master reads from the slave device. Conversely, if the R/W bit is low, the master writes to the slave device.

- 2. In write mode, after acknowledgement of the slave address byte, the next byte is the data byte. Data is transmitted over the serial bus in sequences of nine clock pulses (eight data bits followed by an acknowledge bit). The transitions on the SDA line must occur during the low period of SCL and remain stable during the high period of SCL (see Table 6).

- 3. In read mode, after acknowledgment of the slave address byte, data is received over the serial bus in sequences of nine clock pulses (a slight difference from the write mode where eight data bits are followed by an acknowledge bit). Similarly, the transitions on the SDA line must occur during the low period of SCL and remain stable during the high period of SCL (see Figure 28).

- 4. When all data bits have been read or written, a STOP condition is established by the master. A STOP condition is defined as a low-to-high transition on the SDA line while SCL is high. In write mode, the master pulls the SDA line high during the tenth clock pulse to establish a STOP condition (see Figure 27). In read mode, the master issues a No Acknowledge for the ninth clock pulse (that is, the SDA line remains high). The master then brings the SDA line low before the tenth clock pulse, which goes high to establish a STOP condition (see Figure 28).

A repeated write function gives the user flexibility to update the RDAC output a number of times after addressing the part only once. For example, after the RDAC has acknowledged its slave address in write mode, the RDAC output updates on each successive byte. If different instructions are needed, the write/read mode has to start again with a new slave address and data byte. Similarly, a repeated read function of the RDAC is also allowed.

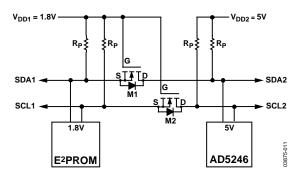

### LEVEL SHIFTING FOR BIDIRECTIONAL INTERFACE

While most legacy systems may be operated at one voltage, a new component may be optimized at another. When two systems operate the same signal at two different voltages, proper level shifting is needed. For instance, one can use a 1.8 V  $E^2PROM$  to interface with a 5 V digital potentiometer. A level shifting scheme is needed to enable a bidirectional communication so that the setting of the digital potentiometer can be stored to and retrieved from the  $E^2PROM$ . Figure 30 shows one of the implementations. M1 and M2 can be any N channel signal FETs, or if  $V_{DD}$  falls below 2.5 V, M1 and M2 can be low threshold FETs such as the FDV301N.

Figure 30. Level Shifting for Operation at Different Potentials

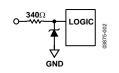

### **ESD PROTECTION**

All digital inputs are protected with a series input resistor and parallel Zener ESD structures, as shown in Figure 31. This applies to the digital input pins SDA and SCL.

Figure 31. ESD Protection of Digital Pins

### **TERMINAL VOLTAGE OPERATING RANGE**

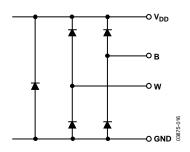

The AD5246  $V_{DD}$  and GND power supply defines the boundary conditions for proper 3-terminal digital potentiometer operation. Supply signals present on Terminal B and Terminal W that exceed  $V_{DD}$  or GND are clamped by the internal forward biased diodes (see Figure 32).

Figure 32. Maximum Terminal Voltages Set by V<sub>DD</sub> and GND

#### MAXIMUM OPERATING CURRENT

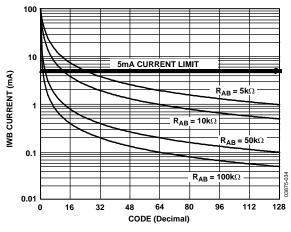

At low code values, the user should be aware that due to low resistance values, the current through the RDAC may exceed the 5 mA limit. In Figure 33, a 5 V supply is placed on the wiper, and the current through Terminal W and Terminal B is plotted with respect to code. A line is also drawn denoting the 5 mA current limit. Note that at low code values (particularly for the 5 k $\Omega$  and 10 k $\Omega$  options), the current level increases significantly. Care should be taken to limit the current flow between W and B in this state to a maximum continuous current of 5 mA and a maximum pulse current of no more than 20 mA. Otherwise, degradation or possible destruction of the internal switch contacts can occur.

Figure 33. Maximum Operating Current

#### **POWER-UP SEQUENCE**

Since the ESD protection diodes limit the voltage compliance at Terminal B and Terminal W (see Figure 32), it is important to power  $V_{DD}/GND$  before applying any voltage to Terminal B and Terminal W; otherwise, the diode is forward biased such that  $V_{DD}$  is powered unintentionally and may affect the rest of the user's circuit. The ideal power-up sequence is in the following order: GND,  $V_{DD}$ , digital inputs, and then  $V_B/V_W$ . The relative order of powering  $V_B$  and  $V_W$  and the digital inputs is not important, providing they are powered after  $V_{DD}/GND$ .

### LAYOUT AND POWER SUPPLY BYPASSING

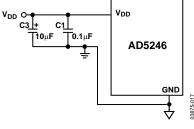

It is a good practice to use a compact, minimum lead-length layout design. The leads to the inputs should be as direct as possible with a minimum conductor length. Ground paths should have low resistance and low inductance.

Similarly, it is good practice to bypass the power supplies with quality capacitors for optimum stability. Supply leads to the device should be bypassed with 0.01  $\mu$ F to 0.1  $\mu$ F disc or chip ceramic capacitors. Low ESR 1  $\mu$ F to 10  $\mu$ F tantalum or electrolytic capacitors should also be applied at the supplies to minimize any transient disturbance and low frequency ripple (see Figure 34). Note that the digital ground should also be joined remotely to the analog ground at one point to minimize the ground bounce.

Figure 34. Power Supply Bypassing

#### CONSTANT BIAS TO RETAIN RESISTANCE SETTING

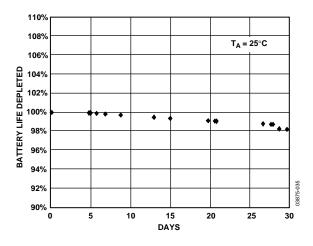

For users who desire nonvolatility but cannot justify the additional cost for the EEMEM, the AD5246 may be considered as a low cost alternative by maintaining a constant bias to retain the wiper setting. The AD5246 was designed specifically with low power in mind, which allows low power consumption even in battery-operated systems. The graph in Figure 35 demonstrates the power consumption from a 3.4 V 450 mA/hr Li-ion cell phone battery, which is connected to the AD5246. The measurement over time shows that the device draws approximately 1.3  $\mu$ A and consumes negligible power. Over a course of 30 days, the battery was depleted by less than 2%, the majority of which is due to the intrinsic leakage current of the battery itself.

Figure 35. Battery Operating Life Depletion

This demonstrates that constantly biasing the pot is not an impractical approach. Most portable devices do not require the removal of batteries for the purpose of charging. Although the resistance setting of the AD5246 will be lost when the battery needs replacement, such events occur rather infrequently, so that this inconvenience is justified by the lower cost and smaller size offered by the AD5246. If and when total power is lost, the user should be provided with a means to adjust the setting accordingly.

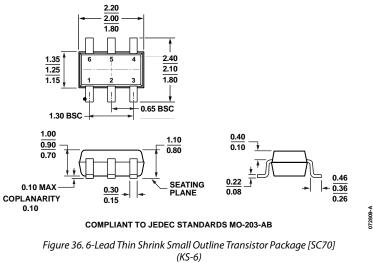

## **OUTLINE DIMENSIONS**

Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model <sup>1, 2</sup> | R <sub>AB</sub> (kΩ) | Temperature Range | Package Description     | Package Option | Branding |  |

|-----------------------|----------------------|-------------------|-------------------------|----------------|----------|--|

| AD5246BKSZ5-RL7       | 5                    | -40°C to +125°C   | 6-lead SC70             | KS-6           | D93      |  |

| AD5246BKSZ10-R2       | 10                   | -40°C to +125°C   | 6-lead SC70             | KS-6           | D92      |  |

| AD5246BKSZ10-RL7      | 10                   | –40°C to +125°C   | 6-lead SC70             | KS-6           | D92      |  |

| AD5246BKSZ50-RL7      | 50                   | –40°C to +125°C   | 6-lead SC70             | KS-6           | D94      |  |

| AD5246BKSZ100-R2      | 100                  | -40°C to +125°C   | 6-lead SC70             | KS-6           | D9D      |  |

| AD5246BKSZ100-RL7     | 100                  | -40°C to +125°C   | 6-lead SC70             | KS-6           | D9D      |  |

| EVAL-AD5246DBZ        |                      |                   | <b>Evaluation Board</b> |                |          |  |

<sup>1</sup> Z = RoHS Compliant Part.

$^{2}$  The evaluation board is shipped with the 10 k $\Omega$  R<sub>AB</sub> resistor option; however, the board is compatible with all available resistor value options.

Purchase of licensed I<sup>2</sup>C components of Analog Devices or one of its sublicensed Associated Companies conveys a license for the purchaser under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

© 2003–2012 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D03875–0–5/12(C)

www.analog.com

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.:

EVAL-AD5246DBZ AD5246BKSZ100-R2 AD5246BKSZ100-RL7 AD5246BKSZ10-RL7 AD5246BKSZ50-RL7 AD5246BKSZ5-RL7