### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND0.3V to +4.0V                   |  |

|-------------------------------------------------------|--|

| IN_+, IN, OUT_+, OUT to GND0.3V to +4.0V              |  |

| EN_, SEL_, NC/RSEL to GND0.3V to ( $V_{CC}$ + 0.3V)   |  |

| Short-Circuit Duration (OUT_+, OUT)Continuous         |  |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |  |

| 16-Pin SO (derate 8.7mW/°C above +70°C)696mW          |  |

|                                                       |  |

| Storage Temperature Range         | 65°C to +150°C |

|-----------------------------------|----------------|

| Junction Temperature              | +150°C         |

| Operating Temperature Range       | 40°C to +85°C  |

| Lead Temperature (soldering, 10s) | +300°C         |

| ESD Protection                    |                |

| Human Body Model IN + IN - OUT    | + OUT - +7kV   |

16-Pin TSSOP (derate 9.4mW/°C above +70°C) .......755mW

Human Body Model, IN\_+, IN\_-, OUT\_+, OUT\_-..... ±7kV

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +3.0V \text{ to } +3.6V, \text{ NC/RSEL} = \text{open for } R_L = 75\Omega \pm 1\%, \text{ NC/RSEL} = \text{high for } R_L = 100\Omega \pm 1\%, \text{ differential input voltage } |V_{\text{ID}}| = 100\Omega \pm 1\%$ 0.1V to V<sub>CC</sub>, input voltage (V<sub>IN+</sub>, V<sub>IN-</sub>) = 0 to V<sub>CC</sub>, EN\_ = high, SEL0 = low, SEL1 = high, and T<sub>A</sub> = -40°C to +85°C. Typical values at  $V_{CC} = +3.3V$ ,  $|V_{ID}| = 0.2V$ , input common-mode voltage  $V_{CM} = 1.2V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                              | SYMBOL                              | CONDITIONS                                                               | MIN   | TYP | MAX             | UNITS |  |  |

|----------------------------------------|-------------------------------------|--------------------------------------------------------------------------|-------|-----|-----------------|-------|--|--|

| LVCMOS/LVTTL INPUTS (EN_, SEL_)        |                                     |                                                                          |       |     |                 |       |  |  |

| Input High Voltage                     | VIH                                 |                                                                          | 2.0   |     | V <sub>CC</sub> | V     |  |  |

| Input Low Voltage                      | VIL                                 |                                                                          | GND   |     | 0.8             | V     |  |  |

| Input High Current                     | Ιн                                  | $V_{IN} = V_{CC} \text{ or } 2.0 \text{V}$                               | 0     |     | 20              | μΑ    |  |  |

| Input Low Current                      | ١ <sub>١</sub> ٢                    | $V_{IN} = 0 \text{ or } 0.8 \text{V}$                                    | -10   |     | 10              | μΑ    |  |  |

| NC/RSEL INPUT                          |                                     |                                                                          |       |     |                 |       |  |  |

| Input High Voltage                     | VIH                                 |                                                                          | 2.0   |     | V <sub>CC</sub> | V     |  |  |

| Input Low Voltage                      | VIL                                 |                                                                          | GND   |     | 0.8             | V     |  |  |

| Input High Current                     | IIН                                 | $V_{IN} = V_{CC} \text{ or } 2.0 \text{V}$                               | 0     |     | 20              | μΑ    |  |  |

| Input Low Current                      | ١ <sub>١</sub> ٢                    | $V_{IN} = 0 \text{ or } 0.8 \text{V}$                                    | -10   |     | 10              | μΑ    |  |  |

| DIFFERENTIAL INPUTS (IN_+, IN_         | )                                   |                                                                          |       |     |                 |       |  |  |

| Differential Input High Threshold      | V <sub>TH</sub>                     |                                                                          |       |     | 100             | mV    |  |  |

| Differential Input Low Threshold       | V <sub>TL</sub>                     |                                                                          | -100  |     |                 | mV    |  |  |

|                                        |                                     | $V_{IN+} = V_{CC} \text{ or } 0, V_{IN-} = V_{CC} \text{ or } 0$         | -1    |     | 1               |       |  |  |

| Input Current                          | I <sub>IN+</sub> , I <sub>IN-</sub> | $V_{IN+} = 3.6V \text{ or } 0, V_{IN-} = 3.6V \text{ or } 0, V_{CC} = 0$ | -1    |     | 1               | μA    |  |  |

| LVDS OUTPUTS (OUT_+, OUT)              | •                                   |                                                                          | •     |     |                 | •     |  |  |

| Differential Output Impedance          |                                     | NC/RSEL = low or open                                                    | 60    | 90  | 118             |       |  |  |

| (Note 2)                               | RDIFF                               | NC/RSEL = high                                                           | 85    | 122 | 155             | Ω     |  |  |

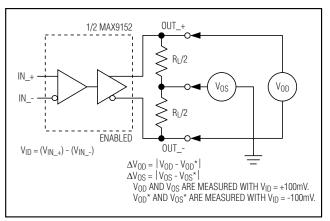

|                                        |                                     | $R_L = 75\Omega$ , NC/RSEL = open, Figure 1                              | 280   | 382 | 470             |       |  |  |

| Differential Output Voltage            | VOD                                 | $R_L = 100\Omega$ , NC/RSEL = high, Figure 1                             | 200   | 302 | 470             | mV    |  |  |

| Change in Magnitude of V <sub>OD</sub> |                                     | $R_L = 75\Omega$ , NC/RSEL = open, Figure 1                              |       |     | 25              | mV    |  |  |

| Between Complementary Output States    | $\Delta V_{OD}$                     | $R_L = 100\Omega$ , NC/RSEL = high, Figure 1                             |       |     | 25              | mv    |  |  |

| Offeet Common Made Valters             |                                     | $R_L = 75\Omega$ , NC/RSEL = open, Figure 1                              | 1.150 |     | 1 400           | V     |  |  |

| Offset Common-Mode Voltage             | Vos                                 | $R_L = 100\Omega$ , NC/RSEL = high, Figure 1                             | 1.150 |     | 1.430           | v     |  |  |

| Change in Magnitude of V <sub>OS</sub> |                                     | $R_L = 75\Omega$ , NC/RSEL = open, Figure 1                              |       |     | 05              | mV    |  |  |

| Between Complementary Output States    | $\Delta V_{OS}$                     | $R_L = 100\Omega$ , NC/RSEL = high, Figure 1                             |       |     | 25              |       |  |  |

M/XI/M

## DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +3.0V \text{ to } +3.6V, \text{ NC/RSEL} = \text{open for } R_L = 75\Omega \pm 1\%, \text{ NC/RSEL} = \text{high for } R_L = 100\Omega \pm 1\%, \text{ differential input voltage } |V_{ID}| = 0.1V \text{ to } V_{CC}, \text{ input voltage } (V_{IN+}, V_{IN-}) = 0 \text{ to } V_{CC}, \text{ EN}_{-} = \text{high}, \text{ SEL0} = \text{low}, \text{ SEL1} = \text{high}, \text{ and } T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}. \text{ Typical values at } V_{CC} = +3.3V, |V_{ID}| = 0.2V, \text{ input common-mode voltage } V_{CM} = 1.2V, T_A = +25^{\circ}\text{C}, \text{ unless otherwise noted.} ) (Note 1)$

| PARAMETER                         | SYMBOL                              | CONDITIONS                                                                                      | MIN | TYP | MAX | UNITS |

|-----------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Output Short-Circuit Current      |                                     | $V_{ID}$ = +100mV, $V_{OUT_+}$ = 0, other output open                                           |     | -12 | -20 | mA    |

| Output Short-Circuit Current      | IOS                                 | $V_{ID} = -100 \text{mV}, V_{OUT_{-}} = 0,$<br>other output open                                |     |     | -20 | ШA    |

| Both Output Short-Circuit Current | IOSB                                | $V_{ID} = +100mV, V_{OUT_+} = 0, V_{OUT} = 0$                                                   |     | -12 | -20 | mA    |

|                                   | IO2B                                | $V_{ID} = -100 \text{mV}, V_{OUT_+} = 0, V_{OUT} = 0$                                           |     | -12 | -20 | ША    |

| Output High-Z Current             | I <sub>OZ+</sub> , I <sub>OZ-</sub> | Disabled, V <sub>OUT_+</sub> = V <sub>CC</sub> or 0,<br>V <sub>OUT</sub> = V <sub>CC</sub> or 0 | -1  |     | 1   | μΑ    |

| Power-Off Output Current          | IOFF+, IOFF-                        | $V_{CC} = 0, V_{OUT_+} = 3.6V \text{ or } 0, V_{OUT} = 3.6V \text{ or } 0$                      | -1  |     | 1   | μΑ    |

| SUPPLY CURRENT                    |                                     |                                                                                                 |     |     |     |       |

|                                   |                                     | $R_L$ = 75 $\Omega, C_L$ = 5pF, enabled, quiescent, Figure 5                                    |     | 38  | 55  |       |

| Supply Current                    |                                     | $R_L$ = 100 $\Omega,C_L$ = 5pF, enabled, quiescent, Figure 5                                    |     | 33  | 50  | ~^^   |

| Supply Current                    | Icc                                 | $R_L$ = 75 $\Omega$ , $C_L$ = 5pF, enabled, switching at 400MHz (800Mbps), Figure 5 (Note 2)    |     | 58  | 70  | mA    |

|                                   |                                     | $R_L$ = 100 $\Omega,C_L$ = 5pF, enabled, switching at 400MHz (800Mbps), Figure 5 (Note 2)       |     | 52  | 65  |       |

| High-Z Supply Current             | ICCZ                                | Disabled                                                                                        |     | 15  | 25  | mA    |

## **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.0V \text{ to } +3.6V, \text{NC/RSEL} = \text{open for } R_L = 75\Omega \pm 1\%, \text{NC/RSEL} = \text{high for } R_L = 100\Omega \pm 1\%, \text{C}_L = 5\text{pF}, \text{ differential input voltage}$  $|V_{ID}| = 0.15V \text{ to } V_{CC}, \text{EN}_{-} = \text{high}, \text{SEL0} = \text{low}, \text{SEL1} = \text{high, differential input transition time} = 0.6\text{ns}$  (20% to 80%), input voltage  $(V_{IN+}, V_{IN-}) = 0$  to  $V_{CC}$ , LVCMOS/LVTTL inputs = 0 to 3V with 2ns (10% to 90%) transition times,  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ . Typical values at  $V_{CC} = +3.3V$ ,  $|V_{ID}| = 0.2V$ ,  $V_{CM} = 1.2V$ ,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted.) (Notes 3, 4)

| PARAMETER                        | SYMBOL            | CONDITIONS                                             | MIN | ТҮР | MAX | UNITS |

|----------------------------------|-------------------|--------------------------------------------------------|-----|-----|-----|-------|

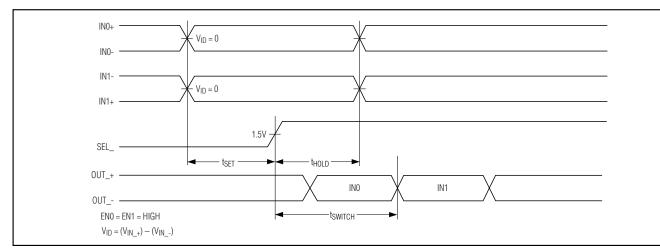

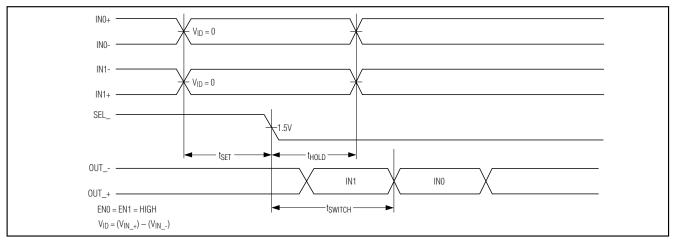

| Input to SEL Setup Time (Note 5) | <b>t</b> SET      | Figures 2, 3                                           | 0.4 |     |     | ns    |

| Input to SEL Hold Time (Note 5)  | <b>t</b> HOLD     | Figures 2, 3                                           | 0.6 |     |     | ns    |

| SEL to Switched Output           | tswitch           | Figures 2, 3                                           | 1.8 | 2.5 | 3.5 | ns    |

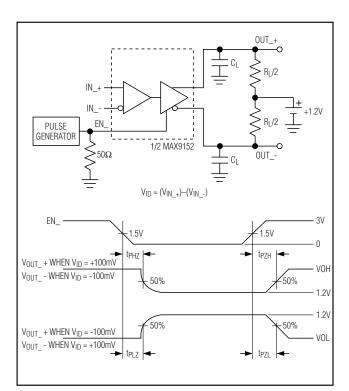

| Disable Time High to Z           | t <sub>PHZ</sub>  | Figure 4                                               |     |     | 3.8 | ns    |

| Disable Time Low to Z            | t <sub>PLZ</sub>  | Figure 4                                               |     |     | 3.8 | ns    |

| Enable Time Z to High            | t <sub>PZH</sub>  | Figure 4                                               |     |     | 3.2 | ns    |

| Enable Time Z to Low             | t <sub>PZL</sub>  | Figure 4                                               |     |     | 3.2 | ns    |

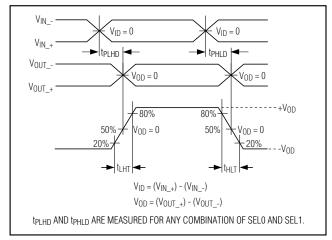

| Propagation Law to High Dalay    | to:               | Figures 5, 6                                           | 1.7 | 2.3 | 3.4 | 20    |

| Propagation Low-to-High Delay    | <sup>t</sup> PLHD | $V_{CC} = +3.3V$ , $T_A = +25^{\circ}C$ ; Figures 5, 6 | 2.0 | 2.3 | 2.9 | ns    |

| Propagation High to Law Dalay    | to:               | Figures 5, 6                                           | 1.7 | 2.3 | 3.4 | 20    |

| Propagation High-to-Low Delay    | <sup>t</sup> PHLD | $V_{CC} = +3.3V$ , $T_A = +25^{\circ}C$ ; Figures 5, 6 | 2.0 | 2.3 | 2.9 | ns    |

## AC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +3.0V \text{ to } +3.6V, \text{NC/RSEL} = \text{open for } R_L = 75\Omega \pm 1\%, \text{NC/RSEL} = \text{high for } R_L = 100\Omega \pm 1\%, \text{C}_L = 5\text{pF}, \text{ differential input voltage}$  $|V_{|D}| = 0.15V \text{ to } V_{CC}, \text{EN}_{-} = \text{high}, \text{SEL0} = \text{low}, \text{SEL1} = \text{high, differential input transition time} = 0.6\text{ns}$  (20% to 80%), input voltage  $(V_{|N+}, V_{|N-}) = 0$  to  $V_{CC}, \text{LVCMOS/LVTTL inputs} = 0$  to 3V with 2ns (10% to 90%) transition times,  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ . Typical values at  $V_{CC} = +3.3V, |V_{|D}| = 0.2V, V_{CM} = 1.2V, T_A = +25^{\circ}\text{C}, \text{ unless otherwise noted.}$  (Notes 3, 4)

| PARAMETER                                          | SYMBOL           | CONDITIONS                                                                                                                           | MIN | TYP | MAX | UNITS |

|----------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Pulse Skew ItpLHD -tpHLDI (Note 6)                 | <b>t</b> SKEW    | Figures 5, 6                                                                                                                         |     | 25  | 90  | ps    |

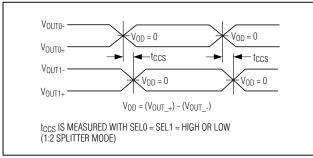

| Output Channel-to-Channel Skew                     | tccs             | Figures 5, 7                                                                                                                         |     | 20  | 50  | ps    |

| Output Low-to-High Transition<br>Time (20% to 80%) | t <sub>LHT</sub> | Figures 5, 6                                                                                                                         | 160 | 270 | 480 | ps    |

| Output High-to-Low Transition<br>Time (20% to 80%) | thlt             | Figures 5, 6                                                                                                                         | 160 | 270 | 480 | ps    |

| LVDS Data Path Peak-to-Peak                        | tur              | $V_{ID}$ = 200mV, $V_{CM}$ = 1.2V, 50% duty<br>cycle, 800Mbps, input transition time =<br>600ps (20% to 80%)                         |     | 10  | 30  |       |

| Jitter (Note 7)                                    | tji⊤             | $V_{ID}$ = 200mV, $V_{CM}$ = 1.2V, PRBS = 2 <sup>23</sup> -1<br>data pattern, 800Mbps, input transition<br>time = 600ps (20% to 80%) |     | 65  | 120 | ps    |

Note 1: Current into a pin is defined as positive. Current out of a pin is defined as negative. All voltages are referenced to ground except V<sub>TH</sub>, V<sub>TL</sub>, V<sub>ID</sub>, V<sub>OD</sub>, and ΔV<sub>OD</sub>.

Note 2: Guaranteed by design and characterization, not production tested.

Note 3: AC parameters are guaranteed by design and characterization.

Note 4: CL includes scope probe and test jig capacitance.

Note 5: t<sub>SET</sub> and t<sub>HOLD</sub> time specify that data must be in a stable state before and after the SEL transition.

Note 6: tSKEW is the magnitude difference of differential propagation delay over rated conditions; tSKEW = ltPHLD - tPLHDl.

Note 7: Specification includes test equipment jitter.

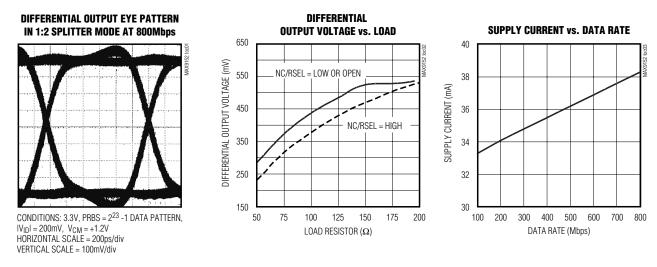

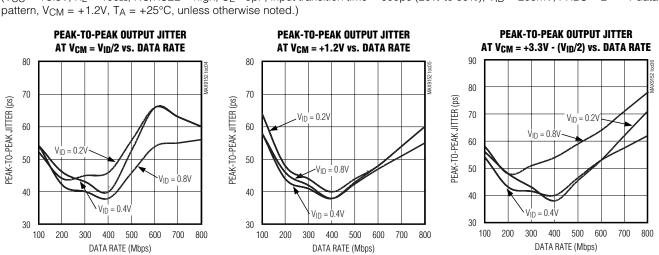

## **Typical Operating Characteristics**

$(V_{CC} = +3.3V, R_L = 100\Omega, NC/RSEL = high, C_L = 5pF$ , input transition time = 600ps (20% to 80%),  $V_{ID} = 200mV$ , PRBS =  $2^{23}$  - 1 data pattern,  $V_{CM} = +1.2V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

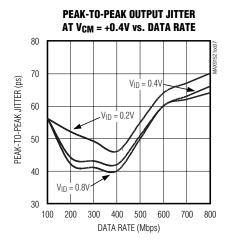

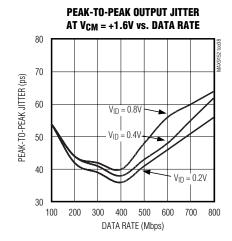

### **Typical Operating Characteristics (continued)**

$(V_{CC} = +3.3V, R_L = 100\Omega, NC/RSEL = high, C_L = 5pF$ , input transition time = 600ps (20% to 80%),  $V_{ID} = 200mV$ , PRBS =  $2^{23}$  - 1 data pattern,  $V_{CM} = +1.2V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

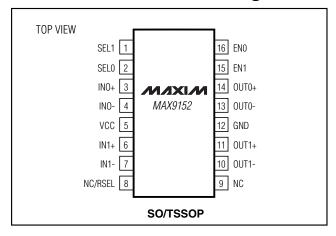

Pin Description

| PIN    | NAME            | FUNCTION                                                                                                                                                                                                                                                              |

|--------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2   | SEL1, SEL0      | LVCMOS/LVTTL Logic Inputs. Allow the switch to be configured as a mux, repeater, or splitter.                                                                                                                                                                         |

| 3, 4   | IN0+, IN0-      | LVDS/LVPECL Differential Input 0                                                                                                                                                                                                                                      |

| 5      | V <sub>CC</sub> | Power-Supply Input. Bypass V <sub>CC</sub> to GND with 0.1 $\mu$ F and 0.001 $\mu$ F ceramic capacitors.                                                                                                                                                              |

| 6, 7   | IN1+, IN1-      | LVDS/LVPECL Differential Input 1                                                                                                                                                                                                                                      |

| 8      | NC/RSEL         | Logic Input. Selects differential output resistance. Set NC/RSEL to open or low when $R_L = 75\Omega$ , set to high when $R_L = 100\Omega$ .                                                                                                                          |

| 9      | NC              | No Connect                                                                                                                                                                                                                                                            |

| 10, 11 | OUT1-,<br>OUT1+ | LVDS Differential Output 1                                                                                                                                                                                                                                            |

| 12     | GND             | Ground                                                                                                                                                                                                                                                                |

| 13, 14 | OUT0-,<br>OUT0+ | LVDS Differential Output 0                                                                                                                                                                                                                                            |

| 15, 16 | EN1, ENO        | LVCMOS/LVTTL Logic Inputs. Enables or disables the outputs. Setting EN0 or EN1 high enables the corresponding output, OUT0 or OUT1. Setting EN0 or EN1 low puts the corresponding output into high impedance (differential output resistance is also high impedance). |

### **Detailed Description**

The LVDS interface standard is a signaling method intended for point-to-point communication over a controlled impedance medium as defined by the ANSI TIA/EIA-644 and IEEE 1596.3 standards. LVDS uses a lower voltage swing than other common communication standards, achieving higher data rates with reduced power consumption while reducing EMI emissions and system susceptibility to noise.

The MAX9152 is an 800Mbps 2 x 2 crosspoint switch designed for high-speed, low-power point-to-point and multidrop interfaces. The device accepts LVDS or differential LVPECL signals and routes them to outputs depending on the selected mode of operation.

A differential input with a magnitude of 0.1V to V<sub>CC</sub> with single-ended voltage levels at or within the MAX9152's V<sub>CC</sub> and ground switches the output. A differential input with a magnitude of at least 0.15V with single-ended voltage levels at or within the MAX9152's V<sub>CC</sub> and ground is required to meet the AC specifications.

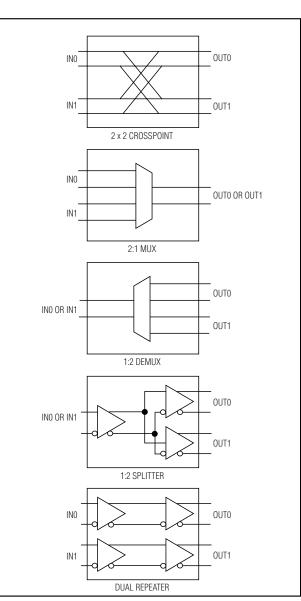

In the 1:2 splitter mode, the outputs repeat the selected input. This is useful for distributing a signal or creating a copy for use in protection switching. In the repeater

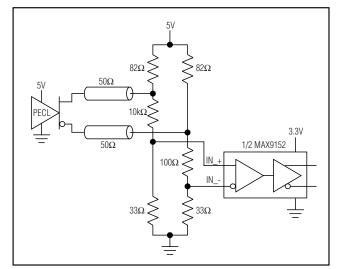

Figure 1. Test Circuit for V<sub>OD</sub> and V<sub>OS</sub>

mode, the device operates as a two-channel buffer. Repeating restores signal amplitude, allowing isolation of media segments or longer media drive. The device is a crosspoint switch where any input can be connected to any output or outputs. In 2:1 mux mode, primary and backup signals can be selected to provide a protection-switched, fault-tolerant application.

Figure 2. Input to Rising Edge Select Setup, Hold, and Mux Switch Timing Diagram

Figure 3. Input to Falling Edge Select Setup, Hold, and Mux Switch Timing Diagram

### Input Fail-Safe

The differential inputs of the MAX9152 do not have internal fail-safe biasing. If fail-safe biasing is required, it can be implemented with external large-value resistors. IN\_+ should be pulled up to V<sub>CC</sub> with 10k $\Omega$  and IN\_ should be pulled down to GND with 10k $\Omega$ . The voltage-divider formed by the 10k $\Omega$  resistors and the 100 $\Omega$  termination resistor (across IN\_+ and IN\_-) provides a slight positive differential bias and sets a high state at the device output when inputs are undriven.

#### **Output Resistance**

The MAX9152 has a selectable differential output resistance to reduce reflections from impedance discontinuities in the interconnect. Reflections are reduced, compared to a high-impedance output. A termination resistor at the receiver is still required and is the primary termination for the interconnect. Select the output resistance that best matches the differential characteristic impedance of the interconnect used.

#### Select Function

The SEL0 and SEL1 logic inputs allow the device to be configured as a high-speed differential crosspoint, 2:1 mux, 1:2 demux, dual repeater, or 1:2 splitter (Figure 8). See Table 1 for mode selection settings.

#### **Enable Function**

The EN0 and EN1 logic inputs enable and disable driver outputs OUT0 and OUT1. Setting EN0 or EN1 high enables the corresponding driver output. Setting EN0

7

or EN1 low puts the corresponding driver output into a high-impedance state (the differential output resistance also becomes high impedance).

Figure 4. Output Active to High-Z and High-Z to Active Test Circuit and Timing Diagram

### Table 1. Input/Output Function Table

| SEL0 | SEL1 | OUT0 | OUT1 | MODE         |

|------|------|------|------|--------------|

| L    | L    | IN0  | INO  | 1:2 splitter |

| L    | Н    | IN0  | IN1  | Repeater     |

| Н    | L    | IN1  | IN0  | Switch       |

| Н    | Н    | IN1  | IN1  | 1:2 splitter |

### **Applications Information**

### **Unused Differential Inputs**

Unused differential inputs should be tied to ground and V<sub>CC</sub> to prevent the high-speed input stage from switching due to noise. IN\_+ should be pulled to V<sub>CC</sub> with 10k $\Omega$  and IN\_- should be pulled to GND with 10k $\Omega$ .

### Expanding the Number of LVDS Output Ports

Devices can be cascaded to make larger switches. Total propagation delay and total jitter should be considered to determine the maximum allowable switch size. Three MAX9152s are needed to make a 2 input x 4 output crosspoint switch with two device propagation delays. Seven MAX9152s make a 2 input x 8 output crosspoint with three device delays.

### Accepting PECL Inputs

The inputs accept PECL signals with the use of an attenuation circuit, as shown in Figure 9.

### **Power-Supply Bypassing**

Bypass V<sub>CC</sub> to ground with high-frequency surfacemount ceramic  $0.1\mu$ F and  $0.001\mu$ F capacitors in paral-

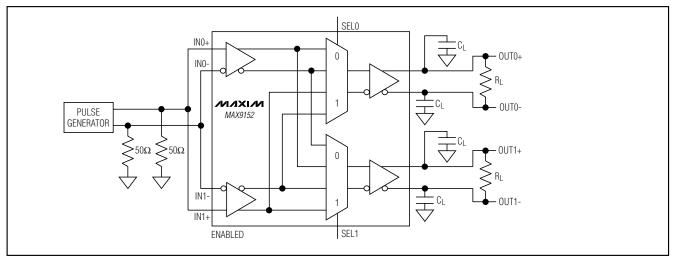

Figure 5. Output Transition Time, Propagation Delay, and Output Channel-to-Channel Skew Test Circuit

Figure 6. Output Transition Time and Propagation Delay Timing Diagram

Figure 7. Output Channel-to-Channel Skew

lel as close to the device as possible, with the smaller value capacitor closest to  $V_{\mbox{CC}}.$

### **Differential Traces**

Trace characteristics affect the performance of the MAX9152. Use controlled-impedance traces. Eliminate reflections and ensure that noise couples as common mode by running the differential trace pairs close together. Reduce skew by matching the electrical length of the traces. Excessive skew can result in a degradation of magnetic field cancellation.

Maintain the distance between the differential traces to avoid discontinuities in differential impedance. Avoid 90° turns and minimize the number of vias to further prevent impedance discontinuities.

### **Cables and Connectors**

Transmission media should have nominal differential impedance of 75 $\Omega$  or 100 $\Omega$ . Use cables and connectors that have matched differential impedance to minimize impedance discontinuities.

Figure 8. Programmable Configurations

Avoid the use of unbalanced cables such as ribbon or simple coaxial cable. Balanced cables such as twisted pair offer superior signal quality and tend to generate less EMI due to canceling effects. Balanced cables tend to pick up noise as common mode, which is rejected by the differential receiver.

#### **Board Layout**

For LVDS applications, a four-layer printed-circuit (PC) board that provides separate power, ground, and signal planes is recommended.

Figure 9. PECL to LVDS Level Conversion Network

### **Pin Configuration**

**Chip Information**

TRANSISTOR COUNT: 880 PROCESS: CMOS

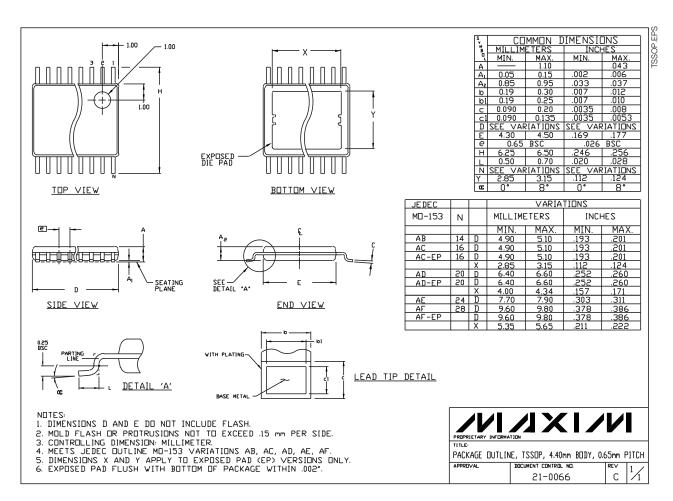

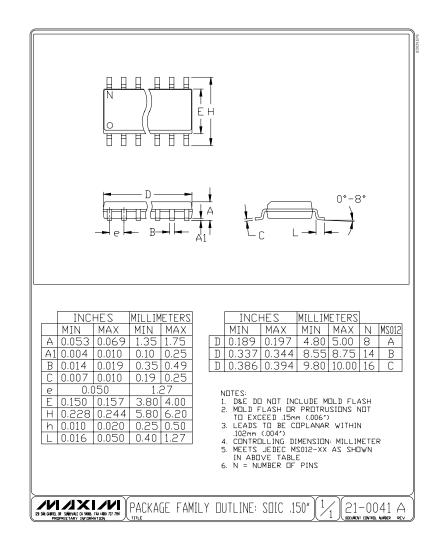

## **Package Information**

M/IXI/N

**Package Information (continued)**

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

12

**MAX9152**

\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2001 Maxim Integrated Products

Printed USA

**MAXIM** is a registered trademark of Maxim Integrated Products.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated: <u>MAX9152ESE+</u> MAX9152ESE+T MAX9152EUE+ MAX9152EUE+T