### **ABSOLUTE MAXIMUM RATINGS**

| LDOH to IN<br>LDOL to GND<br>PDRV to GND<br>NDRV to GND<br>TOFF, REF, SET, TERM, CC to<br>D0, D1 to GND<br>CS+, CS- to GND | 0.3V to +28V<br>+0.3V to -6V<br>0.3V to +6V<br>(V <sub>LDOH</sub> - 0.3V) to (V <sub>IN</sub> + 0.3V)<br>0.3V to (V <sub>LDOL</sub> + 0.3V)<br>GND0.3V to (V <sub>LDOL</sub> + 0.3V)<br>0.3V to +6V<br>0.3V to +28V |

|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                            | 0.3V to +28V<br>±0.3V                                                                                                                                                                                               |

|                                                                                                                            |                                                                                                                                                                                                                     |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )            |

|------------------------------------------------------------------|

| QSOP (derate 9.6mW/°C above +70°C) 772mW                         |

| Package Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) |

| (Note 1)103.7°C/W                                                |

| Package Junction-to-Case Thermal Resistance $\theta_{JC}$ )      |

| (Note1)                                                          |

| Operating Temperature Range                                      |

| MAX164_EEE40°C to +85°C                                          |

| Storage Temperature Range65°C to +150°C                          |

| Lead Temperature (soldering, 10sec) +300°C                       |

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal comsiderations, refer to <u>www.maxim-ic.com/thermal-tutorial</u>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = +12V, V_{OUT} = 6V, Circuit of Figure 1, T_A = 0^{\circ}C to +85^{\circ}C, unless otherwise noted. Typical values are at T_A = +25^{\circ}C.)$

| PARAMETER                                                      | SYMBOL | CON                                          | DITIONS                                         | MIN  | TYP                      | MAX                      | UNITS |

|----------------------------------------------------------------|--------|----------------------------------------------|-------------------------------------------------|------|--------------------------|--------------------------|-------|

| Input Voltage Range                                            | VIN    |                                              |                                                 | 5.5  |                          | 26                       | V     |

| Linear-Regulator Output<br>Voltage, V <sub>IN</sub> Referenced | Vldoh  | $V_{IN} = 5.5V$ to 26V, IL                   | $V_{IN} = 5.5V$ to 26V, $I_{LOAD} = 0$ to 20mA  |      | V <sub>IN</sub> -<br>5.0 | V <sub>IN</sub> -<br>4.5 | V     |

| Linear-Regulator Output<br>Voltage, Ground Referenced          | VLDOL  | $V_{IN} = 5.5V$ to 26V, IL                   | <sub>OAD</sub> = 0 to 20mA                      | 4.5  | 5.0                      | 5.5                      | V     |

| Full-Scale Current-Sense                                       |        | MAX1640                                      | MAX1640                                         |      | 150                      | 158                      | mV    |

| Threshold                                                      |        | MAX1641                                      |                                                 | 147  | 150                      | 153                      |       |

| Quarter-Scale Current-Sense                                    |        | MAX1640                                      |                                                 | 36   | 42                       | 48                       | mV    |

| Threshold                                                      |        | MAX1641                                      |                                                 | 34   | 37.5                     | 41                       |       |

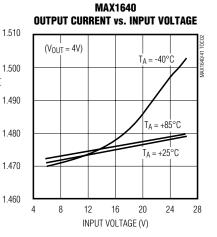

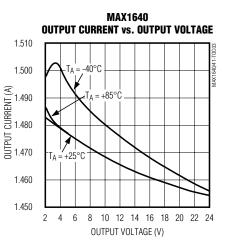

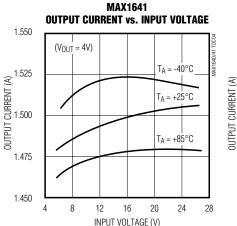

| Current-Sense Line Regulation                                  |        | $V_{IN} = V_{OUT} + 0.5V tc$                 | 26V                                             |      | 0.03                     |                          | %/V   |

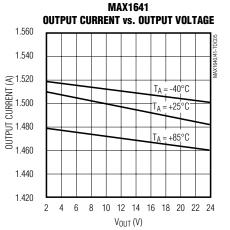

| Output Current Compliance                                      |        | Vout = 2V to 24V                             | MAX1640                                         |      | 0.1                      | 0.4                      | %/V   |

|                                                                |        | VOUT = 2V to 24V                             | MAX1641                                         |      | 0.1                      |                          | 70/V  |

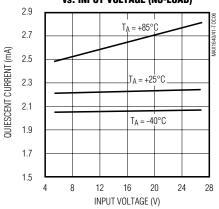

| Quiacoant Viu Supply Current                                   |        | D0 or D1 = high                              |                                                 |      | 2                        | 4                        | mA    |

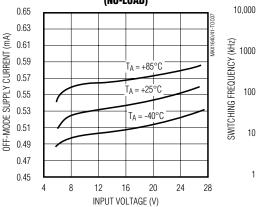

| Quiescent VIN Supply Current                                   |        | D0 = D1 = low (off mode)                     |                                                 |      | 500                      |                          | μA    |

| Output Current in Off Mode                                     |        | D0 = D1 = low                                |                                                 |      |                          | 1                        | μA    |

| V <sub>LDOL</sub> Undervoltage Lockout                         |        |                                              |                                                 | 4.05 | 4.20                     | 4.35                     | V     |

| Reference Voltage                                              | VREF   |                                              |                                                 | 1.96 | 2.00                     | 2.04                     | V     |

| Reference Load Regulation                                      |        | $I_{REF} = 0$ to $50\mu A$                   |                                                 |      | 4                        | 10                       | mV    |

| V <sub>SET</sub> Input Current                                 |        |                                              |                                                 |      |                          | 1                        | μA    |

| FET Drive Output Resistance                                    |        | PFET and NFET drive                          | 9                                               |      |                          | 12                       | Ω     |

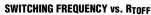

| Off-Time Range                                                 |        |                                              |                                                 | 1    |                          | 10                       | μs    |

| Off-Time Accuracy                                              |        | $R_{TOFF} = 62k\Omega$                       |                                                 | 1.7  | 2.2                      | 2.7                      | μs    |

| Pulse-Trickle Mode Duty-Cycle<br>Period                        |        | D0 = low, D1 = high, $R_{TOFF} = 100k\Omega$ |                                                 | 27   | 33                       | 40                       | ms    |

| Pulse-Trickle Mode Duty Cycle<br>(Note 2)                      |        | D0 = low, D1 = high,                         | D0 = low, D1 = high, $R_{TOFF}$ = 100k $\Omega$ |      | 12.5                     |                          | %     |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = +12V, V_{OUT} = 6V, Circuit of Figure 1, T_A = 0^{\circ}C to +85^{\circ}C, unless otherwise noted. Typical values are at T_A = +25^{\circ}C.)$

| PARAMETER              | SYMBOL | CONDITIONS | MIN | ТҮР | МАХ | UNITS |

|------------------------|--------|------------|-----|-----|-----|-------|

| PWM Maximum Duty Cycle |        |            | 100 |     |     | %     |

| Input Low Voltage      | VIL    | D0, D1     |     |     | 0.8 | V     |

| Input High Voltage     | VIH    | D0, D1     | 2.4 |     |     | V     |

| Input Leakage Current  | lin    | D0, D1     |     |     | ±1  | μA    |

## **ELECTRICAL CHARACTERISTICS**

(V<sub>IN</sub> = +12V, V<sub>OUT</sub> = 6V, Circuit of Figure 1,  $T_A$  = -40°C to +85°C, unless otherwise noted.)

| PARAMETER                                                      | SYMBOL | CONDITIONS                                               | MIN                      | ТҮР | MAX                      | UNITS |

|----------------------------------------------------------------|--------|----------------------------------------------------------|--------------------------|-----|--------------------------|-------|

| Input Voltage Range                                            | VIN    |                                                          | 5.5                      |     | 26                       | V     |

| Linear-Regulator Output<br>Voltage, V <sub>IN</sub> Referenced | VLDOH  | $V_{IN} = 5.5V$ to 26V,<br>I <sub>LOAD</sub> = 0 to 20mA | V <sub>IN</sub> -<br>5.5 |     | V <sub>IN</sub> -<br>4.5 | V     |

| Linear-Regulator Output<br>Voltage, Ground Referenced          | VLDOL  | $V_{IN} = 5.5V$ to 26V,<br>$I_{LOAD} = 0$ to 20mA        | 4.5                      |     | 5.5                      | V     |

| Full-Scale Current-Sense                                       |        | MAX1640                                                  | 141                      |     | 159                      | mV    |

| Threshold                                                      |        | MAX1641                                                  | 146                      |     | 154                      |       |

| Quarter-Scale Current-Sense                                    |        | MAX1640                                                  | 34                       |     | 48                       | mV    |

| Threshold                                                      |        | MAX1641                                                  | 33                       |     | 42                       |       |

| Output Current Compliance                                      |        | V <sub>OUT</sub> = 2V to 24V (MAX1640)                   |                          |     | 0.4                      | %/V   |

| Quiescent VIN Supply Current                                   |        | D0 or D1 = high                                          |                          |     | 4                        | mA    |

| Output Current in Off Mode                                     |        | D0 = D1 = low                                            |                          |     | 1                        | μA    |

| V <sub>LDOL</sub> Undervoltage Lockout                         |        |                                                          | 4.0                      |     | 4.4                      | V     |

| Reference Voltage                                              | VREF   |                                                          | 1.94                     |     | 2.06                     | V     |

| Reference Load Regulation                                      |        | I <sub>REF</sub> = 0 to 50µA                             |                          |     | 10                       | mV    |

| V <sub>SET</sub> Input Current                                 |        |                                                          |                          |     | 1                        | μA    |

| FET Drive Output Resistance                                    |        |                                                          |                          |     | 12                       | Ω     |

| Off-Time Range                                                 |        |                                                          | 1.5                      |     | 8                        | μs    |

| Off-Time Accuracy                                              |        | $R_{TOFF} = 62k\Omega$                                   | 1.5                      |     | 2.5                      | μs    |

| Pulse-Trickle Mode Duty-Cycle<br>Period                        |        | D0 = low, D1 = high, RTOFF = $50k\Omega$                 | 25                       |     | 42                       | ms    |

| PWM Maximum Duty Cycle                                         |        |                                                          | 100                      |     |                          | %     |

| Input Low Voltage                                              | VIL    | D0, D1                                                   |                          |     | 0.8                      | V     |

| Input High Voltage                                             | VIH    | D0, D1                                                   | 2.4                      |     |                          | V     |

| Input Leakage Current                                          | lin    | D0, D1                                                   |                          |     | ±1                       | μA    |

Note 2: This ratio is generated by a 1:8 clock divider and is not an error source for current calculations.

(Circuit of Figure 1,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

## **Typical Operating Characteristics**

QUIESCENT CURRENT vs. INPUT VOLTAGE (NO-LOAD)

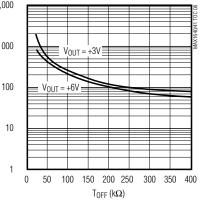

OFF-MODE SUPPLY CURRENT (NO-LOAD)

LINE-TRANSIENT RESPONSE

Maxim Integrated

## **Typical Operating Characteristics (continued)**

(Circuit of Figure 1,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

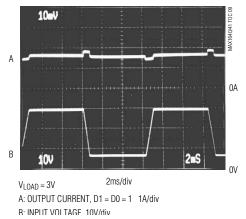

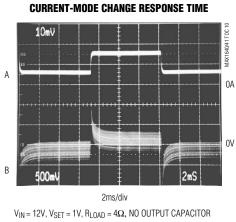

$v_{IN} = 12v$ ,  $v_{SET} = 1V$ ,  $R_{LOAD} = 452$ , NO UDIPUT CAP/ A: OUTPUT CURRENT, D0 = D1 = 0 1A/div B: LOAD VOLTAGE, AC coupled, 500mV/div

B: OUTPUT CURRENT, 0.5A/div

## Pin Description

| PIN  | NAME   | FUNCTION                                                                                                                                                                                                                                                                           |

|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | LDOL   | Internal, Ground-Referenced Low-Dropout Linear Regulator Output.<br>Bypass LDOL with a 0.1µF capacitor in parallel with a 4.7µF capacitor to GND.                                                                                                                                  |

| 2    | TOFF   | Off-Time Select Input. A resistor (R <sub>TOFF</sub> ) connected from TOFF to GND programs the off-time for the hys-<br>teretic PWM step-down converter. This resistor also sets the period in duty-cycle mode. See <i>Duty-Cycle</i><br><i>Mode and Programming the Off-Time.</i> |

| 3, 4 | D1, D0 | Digital Inputs. Select mode of operation (Table 1).                                                                                                                                                                                                                                |

| 5    | CC     | Constant-Current Loop Compensation Input. Bypass CC with a 0.01µF capacitor to GND.                                                                                                                                                                                                |

| 6    | REF    | Reference Voltage Output ( $V_{REF} = 2V$ ). Bypass REF with a 0.1µF capacitor to GND.                                                                                                                                                                                             |

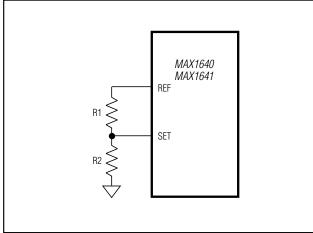

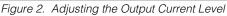

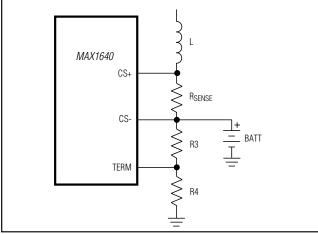

| 7    | SET    | Current Select Input. Program the desired current level by applying a voltage at SET between 0V and $V_{REF}$ , (I = $V_{SET}$ / 13.3 $R_{SENSE}$ ). See Figure 2.                                                                                                                 |

| 8    | TERM   | Maximum Output Voltage Termination Input. When V <sub>TERM</sub> exceeds the reference voltage, the comparator resets the internal PWM latch, shutting off the external P-channel FET.                                                                                             |

| 9    | GND    | Ground                                                                                                                                                                                                                                                                             |

| 10   | CS-    | Negative Current-Sense Comparator Input                                                                                                                                                                                                                                            |

| 11   | CS+    | Positive Current-Sense Comparator Input                                                                                                                                                                                                                                            |

| 12   | PGND   | High-Current Ground Return for the output drivers                                                                                                                                                                                                                                  |

| 13   | NDRV   | Gate Drive for an optional N-channel FET synchronous rectifier                                                                                                                                                                                                                     |

| 14   | PDRV   | Gate Drive for the P-channel FET                                                                                                                                                                                                                                                   |

| 15   | LDOH   | Internal, Input-Referenced Low-Dropout Linear Regulator Output. Bypass LDOH with a 0.33 $\mu\text{F}$ capacitor to IN.                                                                                                                                                             |

| 16   | IN     | Power-Supply Input. Input of the internal, low-dropout linear regulators.                                                                                                                                                                                                          |

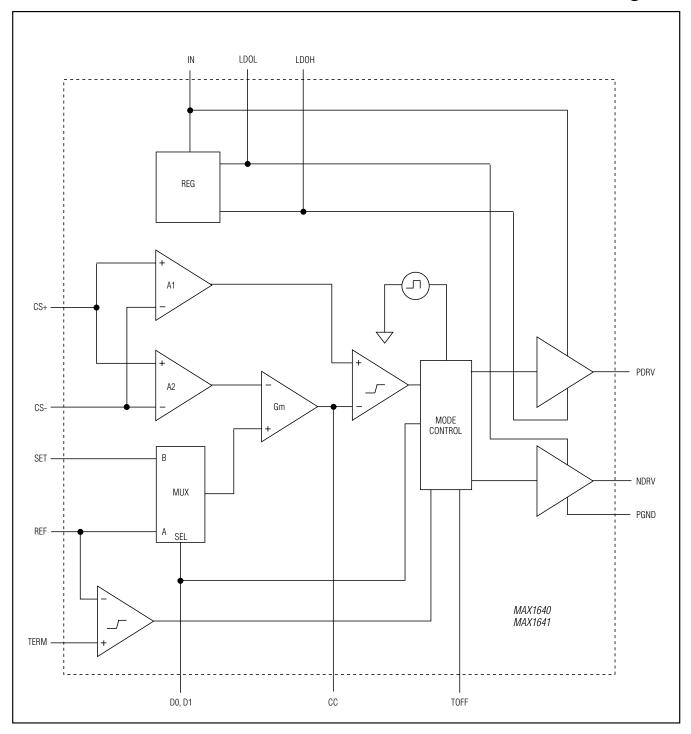

**Functional Diagram**

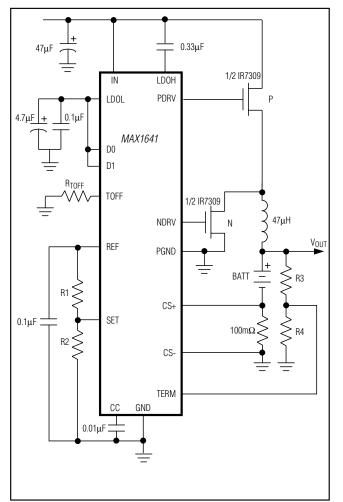

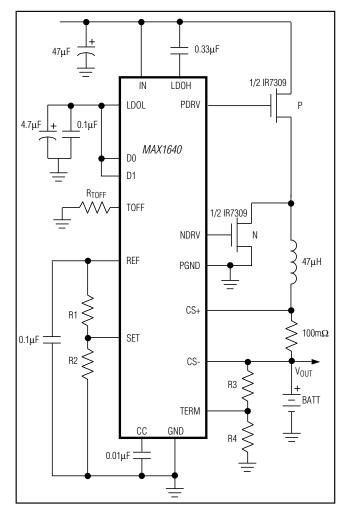

Figure 1a. Standard Application Circuit

## **Detailed Description**

The MAX1640/MAX1641 switch-mode current sources utilize a hysteretic, current-mode, step-down pulse-width-modulation (PWM) topology with constant off-time. Internal comparators control the switching mechanism. These comparators monitor the current through a sense resistor (R<sub>SENSE</sub>) and the voltage at TERM. When inductor current reaches the current limit [(VCS+ - VCS-) / RSENSE], the P-channel FET turns off and the N-channel FET synchronous rectifier turns on. Inductor energy is delivered to the load as the current ramps down. This ramp rate depends on R<sub>TOFF</sub> and inductor values. When off-time expires, the P-channel FET turns off.

Two digital inputs, D0 and D1, select between four possible current levels (Table 1). In pulse-trickle mode, the

Figure 1b. Standard Application Circuit

part operates for 12.5% of the period set by R<sub>TOFF</sub>, resulting in a lower current for pulse-trickle charging. See the *Functional Diagram*. Figures 1a and 1b show the standard application circuits.

### Charge Mode: Programming the Output Currents

The sense resistor, RSENSE, sets two charging current levels. Choose between these two levels by holding D0 high, and toggling D1 either high or low (Table 1). The fast-charge current level equals VCS / RSENSE where V<sub>CS</sub> is the full-scale current-sense voltage of 150mV. Alternatively, calculate this current by V<sub>REF</sub> / (13.3RSENSE). The top-off current equals V<sub>SET</sub> / (13.3RSENSE). A resistor-divider from REF to GND programs the voltage at SET (Figure 2).

The voltage at SET is given by:

R1 = R2 (V<sub>REF</sub> / V<sub>SET</sub> -1 );  $10k\Omega < R2 < 300k\Omega$

where  $V_{\text{REF}} = 2V$  and  $V_{\text{SET}}$  is proportional to the desired output current level.

Table 1. Selecting Output Current Levels

| D1 | DO | MODE          | OUTPUT CURRENT (A)                                               |

|----|----|---------------|------------------------------------------------------------------|

| 0  | 0  | OFF           | 0                                                                |

| 0  | 1  | Top-Off       | V <sub>SET</sub> / (13.3R <sub>SENSE</sub> )                     |

| 1  | 0  | Pulse-Trickle | V <sub>SET</sub> / (13.3R <sub>SENSE</sub> )<br>12.5% duty cycle |

| 1  | 1  | Fast Charge   | V <sub>REF</sub> / (13.3R <sub>SENSE</sub> )                     |

Figure 3a. Setting the Maximum Output Voltage Level

Figure 3b. Setting the Maximum Output Voltage Level

The MAX1640/MAX1641 are specified for VSET between 0V and VREF. For VSET > VREF, output current increases linearly (with reduced accuracy) until it clamps at VSET  $\approx$  4V.

### Pulse-Trickle Mode: Selecting the Pulse-Trickle Current

Pulling D0 low and D1 high selects pulse-trickle mode. This current equals  $V_{SET}$  / (13.3R<sub>SENSE</sub>) and remains on for 12.5% of the period set by R<sub>TOFF</sub>. Pulse-trickle current maintains full charge across the battery and can slowly charge a cold battery before fast charging commences.

$$PERIOD = 3.2 \times 10^{-7} \times R_{TOFF}(sec)$$

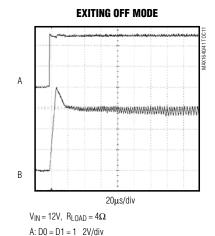

### **Off Mode: Turning Off the Output Current**

Pulling D0 and D1 low turns off the P-channel FET and hence the output current flow. This mode also controls end of charge and protects the battery against excessive temperatures.

### Setting the Maximum Output Voltage Level

The maximum output voltage should be programmed to a level higher than the output/battery voltage ( $I_{LOAD} \times R_{LOAD}$ ). An external resistor-divider between the output and ground (Figure 3) sets the voltage at TERM. Once the voltage at TERM exceeds the reference, the internal comparator turns off the P-channel FET, terminating current flow. Select R4 in the 10k $\Omega$  to 500k $\Omega$  range. R3 is given by:

where  $V_{\text{TERM}} = 2V$  and  $V_{\text{OUT}}$  is the desired output voltage.

### **Programming the Off-Time**

When programming the off-time, consider such factors as maximum inductor current ripple, maximum output voltage, inductor value, and inductor current rating. The output current ripple is less than the inductor current ripple and depends heavily on the output capacitor's size.

Perform the following steps to program the off-time:

- 1) Select the maximum output current ripple. I<sub>R</sub>(A)

- 2) Select the maximum output voltage. VOUT(MAX)(V)

- 3) Calculate the inductor value range as follows:

$L_{MIN} = (V_{OUTMAX} \times 1\mu s) / I_{R}$

$L_{MAX} = (V_{OUTMAX} \times 10 \mu s) / I_{R}$

- 4) Select an inductor value in this range.

- 5) Calculate tOFF as follows:

$$t_{OFF} = \frac{L \times I_R}{V_{OUTMAX}}$$

6) Program tOFF by selecting RTOFF from:

$R_{TOFF} = (29.3 \times 10^9) \times t_{OFF}$

7) Calculate the switching frequency by:

$$fs = 1 / (t_{ON} + t_{OFF})$$

where  $t_{ON} = (I_R \times L) / (V_{IN} - V_{OUT})$  and  $I_R = (V_{OUT} \times t_{OFF}) / L$ . L is the inductor value,  $V_{IN}$  is the input voltage,  $V_{OUT}$  is the output voltage, and  $I_R$  is the output peak-to-peak current ripple.

Note that R<sub>TOFF</sub> sets both the off-time and the pulse-trickle charge period.

### Reference

The on-chip reference is laser trimmed for a precise 2V at REF. REF can source no more than  $50\mu$ A. Bypass REF with a  $0.1\mu$ F capacitor to ground.

#### Constant-Current Loop: AC Loop Compensation

The constant-current loop's output is brought out at CC. To reduce noise due to variations in switching currents, bypass CC with a 1nF to 100nF capacitor to ground. A large capacitor value maintains a constant average output current but slows the loop response to changes in switching current. A small capacitor value speeds up the loop response to changes in switching current, generating increased ripple at the output. Select C<sub>CC</sub> to optimize the ripple vs. loop response.

### Synchronous Rectification

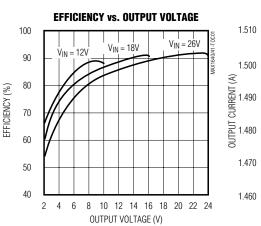

Synchronous rectification reduces conduction losses in the rectifier by shunting the Schottky diode with a lowresistance MOSFET switch. In turn, efficiency increases by about 3% to 5% at heavy loads. To prevent crossconduction or "shoot-through," the synchronous rectifier turns on shortly after the P-channel power MOSFET

| COMPONENT       | MANUFACTURER            |                  |  |  |  |  |

|-----------------|-------------------------|------------------|--|--|--|--|

|                 | Sumida                  | CDRH125 series   |  |  |  |  |

| Inductor        | Coilcraft               | D03316P series   |  |  |  |  |

|                 | Coiltronics             | UP2 series       |  |  |  |  |

| MOSFETs         | International Rectifier | IRF7309          |  |  |  |  |

|                 | Siliconix               | S14539DY         |  |  |  |  |

| Sense Resistor  | Dale                    | WSL-2010 series  |  |  |  |  |

| Serise nesision | IRC                     | LR2010-01 series |  |  |  |  |

| Capacitors      | AVX                     | TPS series       |  |  |  |  |

| Capacitors      | Sprague                 | 595D series      |  |  |  |  |

|                 | Motorola                | MBAR5340t3       |  |  |  |  |

| Rectifier       | MOLOI DIA               | IN5817-IN5822    |  |  |  |  |

|                 | Nihon                   | NSQ03A04         |  |  |  |  |

turns off. The synchronous rectifier remains off for 90% of the off-time. In low-cost designs, the synchronous rectifier FET may be replaced by a Schottky diode.

### **Component Selection**

### **External Switching Transistors**

The MAX1640/MAX1641 drive an enhancement-mode P-channel MOSFET and a synchronous-rectifier N-channel MOSFET (Table 2).

When selecting a P-channel FET, some important parameters to consider are on-resistance ( $r_{DS(ON)}$ ), maximum drain-to-source voltage ( $V_{DS}$  max), maximum gate-to-source voltage ( $V_{GS}$  max), and minimum threshold voltage ( $V_{TH}$  min).

In high-current applications, MOSFET package power dissipation often becomes a dominant design factor. I<sup>2</sup>R power losses are the greatest heat contributor for both high-side and low-side MOSFETs. Switching losses affect the upper MOSFET only (P-channel), since the Schottky rectifier or the N-FET body diode clamps the switching node before the synchronous rectifier turns on.

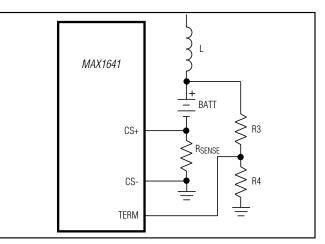

Figure 4. Microcontroller Battery Charger

#### **Rectifier Diode**

If an N-channel MOSFET synchronous rectifier is not used, a Schottky rectifier is needed. The MAX1640/ MAX1641's high switching frequency demands a highspeed rectifier (Table 2). Schottky diodes such as the 1N5817-1N5822 are recommended. Make sure the Schottky diode's average current rating exceeds the peak current limit and that its breakdown voltage exceeds the output voltage (VOUT). For high-temperature applications, Schottky diodes may be inadequate due to their high leakage current; high-speed silicon diodes such as the MUR105 or EC11FS1 can be used instead. At heavy loads and high temperatures, the benefits of a Schottky diode's low forward voltage may outweigh the disadvantage of high leakage current. If the application uses an N-channel MOSFET synchronous rectifier, a parallel Schottky diode is usually unnecessary except with very high charge current (> 3 amps). Best efficiency is achieved with both an N-channel MOSFET and a Schottky diode.

#### Inductor Value

Refer to the section *Programming the Off-Time* to select the proper inductor value. There is a trade-off between inductor value, off-time, output current ripple, and switching frequency.

### **Applications Information**

### All-Purpose Microcontroller Battery Charger: NiCd, NiMH

In applications where a microcontroller is available, the MAX1640/MAX1641 can be used as a low-cost battery charger (Figure 4). The controller takes over fast charge, pulse-trickle charge, charge termination, and other smart functions. By monitoring the output voltage at V<sub>OUT</sub>, the controller initiates fast charge (set D0 and D1 high), terminates fast charge and initiates top-off (set D0 high and D1 low), enters trickle charge (set D0 low and D1 high), or shuts off and terminates current flow (set D0 and D1 low).

### Layout and Grounding

Due to high current levels and fast switching waveforms, proper PC board layout is essential. High-current ground paths should be connected in a star configuration to PGND. These traces should be wide to reduce resistance and as short as possible to reduce stray inductance. All low-current ground paths should be connected to GND. Place the input bypass capacitor as close as possible to IN. See the MAX1640 EV kit for layout example.

### **Chip Information**

PROCESS: BICMOS

## **Package Information**

(For the latest package outline information and land patterns, go to www.maxim-ic.com/packages. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |  |

|--------------|--------------|----------------|--|

| 16 QSOP      | E16+1        | <u>21-0055</u> |  |

## **Revision History**

| REVISION | REVISION | DESCRIPTION                                                                                                                          | PAGES       |

|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------|-------------|

| NUMBER   | DATE     |                                                                                                                                      | CHANGED     |

| 2        | 5/09     | Added lead-free package to <i>Ordering Information</i> , corrected R3 equation, updated <i>Pin Description</i> and figure references | 1–8, 10, 11 |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

Maxim Integrated 160 Rio Robles, San Jose, CA 95134 USA 1-408-601-1000

© 2009 Maxim Integrated

The Maxim logo and Maxim Integrated are trademarks of Maxim Integrated Products, Inc.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated:

MAX1640EEE+ MAX1640EEE+T MAX1641EEE+ MAX1641EEE+T MAX1640EEE MAX1640EEE-T