# High-Output-Drive, 10MHz, 10V/µs, Rail-to-Rail I/O Op Amps with Shutdown in SC70

### **Absolute Maximum Ratings**

| C |

|---|

| J |

| S |

| L |

|   |

| S |

|   |

| 8-Pin µMAX <sup>®</sup> (derate 4.8mW/°C above +70°C)387.8mW |  |

|--------------------------------------------------------------|--|

| 10-Pin µMAX (derate 8.8mW/°C above +70°C)707.3mW             |  |

| 10-Bump UCSP (derate 5.6mW/°C above +70°C)448.7mW            |  |

| 14-Pin SO (derate 11.9mW/°C above +70°C)952.4mW              |  |

| 14-Pin TSSOP (derate 10mW/°C above +70°C)796.8mW             |  |

| Operating Temperature Range40°C to +125°C                    |  |

| Junction Temperature+150°C                                   |  |

| Storage Temperature Range65°C to +150°C                      |  |

| Lead Temperature                                             |  |

| (excluding 6 and 10 UCSP, soldering, 10s)+300°C              |  |

| Soldering Temperature (reflow)+260°C                         |  |

|                                                              |  |

$\mu$ MAX is a registered trademark of Maxim Integrated Products, Inc.

Note 1: Package power dissipation should also be observed.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **DC Electrical Characteristics**

$(V_{DD} = 2.7V, V_{SS} = 0V, V_{CM} = V_{DD/2}, V_{OUT} = (V_{DD/2}), R_L = \infty$  connected to  $(V_{DD/2}), V_{\overline{SHDN}} = V_{DD}, T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                          | SYMBOL                  | COND                                                | MIN                               | TYP             | MAX  | UNITS           |           |

|------------------------------------|-------------------------|-----------------------------------------------------|-----------------------------------|-----------------|------|-----------------|-----------|

| Operating Supply Voltage<br>Range  | V <sub>DD</sub>         | Inferred from PSRF                                  | Rtest                             | 2.7             |      | 5.5             | V         |

| Input Offset Voltage               | V <sub>OS</sub>         |                                                     |                                   |                 | 0.85 | ±6              | mV        |

| Input Bias Current (Note 4)        | I <sub>B</sub>          | $V_{CM} = V_{SS}$ to $V_{DD}$                       |                                   |                 |      | 1               | pА        |

| Input Offset Current               | I <sub>OS</sub>         | $V_{CM} = V_{SS}$ to $V_{DD}$                       |                                   |                 | 50   |                 | pА        |

| Input Resistance                   | R <sub>IN</sub>         |                                                     |                                   |                 | 1000 |                 | MΩ        |

| Common-Mode Input<br>Voltage Range | V <sub>CM</sub>         | Inferred from CMR                                   | R test                            | V <sub>SS</sub> |      | V <sub>DD</sub> | V         |

| Common-Mode Rejection<br>Ratio     | CMRR                    | V <sub>SS</sub> < V <sub>CM</sub> < V <sub>DD</sub> | 52                                | 70              |      | dB              |           |

| Power-Supply Rejection<br>Ratio    | PSRR                    | V <sub>DD</sub> = 2.7V to 5.5V                      | 73                                | 85              |      | dB              |           |

| Shutdown Output<br>Impedance       | R <sub>OUT</sub>        | V <sub>SHDN</sub> = 0V (Note                        | 3)                                |                 | 10   |                 | Ω         |

| Output Voltage in Shutdown         | V <sub>OUT</sub> (SHDN) | $V_{\overline{SHDN}} = 0V, R_L =$                   | 200Ω (Note 3)                     |                 | 68   |                 | mV        |

|                                    |                         | V <sub>SS</sub> + 0.20V <                           | R <sub>L</sub> = 100kΩ            |                 | 100  |                 |           |

| Large-Signal Voltage Gain          | A <sub>VOL</sub>        | $V_{OUT} < V_{DD}$ -                                | $R_L = 2k\Omega$                  | 85              | 98   |                 | dB        |

|                                    |                         | 0.20V                                               | R <sub>L</sub> = 200Ω             | 74              | 80   |                 |           |

|                                    |                         | R <sub>L</sub> = 32Ω                                | V <sub>DD</sub> - V <sub>OH</sub> |                 | 400  | 500             |           |

|                                    |                         | RL - 3202                                           | V <sub>OL</sub> - V <sub>SS</sub> |                 | 360  | 500             |           |

| Output Voltage Swing               | Vour                    | R <sub>L</sub> = 200Ω                               | V <sub>DD</sub> - V <sub>OH</sub> |                 | 80   | 120             | mV        |

| Sulput voltage Swilly              | Vout                    |                                                     | V <sub>OL</sub> - V <sub>SS</sub> |                 | 70   | 120             | - mv<br>- |

|                                    |                         | $R_{I} = 2k\Omega$                                  | V <sub>DD</sub> - V <sub>OH</sub> |                 | 8    | 14              |           |

|                                    |                         |                                                     | V <sub>OL</sub> - V <sub>SS</sub> |                 | 7    | 14              |           |

# High-Output-Drive, 10MHz, 10V/µs, Rail-to-Rail I/O Op Amps with Shutdown in SC70

### **DC Electrical Characteristics (continued)**

$(V_{DD} = 2.7V, V_{SS} = 0V, V_{CM} = V_{DD/2}, V_{OUT} = (V_{DD/2}), R_L = \infty$  connected to  $(V_{DD/2}), V_{\overline{SHDN}} = V_{DD}, T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                | SYMBOL          | CONDITIONS                         |                                                  |                                   | MIN                                 | TYP | MAX | UNITS |    |

|--------------------------|-----------------|------------------------------------|--------------------------------------------------|-----------------------------------|-------------------------------------|-----|-----|-------|----|

| Output Source/Sink       |                 | V <sub>DD</sub> = 2.7V             | V <sub>DD</sub> = 2.7V, V <sub>IN</sub> = ±100mV |                                   |                                     | 70  |     | mA    |    |

| Current                  | IOUT            | V <sub>DD</sub> = 5V, \            | / <sub>IN</sub> = ±100                           | mV                                |                                     | 200 |     | IIIA  |    |

|                          |                 | I <sub>I</sub> = 10mA              | V <sub>DD</sub> =                                | V <sub>DD</sub> - V <sub>OH</sub> |                                     | 128 | 200 |       |    |

| Output Voltage           |                 |                                    | 2.7V                                             | V <sub>OL</sub> - V <sub>SS</sub> |                                     | 112 | 175 | m)/   |    |

| Output Voltage           |                 | I <sub>L</sub> = 30mA              | I <sub>L</sub> = 30mA V <sub>DD</sub> = 5\       |                                   | , V <sub>DD</sub> - V <sub>OH</sub> |     | 240 | 320   | mV |

|                          |                 |                                    |                                                  | V <sub>OL</sub> - V <sub>SS</sub> |                                     | 224 | 300 |       |    |

| Quiescent Supply Current | I               | V <sub>DD</sub> = 5.5V             | , v <sub>cm</sub> = v <sub>c</sub>               | <sub>DD</sub> /2                  |                                     | 1.2 | 2.3 | m۸    |    |

| (per Amplifier)          | dd <sup>l</sup> | V <sub>DD</sub> = 2.7V             | $V_{DD} = 2.7V, V_{CM} = V_{DD}/2$               |                                   |                                     | 1.1 | 2.0 | mA    |    |

| Shutdown Supply Current  |                 | V <sub>SHDN</sub> = 0 <sup>v</sup> | V,                                               | V <sub>DD</sub> = 5.5V            |                                     | 0.5 | 1   |       |    |

| (per Amplifier) (Note 3) | IDD(SHDN)       | $R_L = \infty$                     | Γ                                                | V <sub>DD</sub> = 2.7V            |                                     | 0.1 | 1   | μA    |    |

| SHDN Logic Threshold     | VIL             | Shutdown mode                      |                                                  |                                   |                                     |     | 0.8 | V     |    |

| (Note 3)                 | VIH             | Normal mode                        |                                                  |                                   | V <sub>DD</sub> x 0                 | .57 |     | v     |    |

| SHDN Input Bias Current  |                 | V <sub>SS</sub> < V <sub>SHI</sub> | $\overline{DN} < V_{DD}$ (                       | Note 3)                           |                                     | 50  |     | pА    |    |

#### **DC Electrical Characteristics**

$(V_{DD} = 2.7V, V_{SS} = 0V, V_{CM} = V_{DD/2}, V_{OUT} = (V_{DD/2}), R_L = \infty$  connected to  $(V_{DD/2}), V_{\overline{SHDN}} = V_{DD}, T_A = -40$  to +125°C, unless other wise noted.) (Note 2)

| PARAMETER                          | SYMBOL                     | CONE                                                | DITIONS                           | MIN             | TYP | MAX             | UNITS |  |

|------------------------------------|----------------------------|-----------------------------------------------------|-----------------------------------|-----------------|-----|-----------------|-------|--|

| Operating Supply Voltage<br>Range  | V <sub>DD</sub>            | Inferred from PSRI                                  | R test                            | 2.7             |     | 5.5             | V     |  |

| Input Offset Voltage               | V <sub>OS</sub>            |                                                     |                                   |                 |     | ±8              | mV    |  |

| Offset-Voltage Tempco              | $\Delta V_{OS} / \Delta T$ |                                                     |                                   |                 | ±3  |                 | µV/°C |  |

| Input Bias Current                 | IB                         | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}$      | °C                                |                 |     | 17              | pА    |  |

| (Note 4)                           | 'B                         | T <sub>A</sub> = -40°C to +125                      | 5°C                               |                 |     | 550             | μη    |  |

| Common-Mode Input Voltage<br>Range | V <sub>CM</sub>            | Inferred from CMRR test                             |                                   | V <sub>SS</sub> |     | V <sub>DD</sub> | V     |  |

| Common-Mode Rejection<br>Ratio     | CMRR                       | V <sub>SS</sub> < V <sub>CM</sub> < V <sub>DD</sub> |                                   | 46              |     |                 | dB    |  |

| Power-Supply Rejection Ratio       | PSRR                       | V <sub>DD</sub> = 2.7V to 5.5\                      | /                                 | 70              |     |                 | dB    |  |

| Output Voltage in Shutdown         | VOUT(SHDN)                 | $V_{\overline{SHDN}} = 0V, R_L =$                   | 200Ω (Note 3)                     |                 |     | 150             | mV    |  |

| Lorgo Signal Valtago Cain          |                            | V <sub>SS</sub> + 0.20V                             | $R_L = 2k\Omega$                  | 76              |     |                 | dB    |  |

| Large-Signal Voltage Gain          | A <sub>VOL</sub>           | < V <sub>DD</sub> - 0.20V                           | R <sub>L</sub> = 200Ω             | 67              |     |                 | uБ    |  |

|                                    |                            | R <sub>L</sub> = 32Ω                                | V <sub>DD</sub> - V <sub>OH</sub> |                 |     | 650             |       |  |

|                                    |                            | T <sub>A</sub> = +85°C                              | V <sub>OL</sub> - V <sub>SS</sub> |                 | -   | 650             |       |  |

| Output Voltage Swing               | N/                         | D = 2000                                            | V <sub>DD</sub> - V <sub>OH</sub> |                 |     | 150             | mV    |  |

| Output Voltage Swing               | V <sub>OUT</sub>           | R <sub>L</sub> = 200Ω                               | V <sub>OL</sub> - V <sub>SS</sub> |                 |     | 150             |       |  |

|                                    |                            | $R_{I} = 2k\Omega$                                  | V <sub>DD</sub> - V <sub>OH</sub> |                 |     | 20              |       |  |

|                                    |                            |                                                     | V <sub>OL</sub> - V <sub>SS</sub> |                 |     | 20              |       |  |

# High-Output-Drive, 10MHz, 10V/µs, Rail-to-Rail I/O Op Amps with Shutdown in SC70

### **DC Electrical Characteristics**

$(V_{DD} = 2.7V, V_{SS} = 0V, V_{CM} = V_{DD/2}, V_{OUT} = (V_{DD/2}), R_L = \infty$  connected to  $(V_{DD/2}), V_{\overline{SHDN}} = V_{DD}, T_A = -40$  to +125°C, unless other wise noted.) (Note 2)

| PARAMETER                | SYMBOL          | CONDITIONS                                               |                      |                                   | MIN                   | ΤΥΡ | MAX | UNITS |

|--------------------------|-----------------|----------------------------------------------------------|----------------------|-----------------------------------|-----------------------|-----|-----|-------|

|                          |                 | I <sub>I</sub> = 10mA                                    | V <sub>DD</sub> =    | V <sub>DD</sub> - V <sub>OH</sub> |                       |     | 250 |       |

|                          |                 |                                                          | 2.7V                 | V <sub>OL</sub> - V <sub>SS</sub> |                       |     | 230 |       |

| Output Voltage           |                 | I <sub>L</sub> = 30mA<br>T <sub>A</sub> = -40°C          | $V_{} = 5V_{}$       | V <sub>DD</sub> - V <sub>OH</sub> |                       |     | 400 | mV    |

|                          |                 | to +85°                                                  | V <sub>DD</sub> = 5V | V <sub>OL</sub> - V <sub>SS</sub> |                       |     | 370 |       |

| Quiescent Supply Current | I               | V <sub>DD</sub> = 5.5V,                                  | $V_{CM} = V_{DD}/2$  |                                   |                       |     | 2.8 | mA    |

| (per Amplifier)          | DD              | $V_{DD}$ = 2.7V, $V_{CM}$ = $V_{DD}/2$                   |                      |                                   |                       |     | 2.5 | IIIA  |

| Shutdown Supply Current  |                 |                                                          | D. <b>-</b> ~        | V <sub>DD</sub> = 5.5V            |                       |     | 2.0 |       |

| (per Amplifier) (Note 3) | IDD(SHDN)       | $V_{\overline{SHDN}} < 0V, R_L = \infty$ $V_{DD} = 2.7V$ |                      | V <sub>DD</sub> = 2.7V            |                       |     | 2.0 | μA    |

| SHDN Logic Threshold     | V <sub>IL</sub> | Shutdown mode                                            |                      |                                   |                       | 0.8 | V   |       |

| (Note 3)                 | V <sub>IH</sub> | Normal mode                                              | 9                    |                                   | V <sub>DD</sub> x 0.6 | 61  |     | V     |

### **AC Electrical Characteristics**

$(V_{DD} = 2.7V, V_{SS} = 0V, V_{CM} = V_{DD}/2, V_{OUT} = (V_{DD}/2), R_L = \infty$  connected to  $(V_{DD}/2), V_{\overline{SHDN}} = V_{DD}, T_A = +125^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                               | SYMBOL              | CONDITIONS                                                                   | MIN | TYP    | MAX | UNITS   |  |

|-----------------------------------------|---------------------|------------------------------------------------------------------------------|-----|--------|-----|---------|--|

| Gain-Bandwidth Product                  | GBWP                | $V_{CM} = V_{DD}/2$                                                          |     | 10     |     | MHz     |  |

| Full-Power Bandwidth                    | FPBW                | $V_{OUT} = 2V_{P-P}, V_{DD} = 5V$                                            |     | 0.8    |     | MHz     |  |

| Slew Rate                               | SR                  |                                                                              |     | 10     |     | V/µs    |  |

| Phase Margin                            | PM                  |                                                                              |     | 70     |     | Degrees |  |

| Gain Margin                             | GM                  |                                                                              |     | 15     |     | dB      |  |

| Total Harmonic Distortion<br>Plus Noise | THD+N               | f = 10kHz, V <sub>OUT</sub> = 2V <sub>P-P</sub> ,<br>A <sub>VCL</sub> = 1V/V |     | 0.0005 |     | %       |  |

| Input Capacitance                       | C <sub>IN</sub>     |                                                                              |     | 8      |     | pF      |  |

| Valtara Najao Danaitu                   |                     | f = 1kHz                                                                     |     | 15     |     | nV/√Hz  |  |

| Voltage-Noise Density                   | e <sub>n</sub>      | f = 10kHz                                                                    |     | 12     |     |         |  |

| Channel-to-Channel<br>Isolation         |                     | f = 1kHz, RL = 100kΩ                                                         |     | 125    |     | dB      |  |

| Capacitive-Load Stability               |                     | A <sub>VCL</sub> = 1V/V, no sustained oscillations                           |     | 780    |     | pF      |  |

| Shutdown Time                           | t <sub>SHDN</sub>   | (Note 3)                                                                     |     | 1      |     | μs      |  |

| Enable Time from<br>Shutdown            | t <sub>ENABLE</sub> | (Note 3)                                                                     |     | 6      |     | μs      |  |

| Power-Up Time                           | t <sub>ON</sub>     |                                                                              |     | 5      |     | μs      |  |

Note 2: All units 100% tested at +25°C. All temperature limits are guaranteed by design.

Note 3: SHDN logic parameters are for the MAX4231/MAX4233 only.

Note 4: Guaranteed by design.

# High-Output-Drive, 10MHz, 10V/µs, Rail-to-Rail I/O Op Amps with Shutdown in SC70

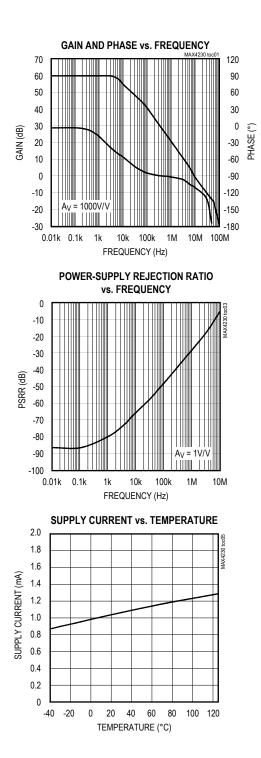

### **Typical Operating Characteristics**

(V<sub>DD</sub> = 2.7V, V<sub>SS</sub> = 0V, V<sub>CM</sub> = V<sub>DD</sub>/2, V<sub>OUT</sub> = V<sub>DD</sub>/2, R<sub>L</sub> = ∞, connected to V<sub>DD</sub>/2, V<sub>SHDN</sub> = V<sub>DD</sub>, T<sub>A</sub> = +25°C, unless otherwise noted.)

# High-Output-Drive, 10MHz, 10V/µs, Rail-to-Rail I/O Op Amps with Shutdown in SC70

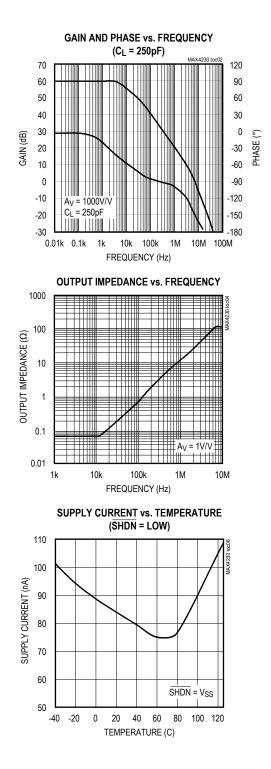

### **Typical Operating Characteristics (continued)**

$(V_{DD} = 2.7V, V_{SS} = 0V, V_{CM} = V_{DD}/2, V_{OUT} = V_{DD}/2, R_L = \infty$ , connected to  $V_{DD}/2, V_{SHDN} = V_{DD}, T_A = +25^{\circ}C$ , unless otherwise noted.)

# High-Output-Drive, 10MHz, 10V/µs, Rail-to-Rail I/O Op Amps with Shutdown in SC70

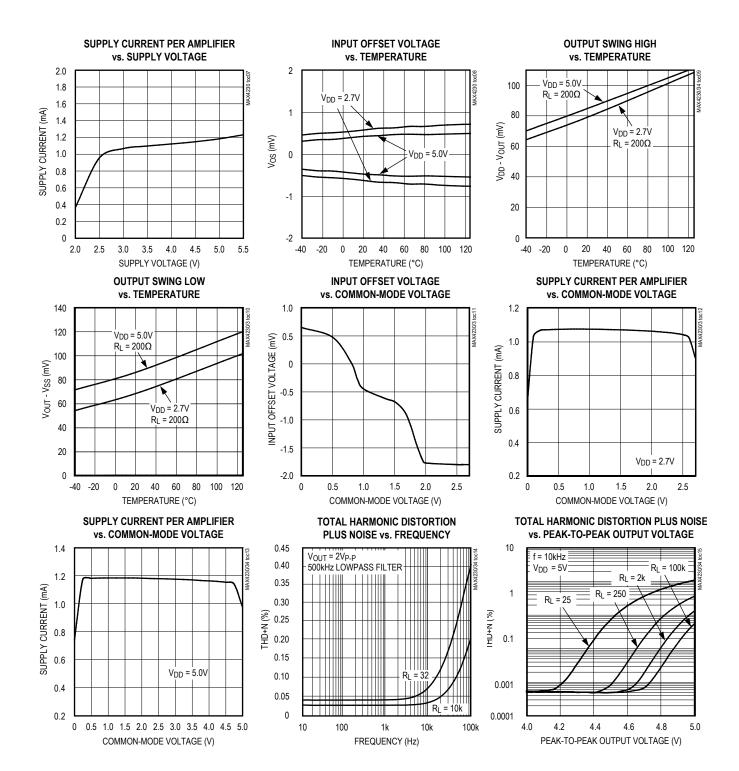

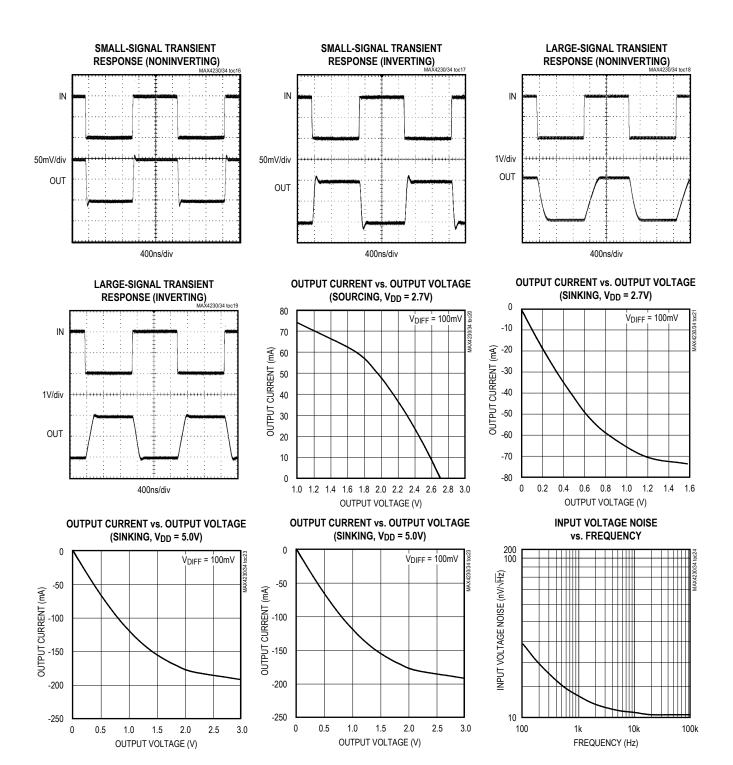

#### **Typical Operating Characteristics (continued)**

$(V_{DD} = 2.7V, V_{SS} = 0V, V_{CM} = V_{DD}/2, V_{OUT} = V_{DD}/2, R_L = \infty, \text{ connected to } V_{DD}/2, V_{\overline{SHDN}} = V_{DD}, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

# $\label{eq:High-Output-Drive, 10MHz, 10V/\mus, Rail-to-Rail I/O Op Amps with Shutdown in SC70$

### **Pin Description**

|                           |                                        | PIN                       |                 |                     | BU              | MP              |                          |                                                                              |

|---------------------------|----------------------------------------|---------------------------|-----------------|---------------------|-----------------|-----------------|--------------------------|------------------------------------------------------------------------------|

| MAX4230<br>SOT23/<br>SC70 | MAX4231<br>SOT23/<br>SC70/Thin<br>µDFN | MAX4232<br>SOT23/<br>μMAX | ΜΑΧ4233<br>μΜΑΧ | MAX4234<br>TSSOP/SO | MAX4231<br>UCSP | MAX4233<br>UCSP | NAME                     | FUNCTION                                                                     |

| 1                         | 1                                      | —                         | —               | _                   | B1              | —               | IN+                      | Noninverting Input                                                           |

| 2                         | 2                                      | 4                         | 4               | 11                  | A1              | B4              | Vss                      | Negative Supply Input.<br>Connect to ground for single-<br>supply operation. |

| 3                         | 3                                      | _                         | _               | _                   | B2              | _               | IN-                      | Inverting Input                                                              |

| 4                         | 4                                      | —                         | —               | —                   | A2              | —               | OUT                      | Amplifier Output                                                             |

| 5                         | 6                                      | 8                         | 10              | 4                   | A3              | B1              | VDD                      | Positive Supply Input                                                        |

| _                         | 5                                      | _                         | 5, 6            | _                   | В3              | C4, A4          | SHDN,<br>SHDN1,<br>SHDN2 | Shutdown Control. Tie to high for normal operation.                          |

| _                         | _                                      | 3                         | 3               | 3                   | _               | C3              | IN1+                     | Noninverting Input to Amplifier 1                                            |

| _                         | _                                      | 2                         | 2               | 2                   | —               | C2              | IN1-                     | Inverting Input to Amplifier 1                                               |

| —                         | _                                      | 1                         | 1               | 1                   | _               | C1              | OUT1                     | Amplifier 1 Output                                                           |

| —                         | —                                      | 5                         | 7               | 5                   | —               | A3              | IN2+                     | Noninverting Input to Amplifier 2                                            |

| _                         | _                                      | 6                         | 8               | 6                   | _               | A2              | IN2-                     | Inverting Input to Amplifier 2                                               |

| —                         | _                                      | 7                         | 9               | 7                   | _               | A1              | OUT2                     | Amplifier 2 Output                                                           |

|                           |                                        |                           |                 | 10, 12              |                 |                 | IN3+,<br>N4+             | Noninverting Input to Amplifiers 3                                           |

| _                         | —                                      | —                         | —               | 9, 13               | _               | _               | IN3-,<br>IN4-            | Inverting Input to Amplifiers 3 and                                          |

| _                         | _                                      | _                         | _               | 8, 14               | _               | _               | OUT3,<br>OUT4            | Amplifiers 3 and 4 Outputs                                                   |

#### **Detailed Description**

#### **Rail-to-Rail Input Stage**

The MAX4230–MAX4234 CMOS operational amplifiers have parallel-connected n- and p-channel differential input stages that combine to accept a common-mode range extending to both supply rails. The n-channel stage is active for common-mode input voltages typically greater than ( $V_{SS}$  + 1.2V), and the p-channel stage is active for common-mode input voltages typically less than ( $V_{DD}$  - 1.2V).

#### **Applications Information**

#### **Package Power Dissipation**

Warning: Due to the high output current drive, this op amp can exceed the absolute maximum powerdissipation rating. As a general rule, as long as the peak current is less than or equal to 40mA, the maximum package power dissipation is not exceeded for any of the package types offered. There are some exceptions to this rule, however. The absolute maximum power-dissipation rating of each package should always be verified using the following equations. The equation below gives an approximation of the package power dissipation:

$$P_{IC(DISS)} \cong V_{RMS} I_{RMS} COS\theta$$

where:

$V_{RMS}$  = RMS voltage from  $V_{DD}$  to  $V_{OUT}$  when sourcing current and RMS voltage from  $V_{OUT}$  to  $V_{SS}$  when sinking current.

$I_{RMS}$  = RMS current flowing out of or into the op amp and the load.

$\theta$  = phase difference between the voltage and the current. For resistive loads, COS  $\theta$  = 1.

# High-Output-Drive, 10MHz, 10V/µs, Rail-to-Rail I/O Op Amps with Shutdown in SC70

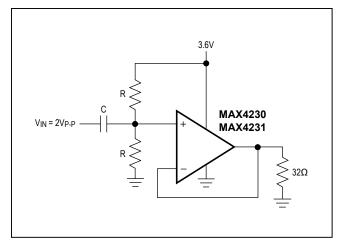

Figure 1. MAX4230/MAX4231 Used in Single-Supply Operation Circuit Example

For example, the circuit in Figure 1 has a package power dissipation of 196mW:

$$\begin{split} \text{RMS} &\cong (\text{V}_{DD} - \text{V}_{DC}) + \frac{\text{V}_{PEAK}}{\sqrt{2}} \\ &= 3.6\text{V} - 1.8\text{V} + \frac{1.0\text{V}}{\sqrt{2}} = 2.507\text{V}_{RMS} \\ \text{I}_{RMS} &\cong \text{I}_{DC} + \frac{\text{I}_{PEAK}}{\sqrt{2}} = \frac{1.8\text{V}}{32\Omega} + \frac{1.0\text{V}/32\Omega}{\sqrt{2}} \\ &= 78.4\text{mA}_{RMS} \end{split}$$

where:

$V_{DC}$  = the DC component of the output voltage.

$I_{DC}$  = the DC component of the output current.

$V_{PEAK}$  = the highest positive excursion of the AC component of the output voltage.

$I_{PEAK}$  = the highest positive excursion of the AC component of the output current.

Therefore:

$$P_{IC(DISS)} = V_{RMS} I_{RMS} COS \theta$$

= 196mW

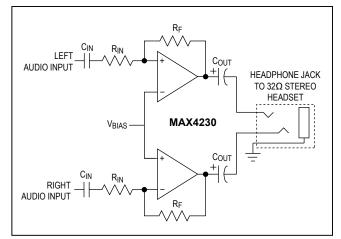

Adding a coupling capacitor improves the package power dissipation because there is no DC current to the load, as shown in Figure 2:

Figure 2. Circuit Example: Adding a Coupling Capacitor Greatly Reduces Power Dissipation of its Package

$$V_{RMS} \approx \frac{V_{PEAK}}{\sqrt{2}}$$

$$= \frac{1.0V}{\sqrt{2}} = 0.707 V_{RMS}$$

$$I_{RMS} \approx I_{DC} + \frac{I_{PEAK}}{\sqrt{2}} = 0A + \frac{1.0V / 32\Omega}{\sqrt{2}}$$

$$= 22.1 mA_{RMS}$$

Therefore:

$$P_{IC(DISS)} = V_{RMS} I_{RMS} COS \theta$$

= 15.6mW

If the configuration in <u>Figure 1</u> were used with all four of the MAX4234 amplifiers, the absolute maximum power dissipation rating of this package would be exceeded (see the *Absolute Maximum Ratings* section).

#### 60mW Single-Supply Stereo Headphone Driver

Two MAX4230/MAX4231s can be used as a single-supply, stereo headphone driver. The circuit shown in Figure 2 can deliver 60mW per channel with 1% distortion from a single 5V supply.

The input capacitor (C<sub>IN</sub>), in conjunction with R<sub>IN</sub>, forms a highpass filter that removes the DC bias from the incoming signal. The -3dB point of the highpass filter is given by

$$f_{-3dB} = \frac{1}{2\pi R_{IN}C_{IN}}$$

# High-Output-Drive, 10MHz, 10V/µs, Rail-to-Rail I/O Op Amps with Shutdown in SC70

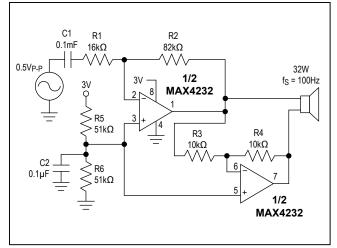

Figure 3. Dual MAX4230/MAX4231 Bridge Amplifier for 200mW at 3V

Choose gain-setting resistors  $R_{IN}$  and  $R_F$  according to the amount of desired gain, keeping in mind the maximum output amplitude. The output coupling capacitor,  $C_{OUT}$ , blocks the DC component of the amplifier output, preventing DC current flowing to the load. The output capacitor and the load impedance form a highpass filer with the -3dB point determined by:

$$f_{-3dB} = \frac{1}{2\pi R_{IN}C_{OUT}}$$

For a 32 load, a 100  $\mu F$  aluminum electrolytic capacitor gives a low-frequency pole at 50 Hz.

#### **Bridge Amplifier**

The circuit shown in Figure 3 uses a dual MAX4230 to implement a 3V, 200mW amplifier suitable for use in sizeconstrained applications. This configuration eliminates the need for the large coupling capacitor required by the single op-amp speaker driver when single-supply operation is necessary. Voltage gain is set to 10V/V; however, it can be changed by adjusting the 82k $\Omega$  resistor value.

#### **Rail-to-Rail Input Stage**

The MAX4230–MAX4234 CMOS op amps have parallel connected n- and p-channel differential input stages that combine to accept a common-mode range extending to both supply rails. The n-channel stage is active for common-mode input voltages typically greater than (V<sub>SS</sub> + 1.2V), and the p-channel stage is active for common-mode input voltages typically less than (V<sub>DD</sub> -1.2V).

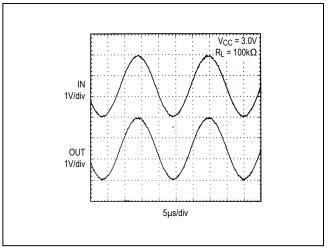

Figure 4. Rail-to-Rail Input/Output Range

#### **Rail-to-Rail Output Stage**

The minimum output is within millivolts of ground for single-supply operation, where the load is referenced to ground (V<sub>SS</sub>). Figure 4 shows the input voltage range and the output voltage swing of a MAX4230 connected as a voltage follower. The maximum output voltage swing is load dependent; however, it is guaranteed to be within 500mV of the positive rail (V<sub>DD</sub> = 2.7V) even with maximum load (32 $\Omega$  to ground).

Observe the <u>Absolute Maximum Ratings</u> for power dissipation and output short-circuit duration (10s, max) because the output current can exceed 200mA (see the <u>Typical Operating Characteristics.</u>)

#### Input Capacitance

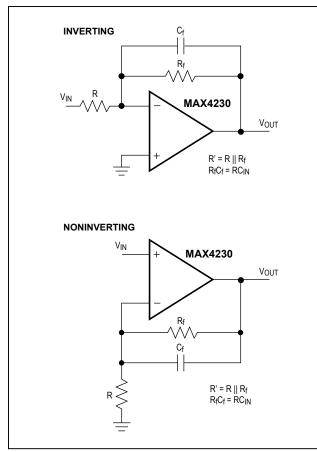

One consequence of the parallel-connected differential input stages for rail-to-rail operation is a relatively large input capacitance  $C_{IN}$  (5pF typ). This introduces a pole at frequency  $(2\pi R'C_{IN})^{-1}$ , where R' is the parallel combination of the gain-setting resistors for the inverting or noninverting amplifier configuration (Figure 5). If the pole frequency is less than or comparable to the unity-gain bandwidth (10MHz), the phase margin is reduced, and the amplifier exhibits degraded AC performance through either ringing in the step response or sustained oscillations. The pole frequency is 10MHz when R' = 2k\Omega. To maximize stability, R' << 2k\Omega is recommended.

# High-Output-Drive, 10MHz, 10V/µs, Rail-to-Rail I/O Op Amps with Shutdown in SC70

Figure 5. Inverting and Noninverting Amplifiers with Feedback Compensation

To improve step response when  $R' > 2k\Omega$ , connect small capacitor Cf between the inverting input and output. Choose Cf as follows:

$$C_{f} = 8(R/R_{f}) [pf]$$

where  $R_f$  is the feedback resistor and R is the gain-setting resistor (Figure 5).

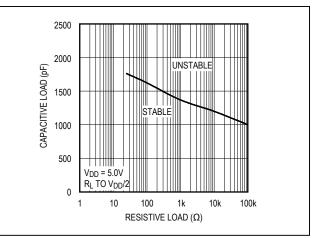

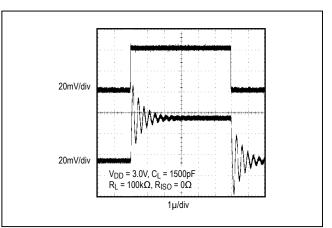

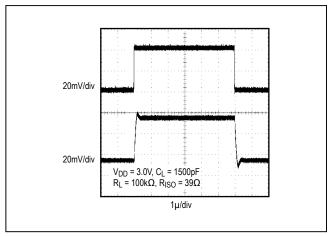

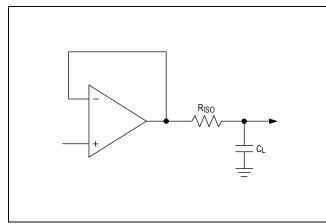

#### **Driving Capacitive Loads**

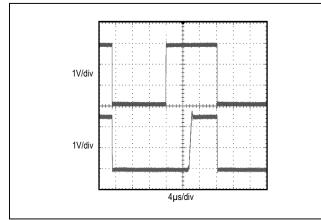

The MAX4230–MAX4234 have a high tolerance for capacitive loads. They are stable with capacitive loads up to 780pF. Figure 6 is a graph of the stable operating region for various capacitive loads vs. resistive loads.Figures 7 and 8 show the transient response with excessive capacitive loads (1500pF), with and without the addition of an isolation resistor in series with the output. Figure 9 shows a typical noninverting capacitive-load-driving circuit in the unity-gain configuration.

Figure 6. Capacitive-Load Stability

Figure 7. Small-Signal Transient Response with Excessive Capacitive Load

Figure 8. Small-Signal Transient Response with Excessive Capacitive Load with Isolation Resistor

# High-Output-Drive, 10MHz, 10V/µs, Rail-to-Rail I/O Op Amps with Shutdown in SC70

Figure 9. Capacitive-Load-Driving Circuit

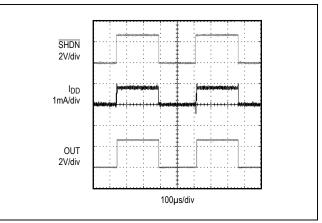

Figure 10. Shutdown Output Voltage Enable/Disable

The resistor improves the circuit's phase margin by isolating the load capacitor from the op amp's output.

#### **Power-Up and Shutdown Modes**

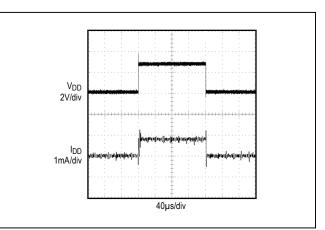

The MAX4231/MAX4233 have a shutdown option. When the shutdown pin (SHDN) is pulled low, supply current drops to 0.5µA per amplifier ( $V_{DD}$  = 2.7V), the amplifiers are disabled, and their outputs are driven to  $V_{SS}$ . Since the outputs are actively driven to  $V_{SS}$  in shutdown, any pullup resistor on the output causes a current drain from the supply. Pulling SHDN high enables the amplifier. In the dual MAX4233, the two amplifiers shut down independently. Figure 10 shows the MAX4231's output voltage to a shutdown pulse. The MAX4231–MAX4234 typically settle within 5µs after power-up. Figures 11 and 12 show IDD to a shutdown plus and voltage power-up cycle.

Figure 11. Shutdown Enable/Disable Supply Current

Figure 12. Power-Up/Down Supply Current

#### **Selector Guide**

| PART    | AMPS PER<br>PACKAGE | SHUTDOWN<br>MODE |

|---------|---------------------|------------------|

| MAX4230 | Single              | —                |

| MAX4231 | Single              | Yes              |

| MAX4232 | Dual                | —                |

| MAX4233 | Dual                | Yes              |

| MAX4234 | Quad                | —                |

When exiting shutdown, there is a  $6\mu$ s delay before the amplifier's output becomes active (Figure 10).

# High-Output-Drive, 10MHz, 10V/ $\mu$ s, Rail-to-Rail I/O Op Amps with Shutdown in SC70

#### TOP VIEW SHDN OUT Vdd 5 V<sub>DD</sub> OUT1 1 8 VDD IN+ 6 V<sub>DD</sub> 1 IN+ MAX4231 6 5 4 7 OUT2 IN1- 2 MAX4230 MAX4232 5 SHDN V<sub>SS</sub> 2 V<sub>SS</sub> 2 MAX4231 IN1+ 3 6 IN2-5 IN2+ Vss 4 IN- 3 4 OUT IN- 3 4 OUT 2 3 1 IN+ IN-VSS SOT23/MAX SOT23/SC70 SC70/SOT23 Thin µDFN (Ultra-Thin LGA) 2 3 2 3 4 14 OUT4 OUT1 OUT1 10 V<sub>DD</sub> | 1 (OUT) (OUT2) ( IN2-( IN2+ $V_{SS}$ $V_{DD}$ SHDN2 13 IN4-IN1- 2 9 OUT2 IN1- 2 MAX4233 IN1+ 3 12 IN4+ IN1+ 3 8 IN2-MAX4233 В $\mathsf{V}_{\mathsf{D}\mathsf{D}}$ 11 V<sub>SS</sub> 7 IN2+ MAX4234 V<sub>SS</sub> 4 MAX4231 VSS V<sub>DD</sub> 4 10 IN3+ SHDN1 5 6 SHDN2 IN2+ 5 9 IN3-IN2- 6 С (SHDN1 MAX В IN+ IN-(SHDN) (OUT1) IN1-( IN1+ OUT2 7 8 OUT3 UCSP UCSP TSSOP/SO

# **Pin/Bump Configurations**

#### **Power Supplies and Layout**

The MAX4230–MAX4234 can operate from a single 2.7V to 5.5V supply, or from dual  $\pm 1.35V$  to  $\pm 2.5V$  supplies. or single-supply operation, bypass the power supply with a 0.1µF ceramic capacitor. For dual-supply operation, bypass each supply to ground. Good layout improves performance by decreasing the amount of stray capacitance at the op amps' inputs and outputs. Decrease stray capacitance by placing external components close to the op amps' pins, minimizing trace and lead lengths.

### **Ordering Information (continued)**

| PART                 | TEMP<br>RANGE   | PIN-<br>PACKAGE | TOP<br>MARK |

|----------------------|-----------------|-----------------|-------------|

| <b>MAX4232</b> AKA+T | -40°C to +125°C | 8 SOT23         | AAKW        |

| MAX4232AUA+T         | -40°C to +125°C | 8 µMAX          | —           |

| MAX4233AUB+T         | -40°C to +125°C | 10 µMAX         | _           |

| MAX4233ABC+T         | -40°C to +125°C | 10 UCSP         | ABF         |

| MAX4234AUD           | -40°C to +125°C | 14 TSSOP        | —           |

| MAX4234AUD/V+        | -40°C to +125°C | 14 TSSOP        | +YWD        |

| MAX4234ASD           | -40°C to +125°C | 14 SO           | _           |

+Denotes a lead-free(Pb)/RoHS-compliant package.

T = Tape and reel.

/V denotes an automotive-qualified part.

\*EP = Exposed pad.

# High-Output-Drive, 10MHz, 10V/µs, Rail-to-Rail I/O Op Amps with Shutdown in SC70

### **Package Information**

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE                    | PACKAGE CODE | DOCUMENT NO.   | LAND PATTERN NO. |

|---------------------------------|--------------|----------------|------------------|

| 5 SC70                          | X5+1         | <u>21-0076</u> | <u>90-0188</u>   |

| 6 SC70                          | X6SN+1       | <u>21-0077</u> | <u>90-0189</u>   |

| 5 SOT23                         | U5+1         | <u>21-0057</u> | <u>90-0174</u>   |

| 6 SOT23                         | U6SN+1       | <u>21-0058</u> | <u>90-0175</u>   |

| 8 µMAX                          | U8+1         | <u>21-0036</u> | <u>90-0092</u>   |

| 8 SOT23                         | K8+5         | <u>21-0078</u> | <u>90-0176</u>   |

| 10 µMAX                         | U10+2        | <u>21-0061</u> | <u>90-0330</u>   |

| 10 UCSP                         | B12+4        | <u>21-0104</u> | —                |

| 6 UCSP                          | R61A1+1      | <u>21-0228</u> | _                |

| 6 Thin µDFN<br>(Ultra-Thin LGA) | Y61A1+1      | <u>21-0190</u> | <u>90-0233</u>   |

| 14 TSSOP                        | U14+1        | <u>21-0066</u> | <u>90-0113</u>   |

| 14 SO                           | S14+1        | <u>21-0041</u> | <u>90-0112</u>   |

# High-Output-Drive, 10MHz, 10V/µs, Rail-to-Rail I/O Op Amps with Shutdown in SC70

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                       | PAGES<br>CHANGED |

|--------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------|

| 7                  | 7/08             | Added 6-pin µDFN package for the MAX4231                                                                                          | 1, 2, 8, 13      |

| 8                  | 10/08            | Corrected top mark for MAX4321, 6 SOT23 package; changed MAX4320 and 4321 to lead-free packages                                   | 1                |

| 9                  | 10/08            | Added shutdown pin limits                                                                                                         | 3, 4             |

| 10                 | 12/08            | Added automotive part number                                                                                                      | 13               |

| 11                 | 9/09             | Corrected top mark designation and pin configuration, and added UCSP package                                                      | 1, 2, 8, 13      |

| 12                 | 1/10             | Updated Absolute Maximum Ratings section                                                                                          | 2                |

| 13                 | 1/11             | Added 10 µMAX to Package Information section                                                                                      | 14               |

| 14                 | 10/11            | Updated <i>Electrical Characteristics</i> table with specs for bias current at various temperatures                               | 1-4              |

| 15                 | 3/12             | Updated thermal data in the Absolute Maximum Ratings                                                                              | 2                |

| 16                 | 6/12             | Added automotive part number for MAX4230                                                                                          | 1                |

| 17                 | 12/13            | Updated t <sub>ENABLE</sub> specification in the AC Electrical Characteristics                                                    | 6                |

| 18                 | 10/14            | Corrected µDFN references and added ultra-thin LGA reference to Ordering Information, Pin Configurations, and Package Information | 1, 13, 14        |

| 19                 | 1/15             | Updated General Description, Applications, and Benefits and Features sections                                                     | 1                |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated:

MAX4234AUD/V+ MAX4234AUD/V+T MAX4233ABC+TG45 MAX4232AKA-T MAX4233AUB MAX4233AUB-T MAX4234ASD MAX4234ASD-T MAX4234AUD MAX4234AUD-T