## **MBSOLUTE MAXIMUM RATINGS**

(Note 1)

| Supply Voltage (V <sub>CC</sub> )    | 13.2V                            |

|--------------------------------------|----------------------------------|

| Input Voltage (TIMER, SENSE)0.3      | $3V \text{ to } (V_{CC} + 0.3V)$ |

| Input Voltage (FB, ON)               | 0.3V to 13.2V                    |

| Output Voltage (RESET)               | 0.3V to 20V                      |

| Output Voltage (GATE)                | 0.3V to 20V                      |

| Operating Temperature Range          |                                  |

| LTC1422C                             | 0°C to 70°C                      |

| LTC14221                             | 40°C to 85°C                     |

| Storage Temperature Range            | . −65°C to 150°C                 |

| Lead Temperature (Soldering, 10 sec) | 300°C                            |

|                                      |                                  |

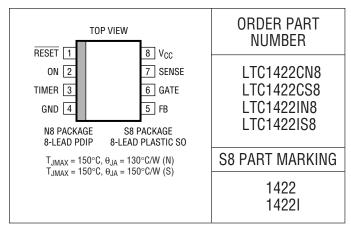

## PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges.

# **ELECTRICAL CHARACTERISTICS** The ullet denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{CC} = 5V$ unless otherwise noted.

| SYMBOL              | PARAMETER                                       | CONDITIONS                                                                        |   | MIN   | TYP        | MAX   | UNITS    |

|---------------------|-------------------------------------------------|-----------------------------------------------------------------------------------|---|-------|------------|-------|----------|

| DC Charac           | teristics                                       |                                                                                   |   |       |            |       |          |

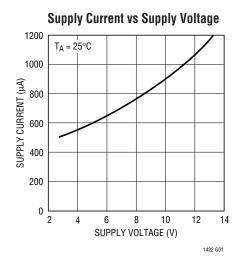

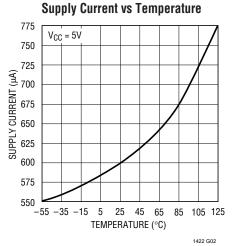

| I <sub>CC</sub>     | V <sub>CC</sub> Supply Current                  | ON = V <sub>CC</sub>                                                              | • |       | 0.65       | 1.00  | mA       |

| $V_{LKO}$           | V <sub>CC</sub> Undervoltage Lockout            |                                                                                   | • | 2.40  | 2.47       | 2.55  | V        |

| $V_{LKH}$           | V <sub>CC</sub> Undervoltage Lockout Hysteresis |                                                                                   |   |       | 120        |       | mV       |

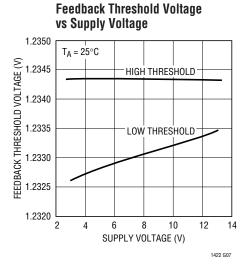

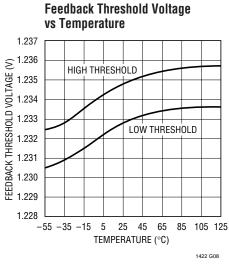

| $V_{FB}$            | FB Pin Voltage Threshold                        |                                                                                   | • | 1.220 | 1.232      | 1.244 | V        |

| $\Delta V_{FB}$     | FB Pin Threshold Line Regulation                | 3V ≤ V <sub>CC</sub> ≤ 12V                                                        | • |       | 0.5        | 2.5   | mV       |

| V <sub>FBHST</sub>  | FB Pin Voltage Threshold Hysteresis             |                                                                                   |   |       | 2.0        |       | mV       |

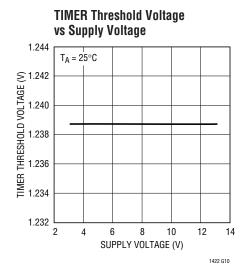

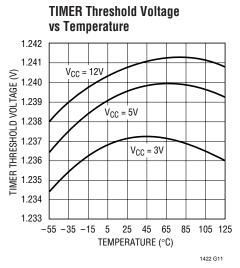

| $V_{TM}$            | TIMER Pin Voltage Threshold                     |                                                                                   | • | 1.208 | 1.232      | 1.256 | V        |

| $\Delta V_{TM}$     | TIMER Pin Threshold Line Regulation             | 3V ≤ V <sub>CC</sub> ≤ 12V                                                        | • |       | 2          | 15    | mV       |

| V <sub>TMHST</sub>  | TIMER Pin Voltage Threshold Hystersis           |                                                                                   |   |       | 45         |       | mV       |

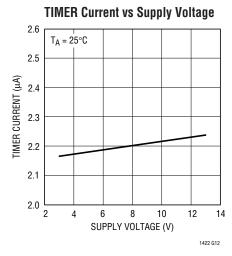

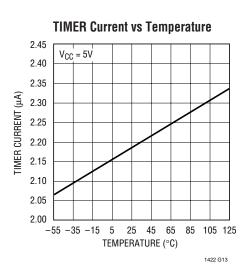

| I <sub>TM</sub>     | TIMER Pin Current                               | Timer On, GND ≤ V <sub>TIMER</sub> ≤ 1.5V<br>Timer Off, V <sub>TIMER</sub> = 1.5V | • | -2.5  | -2.0<br>10 | -1.5  | μA<br>mA |

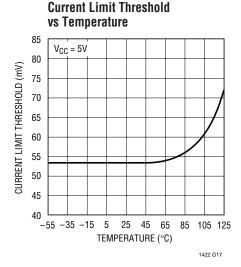

| V <sub>CB</sub>     | Circuit Breaker Trip Voltage                    | V <sub>CB</sub> = (V <sub>CC</sub> - V <sub>SENSE</sub> )                         | • | 44    | 50         | 64    | mV       |

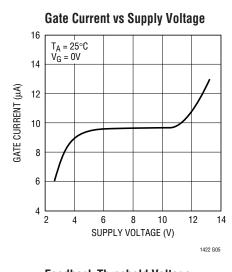

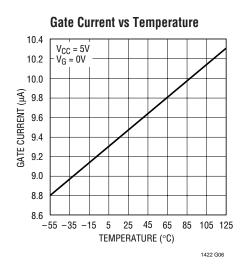

| I <sub>CP</sub>     | GATE Pin Output Current                         | Charge Pump On, $V_{GATE} = GND$<br>Charge Pump Off, $V_{GATE} = V_{CC}$          | • | -12   | -10<br>10  | -8    | μA<br>mA |

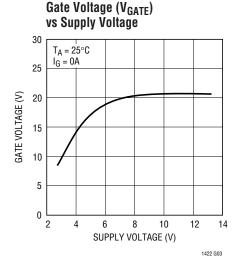

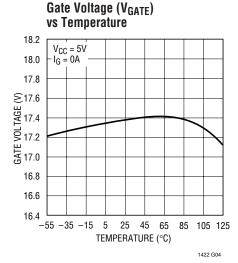

| $\Delta V_{GATE}$   | External N-Channel Gate Drive                   | V <sub>GATE</sub> – V <sub>CC</sub>                                               | • | 10    | 12         | 14    | V        |

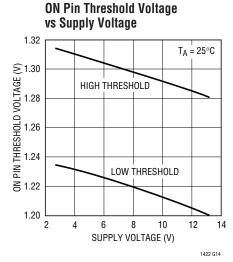

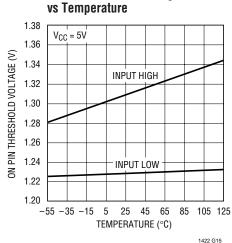

| V <sub>ONHI</sub>   | ON Pin Threshold High                           |                                                                                   | • | 1.25  | 1.30       | 1.35  | V        |

| V <sub>ONLO</sub>   | ON Pin Threshold Low                            |                                                                                   | • | 1.20  | 1.23       | 1.26  | V        |

| V <sub>ONHYST</sub> | ON Pin Hysteresis                               |                                                                                   |   |       | 80         |       | mV       |

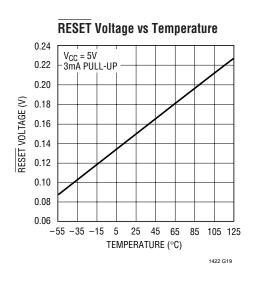

| $V_{OL}$            | Output Low Voltage                              | RESET, I <sub>0</sub> = 3mA                                                       | • |       | 0.14       | 0.4   | V        |

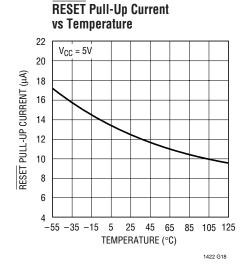

| I <sub>PU</sub>     | Logic Output Pull-Up Current                    | RESET = GND                                                                       |   |       | -12        |       | μА       |

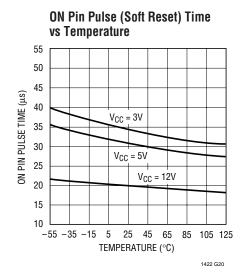

| t <sub>RST</sub>    | Soft Reset Time                                 |                                                                                   | • | 22    | 30         | 48    | μs       |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

## TYPICAL PERFORMANCE CHARACTERISTICS

## TYPICAL PERFORMANCE CHARACTERISTICS

**ON Pin Threshold Voltage**

TECHNOLOGY

### TYPICAL PERFORMANCE CHARACTERISTICS

#### PIN FUNCTIONS

**RESET** (**Pin 1**): Open drain output to GND with a  $12\mu$ A pull-up to V<sub>CC</sub>. This pin is pulled low when the voltage at the FB (Pin 5) goes below the FB pin threshold. The RESET pin will go high one timing cycle after the voltage at the FB pin goes above the FB pin threshold. An external pull-up resistor can be used to speed up the rising edge on the RESET pin or pull the pin to a voltage higher or lower than V<sub>CC</sub>.

**ON (Pin 2):** Analog Input Pin. The threshold is set at 1.30V with 80mV hysteresis. When the ON pin is pulled high, the timer turns on for one cycle, then the charge pump turns on. When the ON pin is pulled low longer than  $40\mu s$ , the GATE pin will be pulled low and remain off until the ON pin is pulled high.

If the ON pin is pulled low for less than 15 $\mu$ s a soft reset will occur. The charge pump remains on, and the RESET pin is pulled low for one timing cycle starting 30 $\mu$ s from the falling edge of the ON pin.

The ON pin is also used to reset the electronic circuit breaker. If the ON pin is cycled low and high following the trip of the circuit breaker, the circuit breaker is reset and a normal power-up sequence will occur.

**TIMER (Pin 3):** Analog system timing generator pin. This pin is used to set the delay before the charge pump turns on after the ON pin goes high. It also sets the delay before the RESET pin goes high, after the output supply voltage is good, as sensed by the FB pin.

When the timer is off, an internal N-channel shorts the TIMER pin to ground. When the timer is turned on, a  $2\mu A$  current from  $V_{CC}$  is connected to the TIMER pin and the voltage starts to ramp up with a slope given by:  $dV/dt=2\mu A/C_{TIMER}.$  When the voltage reaches the trip point (1.232V), the timer will be reset by pulling the TIMER pin back to ground. The timer period is given by: (1.232V •  $C_{TIMER}$ )/2 $\mu A$ .

GND (Pin 4): Chip Ground.

**FB** (**Pin 5**): Analog comparator input used to monitor the output supply voltage with an external resistive divider. When the voltage on the FB pin is lower than the 1.232V, the RESET pin will be pulled low. An internal filter helps prevent negative voltage glitches from triggering a reset. When the voltage on the FB pin rises above the trip point, the RESET pin will go high after one timing cycle.

#### PIN FUNCTIONS

**GATE (Pin 6):** The high side gate drive for the external N-Channel. An internal charge pump guarantees at least 10V of gate drive when  $V_{CC}$  is 5V. The slope of the voltage rise or fall at the GATE is set by an external capacitor connected between GATE and GND, and the  $10\mu A$  charge pump output current. When the circuit breaker trips, the undervoltage lockout circuit monitoring  $V_{CC}$  trips, or the ON pin is pulled low for more than  $40\mu s$ , the GATE pin is immediately pulled to GND.

**SENSE (Pin 7):** Circuit Breaker Set Pin. With a sense resistor placed in the supply path between  $V_{CC}$  and SENSE,

the circuit breaker will trip when the voltage across the resistor exceeds 50mV for more than 10 $\mu$ s. If the circuit breaker trip current is set to twice the normal operating current, only 25mV is dropped across the sense resistor during normal operation. To disable the circuit breaker, V<sub>CC</sub> and SENSE can be shorted together.

$V_{CC}$  (Pin 8): The positive supply input, ranging from 2.7V to 13.2V for normal operation.  $I_{CC}$  is typically 0.6mA. An undervoltage lockout circuit disables the chip until the voltage at  $V_{CC}$  is greater than 2.47V.

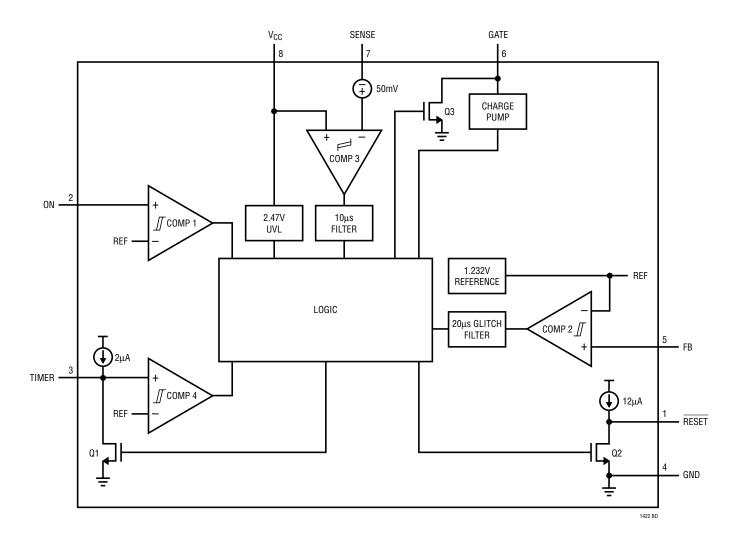

### **BLOCK DIAGRAM**

LINEAR

#### **Hot Circuit Insertion**

When circuit boards are inserted into a live backplane, the supply bypass capacitors on the board can draw huge transient currents from the backplane power bus as they charge up. The transient currents can cause permanent damage to the connector pins and cause glitches on the system supply, causing other boards in the system to reset.

The LTC1422 is designed to turn a board's supply voltage on and off in a controlled manner, allowing the board to be safely inserted or removed from a live backplane. The chip also provides a system reset signal to indicate when board supply voltage drops below a programmable voltage.

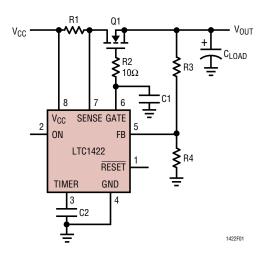

#### **Power Supply Ramping**

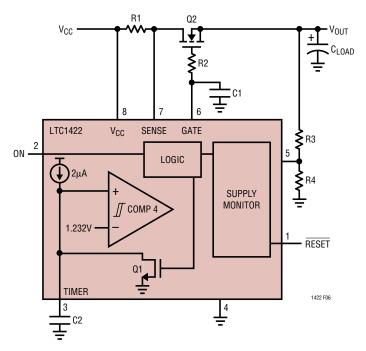

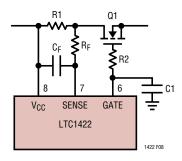

The onboard power supply is controlled by placing an external N-channel pass transistor in the power path (Figure 1). R1 provides current fault detection and R2 prevents high frequency oscillation. By ramping up the gate of the pass transistor at a controlled rate, the transient surge current ( $I = C \cdot dV/dt$ ) drawn from the main backplane supply can be limited to a safe value when the board makes connection.

Figure 1. Supply Control Circuitry

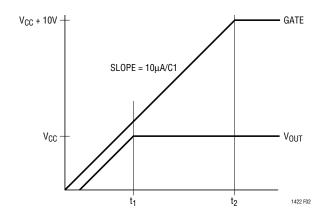

When power is first applied to the chip, the gate of the N-channel (Pin 6) is pulled low. After the ON pin is held high for at least one timing cycle, the charge pump is turned on. The voltage at GATE begins to rise with a slope

Figure 2. Supply Turn-On

equal to  $10\mu\text{A/C1}$  (Figure 2), where C1 is the external capacitor connected between the GATE pin and GND.

The ramp time for the supply is equal to:  $t = (V_{CC} \cdot C1)/10\mu A$ . After the ON pin has been pulled low for more than  $40\mu s$ , the GATE is immediately pulled to GND.

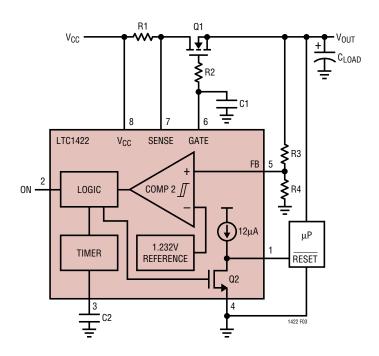

#### **Voltage Monitor**

The LTC1422 uses a 1.232V bandgap reference, precision voltage comparator and a resistive divider to monitor the output supply voltage (Figure 3).

Figure 3. Supply Monitor Block Diagram

1422f

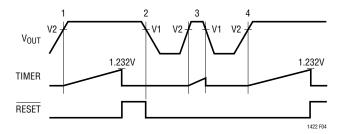

Figure 4. Supply Monitor Waveforms

When the voltage at the FB pin rises above its reset threshold (1.232V), the comparator COMP 2 output goes high, and a timing cycle starts (Figure 4, time points 1 and 4). After a complete timing cycle, RESET is pulled high. The  $12\mu A$  pull-up current source to  $V_{CC}$  on RESET has a series diode so the pin can be pulled above  $V_{CC}$  by an external pull-up resistor without forcing current back into supply.

When the supply voltage at the FB pin drops below its reset threshold, the comparator Comp 2 output goes low. After passing through a glitch filter, RESET is pulled low (time point 2). If the FB pin rises above the reset threshold for less than a timing cycle, the RESET output will remain low (time point 3).

#### Glitch Filter

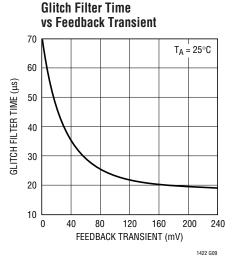

The LTC1422 has a glitch filter to prevent  $\overline{RESET}$  from generating a system reset when there are transients on the FB pin. The filter is  $20\mu s$  for large transients (greater than 150mV) and up to  $80\mu s$  for small transients. The relationship between glitch filter time and the transient voltage is shown in Typical Performance curve: Glitch Filter Time vs Feedback Transient.

#### **Soft Reset**

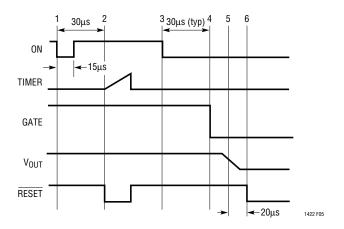

In some cases a system reset is desired without a power down. The ON pin can signal the RESET pin to go low without turning off the external N-channel (a soft reset). This is accomplished by holding the ON pin low for only 15µs or less (Figure 5, time point 1). At about 30µs from the falling edge of the ON pin (time point 2) the RESET pin goes low and stays low for one timing cycle.

Figure 5. Soft Reset Waveforms

If the ON pin is held  $\underline{low for}$  longer than  $30\mu s$  (typ), the gate will turn off and the RESET pin will eventually go low (time points 4, 5 and 6).

#### Timer

The system timing for the LTC1422 is generated by the circuitry shown in Figure 6. The timer is used to set the turn-on delay after the ON pin goes high and the delay before the RESET pin goes high after the output supply voltage is good as sensed by the FB pin.

Figure 6. System Timing Block Diagram

When the timer is off, the internal N-channel Q1 shorts the TIMER pin to ground. When the timer is turned on, a  $2\mu A$  current from  $V_{CC}$  is connected to the TIMER pin and the voltage on the external capacitor C2 starts to ramp up with a slope given by:  $dV/dt = 2\mu A/C2$ . When the voltage reaches the trip point (1.232V), the timer will be reset by pulling the TIMER pin back to ground. The timer period is given by:  $(1.232V \cdot C2)/2\mu A$ . For a 200ms delay, use a  $0.33\mu F$  capacitor.

#### **Electronic Circuit Breaker**

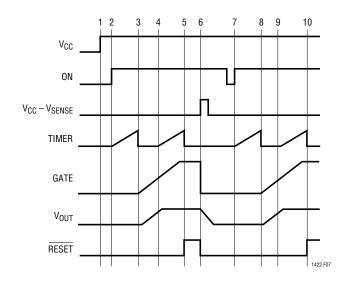

The LTC1422 features an electronic circuit breaker function that protects against short circuits or excessive currents on the supply. By placing a sense resistor between the supply input and SENSE pin, the circuit breaker will be tripped whenever the voltage across the sense resistor is greater than 50mV for more than 10 $\mu$ s. When the circuit breaker trips, the GATE pin is immediately pulled to ground and the external N-channel is quickly turned off. When the ON pin is cycled off for greater than 40 $\mu$ s and then on as shown in Figure 7, time point 7, the circuit breaker is reset and another timing cycle is started.

At the end of the timer cycle (time point 8), the charge pump will turn on again. If the circuit breaker feature is not required, the SENSE pin should be shorted to  $V_{CC}$ .

If more than 10µs of response time is needed to reject supply noise, an external resistor and capacitor can be added to the sense circuit as shown in Figure 8.

#### **Connection Sense with ON Pin**

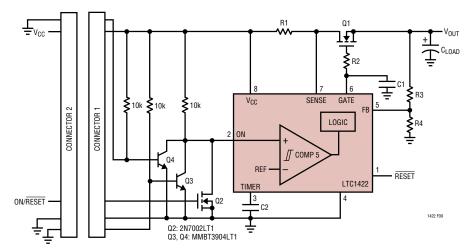

The ON pin can be used to sense board connection to the backplane as shown in Figure 9.

Using staggered connection pins, ground mates first to discharge any static build up on the board, followed by the  $V_{CC}$  connection and all other pins. When  $V_{CC}$  makes connection, the bases of transistors Q3 and Q4 are pulled high turning them on and pulling the ON pin to ground. When the base connector pins of Q3 and Q4 finally mate to the backplane, the bases are shorted to ground. This turns off Q3 and Q4 and allows the ON pin to pull high and start a power-up cycle. The base connection pins of Q3 and Q4 should be located at opposite ends of the connector

Figure 7. Current Fault Timing

Figure 8. Extending the Short-Circuit Protection Delay

because most people will rock the board back and forth to get it seated properly.

A software-initiated power-down cycle can be started by momentarily turning on transistor Q2, which will pull the ON pin to ground. If the ON pin is held low for greater than  $40\mu s$ , the GATE pin is pulled to ground. If the low pulse on the ON pin is less than  $15\mu s$ , a soft reset is generated.

#### **Hot Swapping Two Supplies**

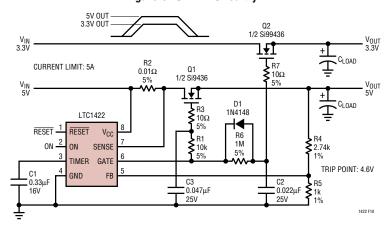

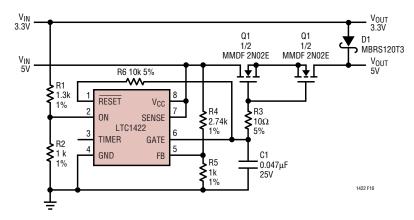

With two external pass transistors, the LTC1422 can switch two supplies. In some cases, it is necessary to bring up the dominant supply first during power-up and ramp it down last during the power-down phase. The circuit in Figure 10 shows how to program two different delays for the pass transistors. The 5V supply is powered up first. R1

Figure 9. ON Pin Circuitry

Figure 10. Switching 5V and 3.3V

and C3 are used to set the rise and fall delays on the 5V supply. Next, the 3.3V supply ramps up with a 20ms delay set by R6 and C2. On the falling edge, the 3.3V supply ramps down first because R6 is bypassed by the diode D1.

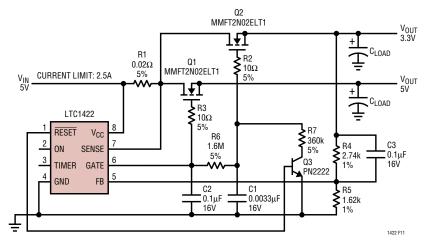

#### Using the LTC1422 as a Linear Regulator

The LTC1422 can be used to Hot Swap the primary supply and generate a secondary low dropout regulated supply. Figure 11 shows how to switch a 5V supply and create a 3.3V supply using the reset comparator and one additional transistor. The FB pin is used to monitor the 3.3V output. When the voltage on the gate of Q2 increases, the 3.3V increases. At the 3.3V threshold, the reset comparator will trip. The RESET pin goes high which turns on Q3. This lowers the voltage on the gate of Q2. This feedback loop is compensated by the capacitor C1 and the resistors R6 and R7.

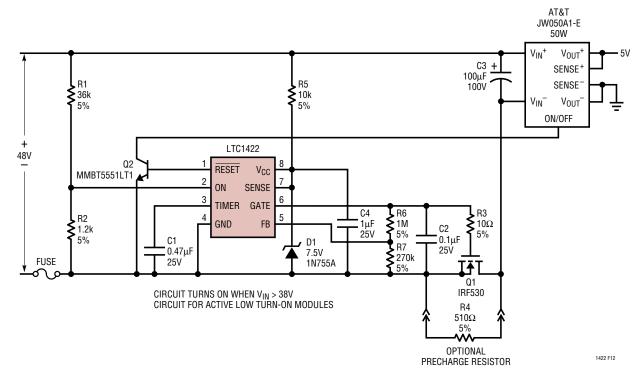

# Hot Swapping 48V DC/DC Module with Active Low On/Off Control Signal

Using a 7.5V Zener and a resistor, the LTC1422 can switch supplies much greater than the 12V  $V_{CC}$  pin rating. As shown in Figure 12, the switching FET Q1 is connected as a common source driver rather than the usual source follower used in previous applications. This allows the ground of the LTC1422 to sit at the negative terminal of the 48V input. The clamp circuit of R5 and D1 provides power to the LTC1422. The resistive divider R1 and R2 at the ON pin monitors the input supply. The switching FET Q1 is prevented from turning on until the input supply is at least 38V. Using the reset comparator to monitor the gate voltage allows the module to be turned on after the gate has reached a minimum level plus one timing cycle. A high voltage transistor Q2 is used to translate the RESET signal to the module On/Off input.

Since the pass transistor is in a common source configuration, care must be taken to limit the inrush current into capacitor C3. One way is to precharge C3 using resistor R4. As the input supply is ramping up, current is flowing through R4 and charging the capacitor C3. Once the input supply crosses 38V, there is a timing cycle followed by the ramp-up of the GATE pin. By this time the capacitor C3 is sufficiently charged, thereby limiting the inrush current. Another method to limit the inrush current is to slow down the ramp-up rate of the GATE pin.

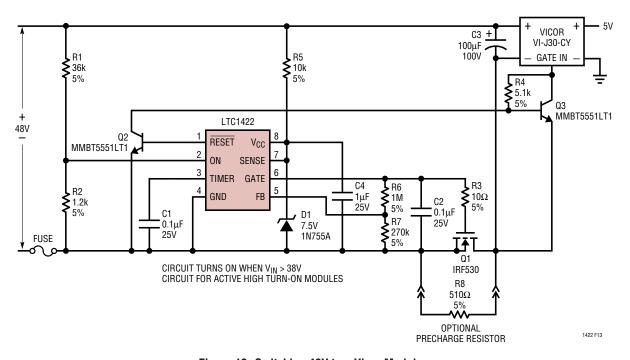

## Hot Swapping 48V DC/DC Module with Active High On/Off Control Signal

This application is identical to the previous except for the polarity of the module's on/off signal. The polarity reversal is accomplished by transistor Q3 in Figure 13.

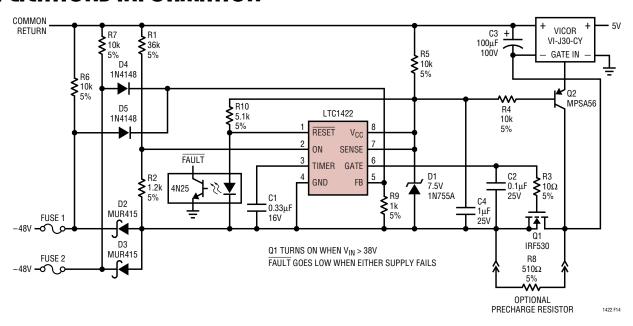

#### **Hot Swapping Redundant 48V**

In critical situations, redundant input supplies are necessary. In Figure 14 a redundant 48V input is switched to a power module. Supplies 1 and 2 are wire OR'ed using two diodes D2 and D3. This results in the most negative of these two supplies being used to drive the power module. If one of the supplies is disconnected or a fuse opens, the fault signal will be activated via diodes D4 and D5 and the reset comparator at the FB pin. The GATE IN signal on the Vicor module is controlled using the high voltage PNP Q2. Once the module's minus input pin is more negative than the base of Q2 plus a diode drop, Q2 will turn off and the module will turn on. This occurs when the source of Q1

plus a Zener voltage (D1) is more positive than the drain of Q1 (in other words, when the switching FET Q1 has only 7.5V across its drain source).

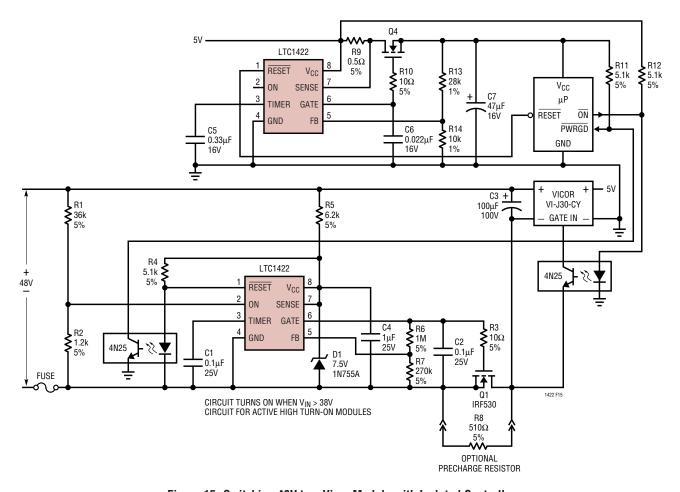

#### Hot Swapping 48V Module with Isolated Controller

A power supervisory controller will sometimes reside on an isolated supply with responsibility for other supplies. Figure 15 shows how to Hot Swap a controller's 5V supply and a 48V module using two LTC1422s. Assuming the 5V supply comes up first, the controller waits for a power good signal from the 48V circuit. Once it receives the right signals the controller activates the GATE IN pin of the Vicor power module.

#### **Power Supply Sequencer**

A circuit that forces two supply voltages to power up together is shown in Figure 16. The input supply voltages may power up in any sequence, but both input voltages must be within tolerance before Q1 and Q2 turn on. Backto-back transistors Q1 and Q2 ensure isolation between the two supplies.

When the 5V input powers up before 3.3V, Q1 and Q2 remain off and the 5V output remains off until the 3.3V input is within tolerance as sensed by resistors R1 and R2. When the 3.3V input powers up before 5V, the diode D1 will pull up the 5V supply output with it. Once the 5V input powers up and is within tolerance as sensed by R4 and R5, Q1 and Q2 will turn on in about 1ms and pull the 5V output up to its final voltage.

Figure 11. Switching 5V and Generating 3.3V

#### **Power N-Channel and Sense Resistor Selection**

The decision of which external power N-Channel to use is dependent on its maximum current rating and the maximum allowed current times  $R_{DS(ON)}$  drop across the transistor. Table 1 lists some transistors that are available.

Table 2 lists some current sense resistors that can be used with the circuit breaker. Since this information is subject to change, please verify the part numbers with the manufacturer. Table 3 lists the web sites of several manufacturers.

Table 1. N-Channel Selection Guide

| CURRENT LEVEL (A) | PART NUMBER | DESCRIPTION                                         | MANUFACTURER     |  |

|-------------------|-------------|-----------------------------------------------------|------------------|--|

| 0 to 2            | MMDF3N02HD  | Dual N-Channel SO-8 $R_{DS(0N)} = 0.1\Omega$        | ON Semiconductor |  |

| 2 to 5            | MMSF5N02HD  | Single N-Channel SO-8<br>$R_{DS(0N)} = 0.025\Omega$ | ON Semiconductor |  |

| 5 to 10           | MTB50N06V   | Single N-Channel DD Pak $R_{DS(0N)} = 0.028\Omega$  | ON Semiconductor |  |

| 10 to 20          | MTB75N05HD  | Single N-Channel DD Pak $R_{DS(0N)} = 0.0095\Omega$ | ON Semiconductor |  |

Table 2. Sense Resistor Selection Guide

| CURRENT LIMIT VALUE | PART NUMBER  | DESCRIPTION              | MANUFACTURER |  |

|---------------------|--------------|--------------------------|--------------|--|

| 1A                  | LR120601R050 | 0.05Ω 0.25W 1% Resistor  | IRC-TT       |  |

| 2A                  | LR120601R025 | 0.025Ω 0.25W 1% Resistor | IRC-TT       |  |

| 2.5A                | LR120601R020 | 0.02Ω 0.25W 1% Resistor  | IRC-TT       |  |

| 3.3A                | WSL2512R015F | 0.015Ω 1W 1% Resistor    | Vishay-Dale  |  |

| 5A                  | LR120601R010 | 0.01Ω 0.25W 1% Resistor  | IRC-TT       |  |

| 10A                 | WSR2R005F    | 0.005Ω 2W 1% Resistor    | Vishay-Dale  |  |

Table 3. Manufacturers' Web Sites

| MANUFACTURER            | WEB SITE                |

|-------------------------|-------------------------|

| TEMIC Semiconductor     | www.temic.com           |

| International Rectifier | www.irf.com             |

| ON Semiconductor        | www.onsemiconductor.com |

| Harris Semiconductor    | www.semi.harris.com     |

| IRC-TT                  | www.irctt.com           |

| Vishay-Dale             | www.vishay.com          |

Figure 12. Switching 48V to an AT&T Module

Figure 13. Switching 48V to a Vicor Module

Figure 14. Hot Swapping Redundant 48V Supplies

Figure 15. Switching 48V to a Vicor Module with Isolated Controller

LINEAR

Figure 16. Power Supply Sequencer

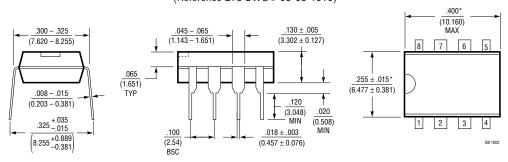

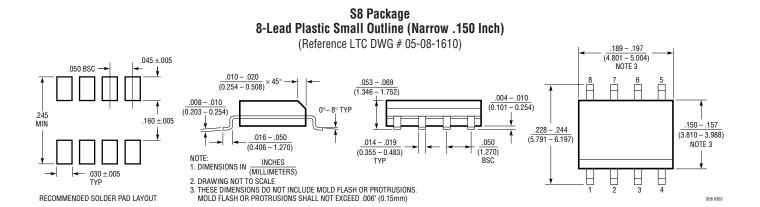

## PACKAGE DESCRIPTION

#### N8 Package 8-Lead PDIP (Narrow .300 Inch) (Reference LTC DWG # 05-08-1510)

NOTE:

1. DIMENSIONS ARE MILLIMETERS

<sup>\*</sup>THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED .010 INCH (0.254mm)

LINEAR

#### TYPICAL APPLICATION

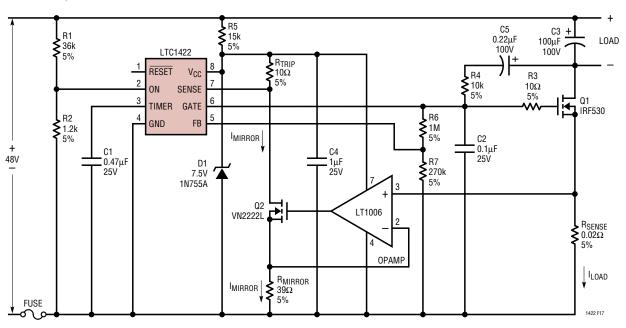

#### **Current Sensing with 48V Applications**

In the LTC1422, the SENSE pin threshold is 50mV below the  $V_{CC}$  pin. Typically, the current sense resistor is connected to the  $V_{CC}$  pin, but in 48V applications the sense resistor is connected to the negative terminal of the 48V supply. The circuit in Figure 17 translates the current in the sense resistor to a resistor connected to the LTC1422 SENSE pin.

The voltage drop across the current sense resistor  $R_{SENSE}$  is proportional to the load current  $I_{LOAD}$ . The voltage drop across  $R_{SENSE}$  is buffered by the op amp follower and is forced on  $R_{MIRROR}$ .

The mirror current can be described as:  $I_{MIRROR} = I_{LOAD} \cdot R_{SENSE}/R_{MIRROR}$ . The mirror current flows through the trip resistor  $R_{TRIP}$ . When the mirror current generates 50mV across  $R_{TRIP}$ , the LTC1422 will latch the GATE pin low (50mV =  $I_{MIRROR} \cdot R_{TRIP} = I_{LOAD} \cdot R_{SENSE}/R_{MIRROR} \cdot R_{TRIP}$ ). This example uses a 48V input but this translation circuit can be used anywhere the current sense resistor is not tied to  $V_{CC}$ .

Figure 17. Switching 48V with Current Sensing

## **RELATED PARTS**

| PART NUMBER       | DESCRIPTION                                  | COMMENTS                                    |

|-------------------|----------------------------------------------|---------------------------------------------|

| LTC1421           | Hot Swap Controller                          | 24-Pin Multiple Supplies                    |

| LT1640L/LT1640H   | Negative Voltage Hot Swap Controller in SO-8 | Operates from -10V to -80V                  |

| LT1641            | High Voltage Hot Swap Controller in SO-8     | Operates from 9V to 80V                     |

| LT1642            | Fault Protected Hot Swap Controller          | Operates Up to 16.5V, Protected to 33V      |

| LTC1643L/LTC1643H | PCI-Bus Hot Swap Controller                  | 3.3V, 5V and ±12V in Narrow 16-Pin SSOP     |

| LT1645            | 2-Channel Hot Swap Controller                | Operates from 1.2V to 12V, Power Sequencing |

| LTC1647           | Dual Hot Swap Controller in SO-8 or SSOP-16  | Two ON Pins, Operates from 2.7V to 16.5V    |

LT/TP 0503 1K REV B • PRINTED IN USA

TECHNOLOGY

© LINEAR TECHNOLOGY CORPORATION 1997

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## **Analog Devices Inc.:**

<u>LTC1422IS8 LTC1422CS8#TR LTC1422IS8#TRPBF LTC1422CN8#PBF LTC1422CS8 LTC1422CS8#TRPBF LTC1422IS8#PBF LTC1422IS8#PBF LTC1422IS8#TRPBF LTC1422IS8#TRPBF LTC1422IS8#TR</u>