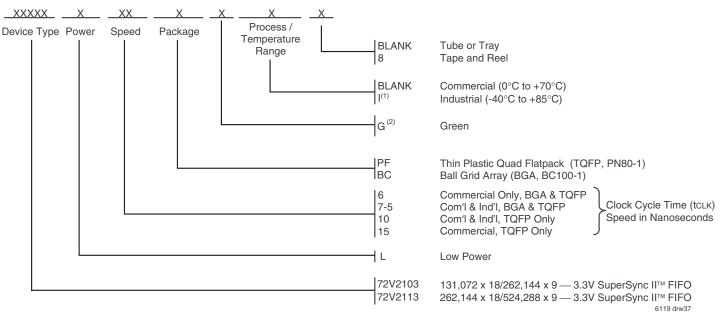

# IDT72V2103/72V2113 3.3V HIGH DENSITY SUPERSYNC II™ NARROW BUS FIFO 131,072 x 18/262,144 x 9, 262,144 x 18/524,288 x 9

## DESCRIPTION:

The IDT72V2103/72V2113 are exceptionally deep, high speed, CMOS First-In-First-Out (FIFO) memories with clocked read and write controls and a flexible Bus-Matching x9/x18 data flow. These FIFOs offer numerous improvements over previous SuperSync FIFOs, including the following:

- Flexible x9/x18 Bus-Matching on both read and write ports.

- The limitation of the frequency of one clock input with respect to the other has been removed. The Frequency Select pin (FS) has been removed, thus it is no longer necessary to select which of the two clock inputs, RCLK or WCLK, is running at the higher frequency.

- The period required by the retransmit operation is now fixed and short.

- The first word data latency period, from the time the first word is written to an empty FIFO to the time it can be read, is now fixed and short. (The variable clock cycle counting delay associated with the latency period found on previous SuperSync devices has been eliminated on this SuperSync family.)

- Asynchronous/Synchronous translation on the read or write ports.

- High density offerings up to 4 Mbit.

Bus-Matching SuperSync FIFOs are particularly appropriate for network, video, telecommunications, data communications and other applications that need to buffer large amounts of data and match busses of unequal sizes.

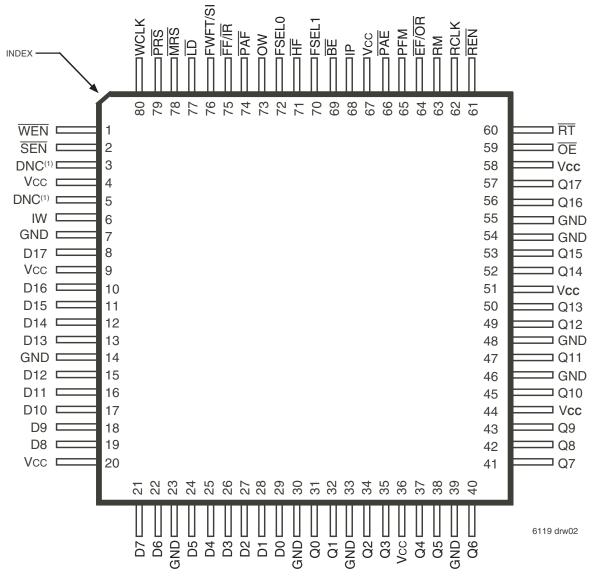

# PIN CONFIGURATIONS

NOTE: 1. DNC = Do Not Connect.

> TQFP (PN80, order code: PF) TOP VIEW

> > 2

# IDT72V2103/72V2113 3.3V HIGH DENSITY SUPERSYNC II™ NARROW BUS FIFO 131,072 x 18/262,144 x 9, 262,144 x 18/524,288 x 9

## DESCRIPTION (CONTINUED)

Each FIFO has a data input port (Dn) and a data output port (Qn), both of which can assume either an 18-bit or a 9-bit width as determined by the state of external control pins Input Width (IW) and Output Width (OW) during the Master Reset cycle.

The input port can be selected as either a Synchronous (clocked) interface, or Asynchronous interface. During Synchronous operation the input port is controlled by a Write Clock (WCLK) input and a Write Enable ( $\overline{WEN}$ ) input. Data present on the Dn data inputs is written into the FIFO on every rising edge of WCLK when  $\overline{WEN}$  is asserted. During Asynchronous operation only the WR input is used to write data into the FIFO. Data is written on a rising edge of WR, the  $\overline{WEN}$  input should be tied to its active state, (LOW).

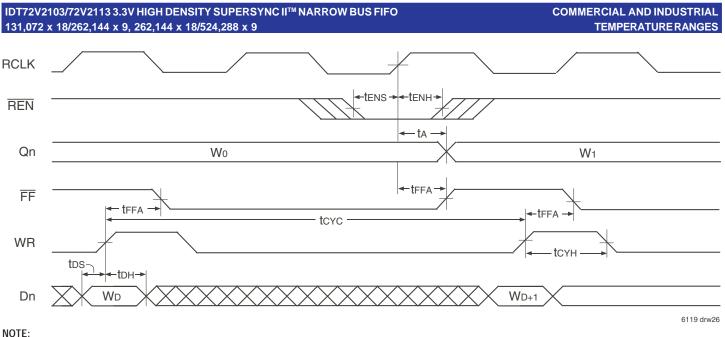

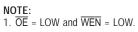

The output port can be selected as either a Synchronous (clocked) interface, or Asynchronous interface. During Synchronous operation the output port is controlled by a Read Clock (RCLK) input and Read Enable (REN) input. Data is read from the FIFO on every rising edge of RCLK when REN is asserted.

During Asynchronous operation only the RD input is used to read data from the FIFO. Data is read on a rising edge of RD, the  $\overline{\text{REN}}$  input should be tied to its active state, LOW. When Asynchronous operation is selected on the output port the FIFO must be configured for Standard IDT mode, and the  $\overline{\text{OE}}$  input used to provide three-state control of the outputs, Qn.

The frequencies of both the RCLK and the WCLK signals may vary from 0 to fMAX with complete independence. There are no restrictions on the frequency of the one clock input with respect to the other.

There are two possible timing modes of operation with these devices: IDT Standard mode and First Word Fall Through (FWFT) mode.

In *IDT Standard mode*, the first word written to an empty FIFO will not appear on the data output lines unless a specific read operation is performed. A read operation, which consists of activating REN and enabling a rising RCLK edge, will shift the word from internal memory to the data output lines.

In *FWFT mode*, the first word written to an empty FIFO is clocked directly to the data output lines after three transitions of the RCLK signal. A REN does

## PINCONFIGURATIONS (CONTINUED)

|   | *             | /                                 | A1 BALL P    | AD CO    | RNER       |            |           |          |                                         |                          |

|---|---------------|-----------------------------------|--------------|----------|------------|------------|-----------|----------|-----------------------------------------|--------------------------|

| Α | O<br>WCLK     | O<br>PRS                          |              | O<br>PAF | O<br>FSEL0 |            | O<br>ASYR | O<br>PFM | O<br>RM                                 | O<br>REN                 |

| В | $O \over WEN$ | $\bigcup_{\overline{\text{MRS}}}$ | O<br>FWFT/SI | O<br>ow  |            | O<br>FSEL1 | O<br>IP   | O<br>PAE | $\bigcup_{\overline{EF}/\overline{OR}}$ | O<br>rclk                |

| С | O<br>ASYW     | $\frac{O}{SEN}$                   | O<br>FF/IR   | O<br>Vcc | O<br>Vcc   | O<br>Vcc   | O<br>Vcc  | O<br>Vcc | O<br>RT                                 | O<br>OE                  |

| D | O             | O                                 | O            | O        | O          | O          | O         | O        | O                                       | O                        |

|   | D17           | IW                                | Vcc          | gnd      | GND        | GND        | GND       | Vcc      | Q16                                     | Q17                      |

| Е | O             | O                                 | O            | O        | O          | O          | O         | O        | O                                       | O                        |

|   | D16           | D15                               | Vcc          | GND      | GND        | GND        | GND       | Vcc      | Q14                                     | Q15                      |

| F | O             | O                                 | O            | O        | O          | O          | O         | O        | O                                       | O                        |

|   | D13           | D14                               | Vcc          | GND      | GND        | GND        | GND       | Vcc      | Q13                                     | Q12                      |

| G | O             | O                                 | O            | O        | O          | O          | O         | O        | O                                       | O                        |

|   | D11           | D12                               | Vcc          | GND      | GND        | GND        | GND       | Vcc      | Q11                                     | Q10                      |

| н | O             | O                                 | O            | O        | O          | O          | O         | O        | O                                       | ()                       |

|   | D8            | D9                                | D10          | Vcc      | Vcc        | Vcc        | Vcc       | Q1       | Q9                                      | Q8                       |

| J | O             | O                                 | O            | O        | О          | О          | O         | ()       | O                                       | 0                        |

|   | D6            | D7                                | D2           | D0       | тмs        | тск        | tdo       | Q2       | Q4                                      | Q7                       |

| K | O             | O                                 | O            | O        | O          | O          | O         | ()       | O                                       | O                        |

|   | D5            | D4                                | D3           | D1       | TRST       | TDI        | Q0        | Q3       | Q5                                      | Q6                       |

|   | 1             | 2                                 | 3            | 4        | 5          | 6          | 7         | 8        | 9                                       | <b>10</b><br>6119 drw02b |

BGA: 1mm pitch, 11mm x 11mm (BC100, order code: BC) TOP VIEW

## DESCRIPTION (CONTINUED)

not have to be asserted for accessing the first word. However, subsequent words written to the FIFO do require a LOW on  $\overline{\text{REN}}$  for access. The state of the FWFT/SI input during Master Reset determines the timing mode in use.

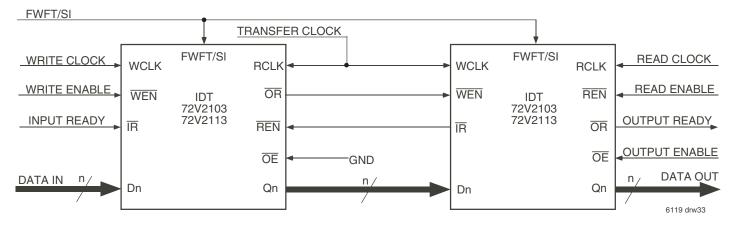

For applications requiring more data storage capacity than a single FIFO can provide, the FWFT timing mode permits depth expansion by chaining FIFOs in series (i.e. the data outputs of one FIFO are connected to the corresponding data inputs of the next). No external logic is required.

These FIFOs have five flag pins, EF/OR (Empty Flag or Output Ready), FF/IR (Full Flag or Input Ready), HF (Half-full Flag), PAE (Programmable Almost-Emptyflag) and PAF (Programmable Almost-Fullflag). The EF and FF functions are selected in IDT Standard mode. The IR and OR functions are selected in FWFT mode. HF, PAE and PAF are always available for use, irrespective of timing mode.

$\overrightarrow{PAE}$  and  $\overrightarrow{PAF}$  can be programmed independently to switch at any point in memory. Programmable offsets determine the flag switching threshold and can be loaded by two methods: parallel or serial. Eight default offset settings are also provided, so that  $\overrightarrow{PAE}$  can be set to switch at a predefined number of locations from the empty boundary and the  $\overrightarrow{PAF}$  threshold can also be set at similar predefined values from the full boundary. The default offset values are set during Master Reset by the state of the FSEL0, FSEL1, and  $\overrightarrow{LD}$  pins. For serial programming,  $\overline{SEN}$  together with  $\overline{LD}$  on each rising edge of WCLK, are used to load the offset registers via the Serial Input (SI). For parallel programming,  $\overline{WEN}$  together with  $\overline{LD}$  on each rising edge of WCLK, are used to load the offset registers via Dn.  $\overline{REN}$  together with  $\overline{LD}$  on each rising edge of RCLK can be used to read the offsets in parallel from Qn regardless of whether serial or parallel offset loading has been selected.

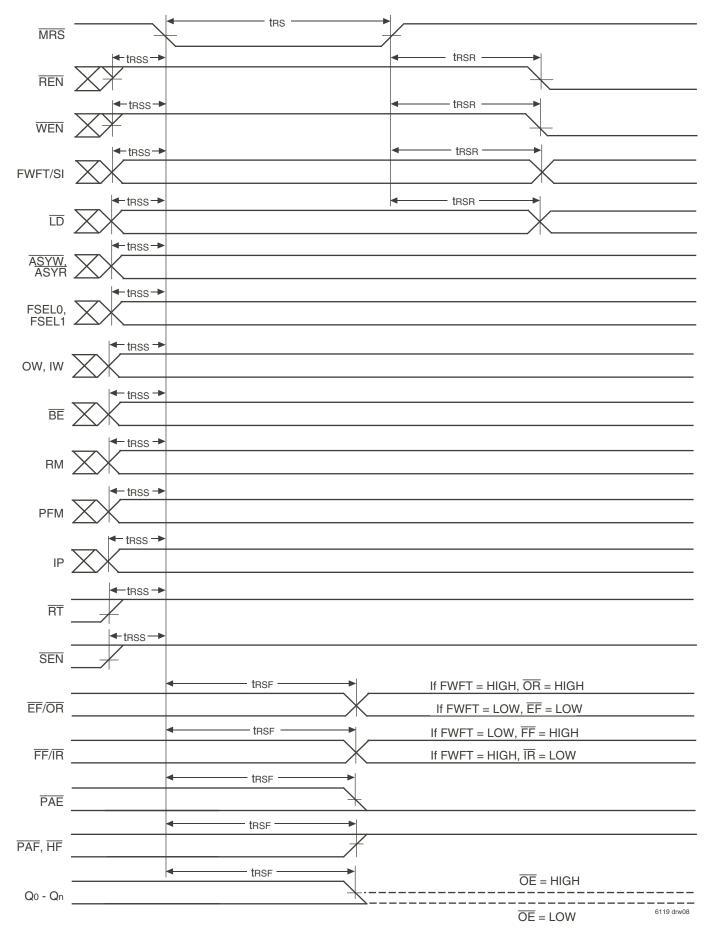

During Master Reset (MRS) the following events occur: the read and write pointers are set to the first location of the FIFO. The FWFT pin selects IDT Standard mode or FWFT mode.

The Partial Reset (PRS) also sets the read and write pointers to the first location of the memory. However, the timing mode, programmable flag programming method, and default or programmed offset settings existing before Partial Reset remain unchanged. The flags are updated according to the timing mode and offsets in effect. PRS is useful for resetting a device in mid-operation, when reprogramming programmable flags would be undesirable.

It is also possible to select the timing mode of the  $\overline{\text{PAE}}$  (Programmable Almost-Empty flag) and  $\overline{\text{PAF}}$  (Programmable Almost-Full flag) outputs. The timing modes can be set to be either asynchronous or synchronous for the  $\overline{\text{PAE}}$  and  $\overline{\text{PAF}}$  flags.

If asynchronous PAE/PAF configuration is selected, the PAE is asserted LOW on the LOW-to-HIGH transition of RCLK. PAE is reset to HIGH on the LOW-

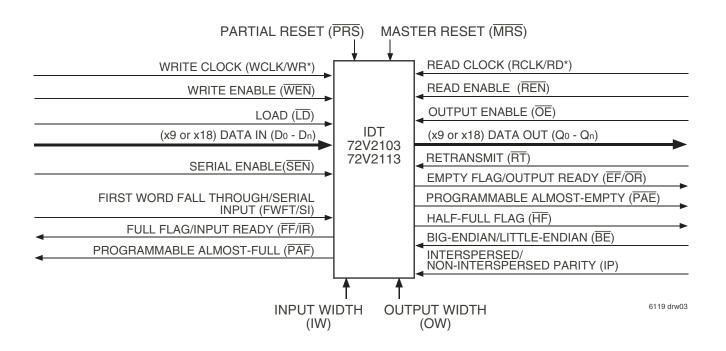

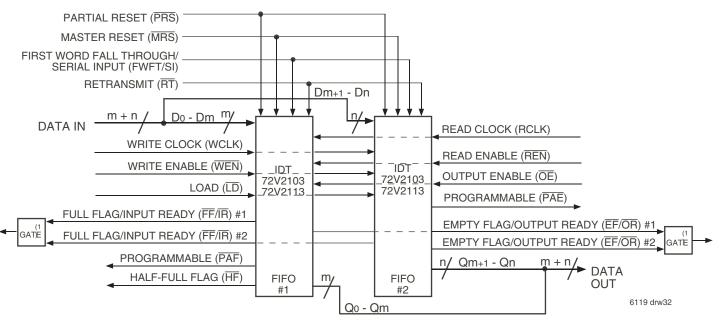

Figure 1. Single Device Configuration Signal Flow Diagram

to-HIGH transition of WCLK. Similarly, the PAF is asserted LOW on the LOWto-HIGH transition of WCLK and PAF is reset to HIGH on the LOW-to-HIGH transition of RCLK.

If synchronous PAE/PAF configuration is selected, the PAE is asserted and updated on the rising edge of RCLK only and not WCLK. Similarly, PAF is asserted and updated on the rising edge of WCLK only and not RCLK. The mode desired is configured during master reset by the state of the Programmable Flag Mode (PFM) pin.

The Retransmit function allows data to be reread from the FIFO more than once. A LOW on the  $\overline{\text{RT}}$  input during a rising RCLK edge initiates a retransmit operation by setting the read pointer to the first location of the memory array. A zero-latency retransmit timing mode can be selected using the Retransmit timing Mode pin (RM). During Master Reset, a LOW on RM will select zero-latency retransmit. A HIGH on RM during Master Reset will select normal latency.

If zero-latency retransmit operation is selected the first data word to be retransmitted will be placed on the output register with respect to the same RCLK edge that initiated the retransmit based on RT being LOW.

Refer to Figure 11 and 12 for *Retransmit Timing* with normal latency. Refer to Figure 13 and 14 for *Retransmit Timing* with zero-latency.

A Big-Endian/Little-Endian data word format is provided. This function is useful when data is written into the FIFO in long word format (x18) and read out of the FIFO in small word (x9) format. If Big-Endian mode is selected, then the most significant byte (word) of the long word written into the FIFO will be read

out of the FIFO first, followed by the least significant byte. If Little-Endian format is selected, then the least significant byte of the long word written into the FIFO will be read out first, followed by the most significant byte. The mode desired is configured during master reset by the state of the Big-Endian (BE) pin.

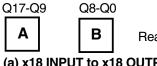

The Interspersed/Non-Interspersed Parity (IP) bit function allows the user to select the parity bit in the word loaded into the parallel port (Do-Dn) when programming the flag offsets. If Interspersed Parity mode is selected, then the FIFO will assume that the parity bit is located in bit position Da during the parallel programming of the flag offsets. If Non-Interspersed Parity mode is selected, then Da is assumed to be a valid bit and D16 and D17 are ignored. IP mode is selected during Master Reset by the state of the IP input pin. This mode is relevant only when the input width is set to x18 mode. Interspersed Parity control only has an effect during parallel programming of the offset registers. It does not effect the data written to and read from the FIFO.

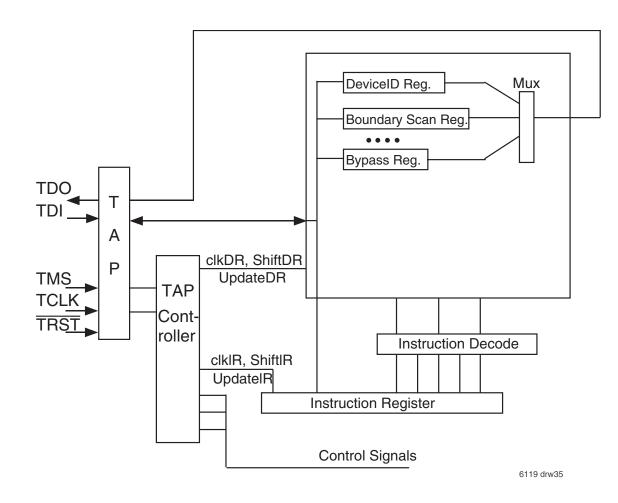

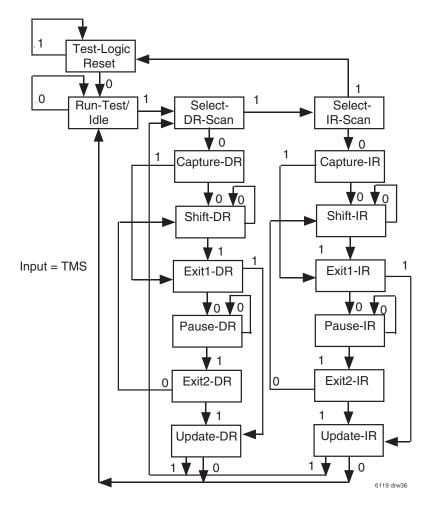

A JTAG test port is provided, here the FIFO has fully functional Boundary Scan feature, compliant with IEEE 1149.1 Standard Test Access Port and Boundary Scan Architecture.

If, at any time, the FIFO is not actively performing an operation, the chip will automatically power down. Once in the power down state, the standby supply current consumption is minimized. Initiating any operation (by activating control inputs) will immediately take the device out of the power down state.

The IDT72V2103/72V2113 are fabricated using IDT's high speed submicron CMOS technology.

## TABLE 1 — BUS-MATCHING CONFIGURATION MODES

| IW | OW | Write Port Width | Read Port Width |

|----|----|------------------|-----------------|

| L  | L  | x18              | x18             |

| L  | Н  | x18              | x9              |

| Н  | L  | х9               | x18             |

| Н  | Н  | х9               | х9              |

# PIN DESCRIPTION (TQFP & BGA PACKAGES)

| Symbol               | Name                                 | I/0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------|--------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BE <sup>(1)</sup>    | *Big-Endian/<br>Little-Endian        | Ι   | During Master Reset, a LOW on BE will select Big-Endian operation. A HIGH on BE during Master Reset will select Little-Endian format.                                                                                                                                                                                                                                                                                                                                                                                                |

| D0-D17               | Data Inputs                          | Ι   | Data inputs for a 18- or 9-bit bus. When in 18-bit mode, D0–D17 are used. When in 9-bit mode, D0–D8 are used and the unused inputs, D9–D17, should be tied LOW.                                                                                                                                                                                                                                                                                                                                                                      |

| EF/OR                | Empty Flag/<br>Output Ready          | 0   | In the IDT Standard mode, the $\overline{EF}$ function is selected. $\overline{EF}$ indicates whether or not the FIFO memory is empty. In FWFT mode, the $\overline{OR}$ function is selected. $\overline{OR}$ indicates whether or not there is valid data available at the outputs.                                                                                                                                                                                                                                                |

| FF/IR                | Full Flag/<br>Input Ready            | 0   | In the IDT Standard mode, the FF function is selected. FF indicates whether or not the FIFO memory is full. In the FWFT mode, the IR function is selected. IR indicates whether or not there is space available for writing to the FIFO memory.                                                                                                                                                                                                                                                                                      |

| FSEL0 <sup>(1)</sup> | Flag Select Bit 0                    | Ι   | During Master Reset, this input along with FSEL1 and the $\overline{LD}$ pin, will select the default offset values for the programmable flags PAE and PAF. There are up to eight possible settings available.                                                                                                                                                                                                                                                                                                                       |

| FSEL1 <sup>(1)</sup> | Flag Select Bit 1                    | Ι   | During Master Reset, this input along with FSEL0 and the LD pin will select the default offset values for the programmable flags PAE and PAF. There are up to eight possible settings available.                                                                                                                                                                                                                                                                                                                                     |

| FWFT/SI              | First Word Fall<br>Through/Serial In | Ι   | During Master Reset, selects First Word Fall Through or IDT Standard mode. After Master Reset, this pin functions as a serial input for loading offset registers.                                                                                                                                                                                                                                                                                                                                                                    |

| ĦF                   | Half-Full Flag                       | 0   | HF indicates whether the FIFO memory is more or less than half-full.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| IP <sup>(1)</sup>    | Interspersed Parity                  | Ι   | During Master Reset, a LOW on IP will select Non-Interspersed Parity mode. A HIGH will select Interspersed Parity mode. Interspersed Parity control only has an effect during parallel programming of the offset registers. It does not effect the data written to and read from the FIFO.                                                                                                                                                                                                                                           |

| IW <sup>(1)</sup>    | Input Width                          | Ι   | This pin selects the bus width of the write port. During Master Reset, when IW is LOW, the write port will be configured with a x18 bus width. If IW is HIGH, the write port will be a x9 bus width.                                                                                                                                                                                                                                                                                                                                 |

| ĪD                   | Load                                 | -   | This is a dual purpose pin. During Master Reset, the state of the $\overline{\text{LD}}$ input, along with FSEL0 and FSEL1, determines one of eight default offset values for the $\overline{\text{PAE}}$ and $\overline{\text{PAF}}$ flags, along with the method by which these offset registers can be programmed, parallel or serial (see Table 2). After Master Reset, this pin enables writing to and reading from the offset registers.                                                                                       |

| MRS                  | Master Reset                         | Ι   | MRS initializes the read and write pointers to zero and sets the output register to all zeroes. During Master Reset, the FIFO is configured for either FWFT or IDT Standard mode, Bus-Matching configurations, one of eight programmable flag default settings, serial or parallel programming of the offset settings, Big-Endian/Little-Endian format, zero latency timing mode, interspersed parity, and synchronous versus asynchronous programmable flag timing modes.                                                           |

| ŌĒ                   | Output Enable                        | Ι   | OE controls the output impedance of Qn.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| OW <sup>(1)</sup>    | Output Width                         | Ι   | This pin selects the bus width of the read port. During Master Reset, when OW is LOW, the read port will be config-<br>ured with a x18 bus width. If OW is HIGH, the read port will be a x9 bus width.                                                                                                                                                                                                                                                                                                                               |

| PAE                  | Programmable<br>Almost-Empty Flag    | 0   | PAE goes LOW if the number of words in the FIFO memory is less than offset n, which is stored in the Empty Offset register. PAE goes HIGH if the number of words in the FIFO memory is greater than or equal to offset n.                                                                                                                                                                                                                                                                                                            |

| PAF                  | Programmable<br>Almost-Full Flag     | 0   | PAF goes HIGH if the number of free locations in the FIFO memory is more than offset m, which is stored in the Full Offset register. PAF goes LOW if the number of free locations in the FIFO memory is less than or equal to m.                                                                                                                                                                                                                                                                                                     |

| PFM <sup>(1)</sup>   | Programmable<br>Flag Mode            | I   | During Master Reset, a LOW on PFM will select Asynchronous Programmable flag timing mode. A HIGH on PFM will select Synchronous Programmable flag timing mode.                                                                                                                                                                                                                                                                                                                                                                       |

| PRS                  | Partial Reset                        | Ι   | PRS initializes the read and write pointers to zero and sets the output register to all zeroes. During Partial Reset, the existing mode (IDT or FWFT), programming method (serial or parallel), and programmable flag settings are all retained.                                                                                                                                                                                                                                                                                     |

| Q0–Q17               | Data Outputs                         | 0   | Data outputs for a 18- or 9-bit bus. When in 18-bit mode, $Q_0-Q_{17}$ are used and when in 9-bit mode, $Q_0-Q_8$ are used, and the unused outputs, Q9-Q17 should not be connected. Outputs are not 5V tolerant regardless of the state of $\overline{OE}$ .                                                                                                                                                                                                                                                                         |

| REN                  | Read Enable                          | Ι   | REN enables RCLK for reading data from the FIFO memory and offset registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RCLK/<br>RD          | Read Clock/<br>Read Strobe           | Ι   | If Synchronous operation of the read port has been selected, when enabled by REN, the rising edge of RCLK reads data from the FIFO memory and offsets from the programmable registers. If LD is LOW, the values loaded into the offset registers is output on a rising edge of RCLK. If Asynchronous operation of the read port has been selected, a rising edge on RD reads data from the FIFO in an Asynchronous manner. REN should be tied LOW. Asynchronous operation of the RCLK/RD input is only available in the BGA package. |

NOTE:

1. Inputs should not change state after Master Reset.

# PIN DESCRIPTION-CONTINUED (TQFP & BGA PACKAGES)

| Symbol            | Name                         | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------|------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RM <sup>(1)</sup> | Retransmit Timing<br>Mode    | I   | During Master Reset, a LOW on RM will select zero latency Retransmit timing Mode. A HIGH on RM will select normal latency mode.                                                                                                                                                                                                                                                                           |

| RT                | Retransmit                   | I   | $\overline{\text{RT}}$ asserted on the rising edge of RCLK initializes the READ pointer to zero, sets the $\overline{\text{EF}}$ flag to LOW ( $\overline{\text{OR}}$ to HIGH in FWFT mode) and does not disturb the write pointer, programming method, existing timing mode or programmable flag settings. $\overline{\text{RT}}$ is useful to reread data from the first physical location of the FIFO. |

| SEN               | Serial Enable                | Ι   | SEN enables serial loading of programmable flag offsets.                                                                                                                                                                                                                                                                                                                                                  |

| WCLK/<br>WR       | Write Clock/<br>Write Strobe | Ι   | If Synchronous operation of the write port has been selected, when enabled by WEN, the rising edge of WCLK writes data into the FIFO. If Asynchronous operation of the write port has been selected, WR writes data into the FIFO on a rising edge in an Asynchronous manner, (WEN should be tied to its active state). Asynchronous operation of the WCLK/WR input is only available in the BGA package. |

| WEN               | Write Enable                 | I   | WEN enables WCLK for writing data into the FIFO memory and offset registers.                                                                                                                                                                                                                                                                                                                              |

| Vcc               | +3.3V Supply                 | I   | These are VCC supply inputs and must be connected to the 3.3V supply rail.                                                                                                                                                                                                                                                                                                                                |

NOTE:

1. Inputs should not change state after Master Reset.

# PIN DESCRIPTION (BGA PACKAGE ONLY)

|                     |                            | <u> </u> |                                                                                                                                                                                                                                                                                                                                                            |

|---------------------|----------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol              | Name                       | 1/0      | Description                                                                                                                                                                                                                                                                                                                                                |

| ASYR <sup>(1)</sup> | Asynchronous<br>Read Port  | I        | A HIGH on this input during Master Reset will select Synchronous read operation for the output port. A LOW will select Asynchronous operation. If Asynchronous is selected the FIFO must operate in IDT Standard mode.                                                                                                                                     |

| ASYW <sup>(1)</sup> | Asynchronous<br>Write Port | I        | A HIGH on this input during Master Reset will select Synchronous write operation for the input port. A LOW will select Asynchronous operation.                                                                                                                                                                                                             |

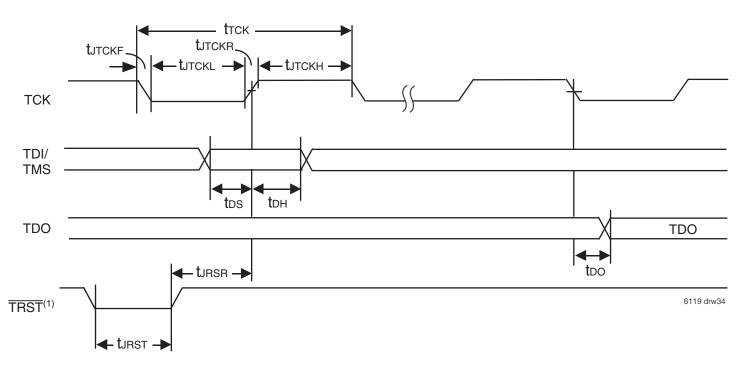

| TCK <sup>(2)</sup>  | JTAG Clock                 | I        | Clock input for JTAG function. One of four terminals required by IEEE Standard 1149.1-1990. Test operations of the device are synchronous to TCK. Data from TMS and TDI are sampled on the rising edge of TCK and outputs change on the falling edge of TCK. If the JTAG function is not used this signal needs to be tied to GND.                         |

| TDI <sup>(2)</sup>  | JTAG Test Data<br>Input    | I        | One of four terminals required by IEEE Standard 1149.1-1990. During the JTAG boundary scan operation, test data serially loaded via the TDI on the rising edge of TCK to either the Instruction Register, ID Register and Bypass Register. An internal pull-up resistor forces TDI HIGH if left unconnected.                                               |

| TDO <sup>(2)</sup>  | JTAG Test Data<br>Output   | 0        | One of four terminals required by IEEE Standard 1149.1-1990. During the JTAG boundary scan operation, test data serially loaded output via the TDO on the falling edge of TCK from either the Instruction Register, ID Register and Bypass Register. This output is high impedance except when shifting, while in SHIFT-DR and SHIFT-IR controller states. |

| TMS <sup>(2)</sup>  | JTAG Mode                  | I        | TMS is a serial input pin. One of four terminals required by IEEE Standard 1149.1-1990. TMS directs the device through its TAP controller states. An internal pull-up resistor forces TMS HIGH if left unconnected.                                                                                                                                        |

| TRST <sup>(2)</sup> | JTAG Reset                 |          | TRST is an asynchronous reset pin for the JTAG controller. The JTAG TAP controller will automatically reset upon power-up. If the JTAG function is not used then this signal should to be tied to GND.                                                                                                                                                     |

NOTES:

1. Inputs should not change state after Master Reset.

2. These pins are for the JTAG port. Please refer to pages 41-45 and Figures 31-33.

# ABSOLUTE MAXIMUM RATINGS

| Symbol               | Rating                               | Com'l & Ind'l | Unit |

|----------------------|--------------------------------------|---------------|------|

| VTERM <sup>(2)</sup> | Terminal Voltage with respect to GND | -0.5 to +4.5  | V    |

| Tstg                 | Storage Temperature                  | –55 to +125   | °C   |

| Ιουτ                 | DC Output Current                    | -50 to +50    | mA   |

#### NOTE:

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. Vcc terminal only.

# RECOMMENDED DC OPERATING CONDITIONS

| Symbol             | Parameter                          | Min. | Тур. | Max. | Unit |

|--------------------|------------------------------------|------|------|------|------|

| VCC <sup>(1)</sup> | Supply Voltage (Com'l & Ind'l)     | 3.15 | 3.3  | 3.45 | V    |

| GND                | Supply Voltage (Com'l & Ind'l)     | 0    | 0    | 0    | V    |

| VIH <sup>(2)</sup> | Input High Voltage (Com'l & Ind'l) | 2.0  | _    | 5.5  | V    |

| VIL <sup>(3)</sup> | Input Low Voltage (Com'l & Ind'l)  | _    | _    | 0.8  | V    |

| TA                 | Operating Temperature Commercial   | 0    | _    | +70  | °C   |

| Ta                 | Operating Temperature Industrial   | -40  | —    | +85  | °C   |

#### NOTES:

1. Vcc=3.3V ± 0.15V, JEDEC JESD8-A compliant.

2. Outputs are not 5V tolerant.

3. 1.5V undershoots are allowed for 10ns once per cycle.

# DCELECTRICAL CHARACTERISTICS

(Commercial: Vcc = 3.3V ± 0.15V, TA = 0°C to +70°C; Industrial: Vcc = 3.3V ± 0.15V, TA = -40°C to +85°C; JEDEC JESD8-A compliant)

|                         |                                                       | IDT72V21<br>Commercial and | IDT72V2103L<br>IDT72V2113L<br>Commercial and Industrial <sup>(1)</sup><br>tCLK = 6, 7-5, 10, 15 ns |      |

|-------------------------|-------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------|------|

| Symbol                  | Parameter                                             | Min.                       | Max.                                                                                               | Unit |

| LI <sup>(2)</sup>       | Input Leakage Current                                 | -1                         | 1                                                                                                  | μA   |

| LO <sup>(3)</sup>       | Output Leakage Current                                | -10                        | 10                                                                                                 | μA   |

| Vон                     | Output Logic "1" Voltage, IOH = -2 mA                 | 2.4                        | _                                                                                                  | V    |

| Vol                     | Output Logic "0" Voltage, IOL = 8 mA                  | —                          | 0.4                                                                                                | V    |

| ICC1 <sup>(4,5,6)</sup> | Active Power Supply Current (x9 Input to x9 Output)   | —                          | 30                                                                                                 | mA   |

| ICC1 <sup>(4,5,6)</sup> | Active Power Supply Current (x18 Input to x18 Output) | -                          | 35                                                                                                 | mA   |

| ICC2 <sup>(4,7)</sup>   | Standby Current                                       | —                          | 15                                                                                                 | mA   |

NOTES:

1. Industrial temperature range product for the 7-5ns and 10ns speed grades are available as a standard device. All other speed grades are available by special order.

2. Measurements with  $0.4 \leq V_{IN} \leq V_{CC}$ .

3.  $\overline{OE} \ge V_{IH}$ ,  $0.4 \le V_{OUT} \le V_{CC}$ .

4. Tested with outputs open (IOUT = 0).

5. RCLK and WCLK toggle at 20 MHz and data inputs switch at 10 MHz.

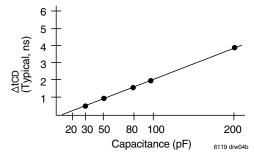

6. For x 18 bus widths, typical lcc1 = 5 + fs + 0.002\*CL\*fs (in mA); for x 9 bus widths, typical lcc1 = 5 + 0.775\*fs + 0.002\*CL\*fs (in mA). These equations are valid under the following conditions: Vcc = 3.3V. ta = 25°C. fs = WCLK frequency = RCLK frequency (in the following conditions).

Vcc = 3.3V, ta = 25°C, fs = WCLK frequency = RCLK frequency (in MHz, using TTL levels), data switching at fs/2, CL = capacitive load (in pF).

7. All Inputs = Vcc - 0.2V or GND + 0.2V, except RCLK and WCLK, which toggle at 20 MHz.

## CAPACITANCE (TA = +25°C, f = 1.0MHz)

| Symbol                | Parameter <sup>(1)</sup> | Conditions    | Max. | Unit |

|-----------------------|--------------------------|---------------|------|------|

| CIN <sup>(2)</sup>    | Input                    | $V_{IN} = 0V$ | 10   | pF   |

|                       | Capacitance              |               |      |      |

| COUT <sup>(1,2)</sup> | Output                   | Vout = 0V     | 10   | pF   |

|                       | Capacitance              |               |      |      |

#### NOTES:

1. With output deselected, ( $\overline{OE} \ge V_{IH}$ ).

2. Characterized values, not currently tested.

## AC ELECTRICAL CHARACTERISTICS<sup>(1)</sup>

(Commercial: Vcc =  $3.3V \pm 0.15V$ , TA = 0°C to +70°C; Industrial: Vcc =  $3.3V \pm 0.15V$ , TA = -40°C to +85°C; JEDEC JESD8-A compliant)

|               |                                                          | Comm<br>BGA & | nercial<br>TQFP  | Com'l &<br>BGA &   |       | Com'l &<br>TQFP    |      | Comm<br>TQFP       |      |      |

|---------------|----------------------------------------------------------|---------------|------------------|--------------------|-------|--------------------|------|--------------------|------|------|

|               |                                                          |               | 2103L6<br>2113L6 | IDT72V2<br>IDT72V2 |       | IDT72V2<br>IDT72V2 |      | IDT72V2<br>IDT72V2 |      |      |

| Symbol        | Parameter                                                | Min.          | Max.             | Min.               | Max.  | Min.               | Max. | Min.               | Max. | Unit |

| fs            | Clock Cycle Frequency                                    | _             | 166              | —                  | 133.3 | _                  | 100  | _                  | 66.7 | MHz  |

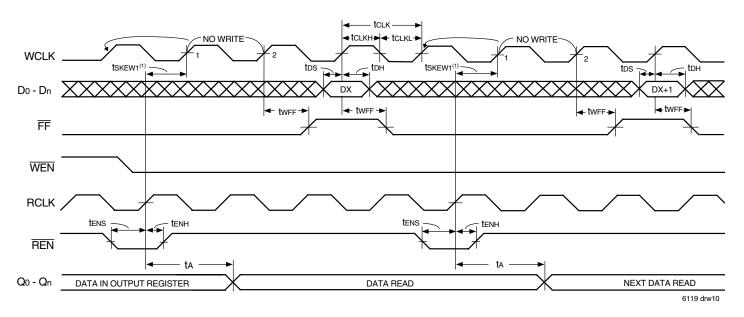

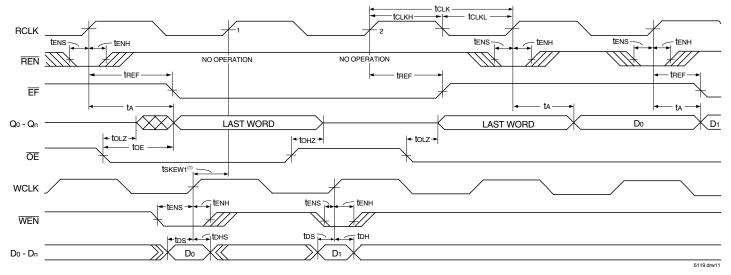

| tA            | Data Access Time <sup>(5)</sup>                          | 1             | 4                | 1(5)               | 5     | 1(5)               | 6.5  | 1(5)               | 10   | ns   |

| tCLK          | Clock Cycle Time                                         | 6             | —                | 7.5                |       | 10                 | —    | 15                 | —    | ns   |

| <b>t</b> CLKH | Clock High Time                                          | 2.7           | —                | 3.5                | _     | 4.5                | —    | 6                  | —    | ns   |

| <b>t</b> CLKL | Clock Low Time                                           | 2.7           | —                | 3.5                | _     | 4.5                | —    | 6                  | —    | ns   |

| tDS           | Data Setup Time                                          | 2             | —                | 2.5                | _     | 3.5                | —    | 4                  | —    | ns   |

| tDH           | Data Hold Time                                           | 0.5           | —                | 0.5                | _     | 0.5                | —    | 1                  | —    | ns   |

| tens          | Enable Setup Time                                        | 2             | —                | 2.5                | —     | 3.5                | —    | 4                  | —    | ns   |

| tenh          | Enable Hold Time                                         | 0.5           | —                | 0.5                | —     | 0.5                | —    | 1                  | —    | ns   |

| tlds          | Load Setup Time                                          | 3             | —                | 3.5                | —     | 3.5                | —    | 4                  | —    | ns   |

| tldh          | Load Hold Time                                           | 0.5           | —                | 0.5                | —     | 0.5                | —    | 1                  | —    | ns   |

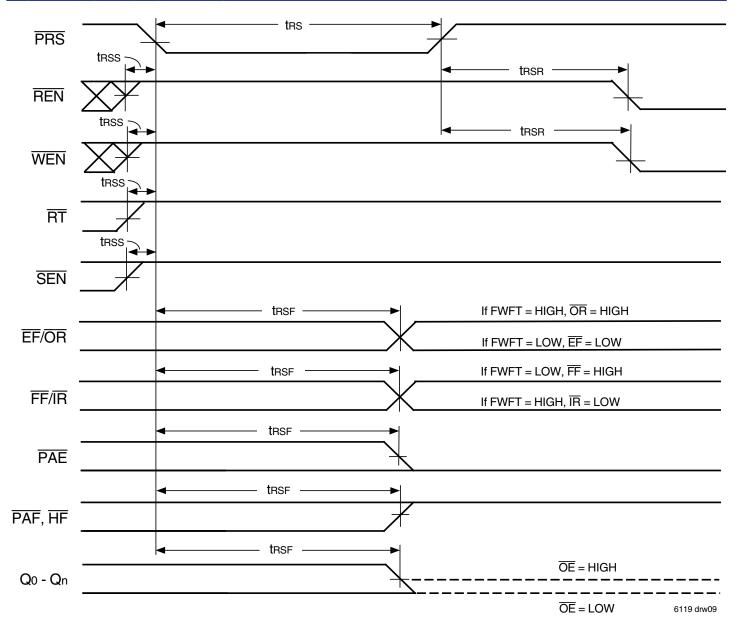

| tRS           | Reset Pulse Width <sup>(3)</sup>                         | 10            | —                | 10                 | —     | 10                 | —    | 15                 | —    | ns   |

| trss          | Reset Setup Time                                         | 15            | _                | 15                 | _     | 15                 | —    | 15                 | _    | ns   |

| trsr          | Reset Recovery Time                                      | 10            | _                | 10                 | _     | 10                 | —    | 15                 | _    | ns   |

| trsf          | Reset to Flag and Output Time                            | —             | 15               | —                  | 15    | —                  | 15   | —                  | 15   | ns   |

| trts          | Retransmit Setup Time                                    | 3             | _                | 3.5                | _     | 3.5                | —    | 4                  | _    | ns   |

| tolz          | Output Enable to Output in Low Z <sup>(4)</sup>          | 0             | —                | 0                  | _     | 0                  | —    | 0                  | —    | ns   |

| toe           | Output Enable to Output Valid <sup>(5)</sup>             | 1             | 4                | 1(5)               | 6     | 1(5)               | 6    | 1(5)               | 8    | ns   |

| tонz          | Output Enable to Output in High Z <sup>(4,5)</sup>       | 1             | 4                | 1(5)               | 6     | 1(5)               | 6    | 1(5)               | 8    | ns   |

| twff          | Write Clock to $\overline{FF}$ or $\overline{IR}$        | _             | 4                | —                  | 5     | —                  | 6.5  | —                  | 10   | ns   |

| <b>t</b> REF  | Read Clock to EF or OR                                   | _             | 4                | —                  | 5     | —                  | 6.5  | —                  | 10   | ns   |

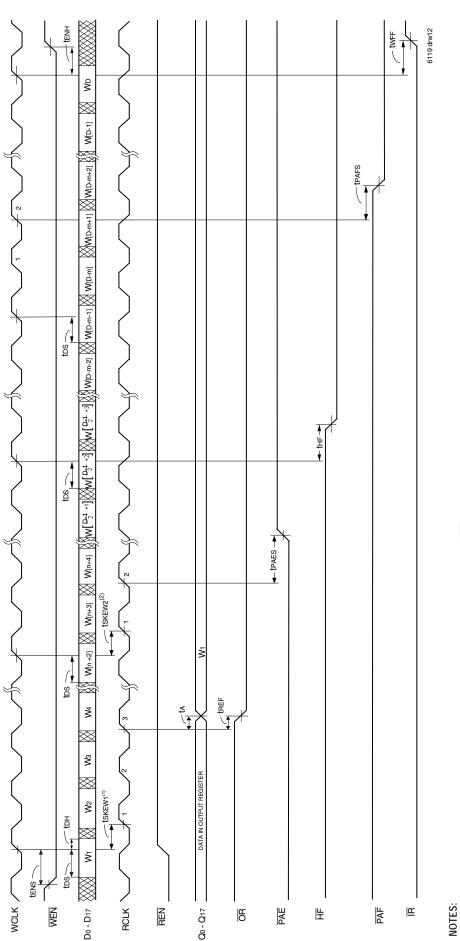

| <b>t</b> PAFA | Clock to Asynchronous Programmable Almost-Full Flag      | _             | 10               | —                  | 12.5  | —                  | 16   | —                  | 20   | ns   |

| <b>t</b> PAFS | Write Clock to Synchronous Programmable Almost-Full Flag | _             | 4                | —                  | 5     | _                  | 6.5  | _                  | 10   | ns   |

| <b>t</b> PAEA | Clock to Asynchronous Programmable Almost-Empty Flag     | _             | 10               | —                  | 12.5  | —                  | 16   | —                  | 20   | ns   |

| <b>t</b> PAES | Read Clock to Synchronous Programmable Almost-Empty Flag | _             | 4                | —                  | 5     | _                  | 6.5  | _                  | 10   | ns   |

| thf           | Clock to HF                                              | _             | 10               | _                  | 12.5  | —                  | 16   | —                  | 20   | ns   |

| tskew1        | Skew time between RCLK and WCLK for EF/OR and FF/IR      | 4             | —                | 5                  | —     | 7                  |      | 9                  | _    | ns   |

| tSKEW2        | Skew time between RCLK and WCLK for PAE and PAF          | 5             | _                | 7                  | _     | 10                 | _    | 14                 | _    | ns   |

NOTES:

1. All AC timings apply to both Standard IDT mode and First Word Fall Through mode.

2. Industrial temperature range product for the 7-5ns and 10ns are available as a standard device. All other speed grades are available by special order.

3. Pulse widths less than minimum values are not allowed.

4. Values guaranteed by design, not currently tested.

5. TQFP package only: for speed grades 7-5ns, 10ns and 15ns the minimum for tA, tOE, and tOHZ is 2ns.

# AC ELECTRICAL CHARACTERISTICS<sup>(1)</sup> — ASYNCHRONOUS TIMING

(Commercial: Vcc =  $3.3V \pm 0.15V$ , TA = 0°C to +70°C;Industrial: Vcc =  $3.3V \pm 0.15V$ , TA = -40°C to +85°C; JEDEC JESD8-A compliant)

|                      |                                                      | Comn | nercial                      | Com'l & Ind'l |                                  |      |  |

|----------------------|------------------------------------------------------|------|------------------------------|---------------|----------------------------------|------|--|

|                      |                                                      |      | IDT72V2103L6<br>IDT72V2113L6 |               | IDT72V2103L7-5<br>IDT72V2113L7-5 |      |  |

| Symbol               | Parameter                                            | Min. | Max.                         | Min.          | Max.                             | Unit |  |

| fA <sup>(4)</sup>    | Cycle Frequency (Asynchronous mode)                  | _    | 100                          | —             | 83                               | MHz  |  |

| taa <sup>(4)</sup>   | Data Access Time                                     | 0.6  | 8                            | 0.6           | 10                               | ns   |  |

| tcyc <sup>(4)</sup>  | Cycle Time                                           | 10   | _                            | 12            | —                                | ns   |  |

| tcyh <sup>(4)</sup>  | Cycle HIGH Time                                      | 4.5  | _                            | 5             | —                                | ns   |  |

| tcyl <sup>(4)</sup>  | Cycle LOW Time                                       | 4.5  | _                            | 5             | —                                | ns   |  |

| trpe <sup>(4)</sup>  | Read Pulse after EF HIGH                             | 8    | _                            | 10            | _                                | ns   |  |

| tffa <sup>(4)</sup>  | Clock to Asynchronous FF                             | _    | 8                            | _             | 10                               | ns   |  |

| tefa <sup>(4)</sup>  | Clock to Asynchronous EF                             | _    | 8                            | _             | 10                               | ns   |  |

| tpafa <sup>(4)</sup> | Clock to Asynchronous Programmable Almost-Full Flag  | _    | 8                            | _             | 10                               | ns   |  |

| tpaea <sup>(4)</sup> | Clock to Asynchronous Programmable Almost-Empty Flag | -    | 8                            | _             | 10                               | ns   |  |

NOTES:

1. All AC timings apply to both Standard IDT mode and First Word Fall Through mode.

2. Pulse widths less than minimum values are not allowed.

Values guaranteed by design, not currently tested.

Parameters apply to the BGA package only.

# AC TEST CONDITIONS

| Input Pulse Levels                 | GND to 3.0V        |

|------------------------------------|--------------------|

| Input Rise/Fall Times              | 3ns <sup>(1)</sup> |

| Input Timing Reference Levels      | 1.5V               |

| Output Reference Levels            | 1.5V               |

| Output Load for tCLK = 10ns, 15 ns | See Figure 2a      |

| Output Load for tCLK = 6ns, 7.5ns  | See Figure 2b & 2c |

#### NOTE:

1. For 166MHz and 133MHz operation input rise/fall times are 1.5ns.

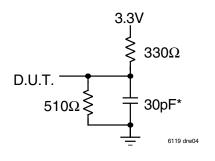

## ACTESTLOADS-10ns, 15ns Speed Grades

Figure 2a. Output Load \* Includes jig and scope capacitances.

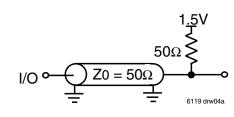

# ACTESTLOADS-6ns, 7.5ns Speed Grades

Figure 2b. AC Test Load

Figure 2c. Lumped Capacitive Load, Typical Derating

# OUTPUT ENABLE & DISABLE TIMING

1. REN is HIGH.

## **FUNCTIONAL DESCRIPTION**

# TIMING MODES: IDT STANDARD vs FIRST WORD FALL THROUGH (FWFT) MODE

The IDT72V2103/72V2113 support two different timing modes of operation: IDT Standard mode or First Word Fall Through (FWFT) mode. The selection of which mode will operate is determined during Master Reset, by the state of the FWFT/SI input.

If, at the time of Master Reset, FWFT/SI is LOW, then IDT Standard mode will be selected. This mode uses the Empty Flag ( $\overline{EF}$ ) to indicate whether or not there are any words present in the FIFO. It also uses the Full Flag function ( $\overline{FF}$ ) to indicate whether or not the FIFO has any free space for writing. In IDT Standard mode, every word read from the FIFO, including the first, must be requested using the Read Enable ( $\overline{REN}$ ) and RCLK.

If, at the time of Master Reset, FWFT/SI is HIGH, then FWFT mode will be selected. This mode uses Output Ready ( $\overline{OR}$ ) to indicate whether or not there is valid data at the data outputs (Qn). It also uses Input Ready ( $\overline{IR}$ ) to indicate whether or not the FIFO has any free space for writing. In the FWFT mode, the first word written to an empty FIFO goes directly to Qn after three RCLK rising edges,  $\overline{REN} = LOW$  is not necessary. Subsequent words must be accessed using the Read Enable ( $\overline{REN}$ ) and RCLK.

Various signals, both input and output signals operate differently depending on which timing mode is in effect.

#### **IDT STANDARD MODE**

In this mode, the status flags,  $\overline{FF}$ ,  $\overline{PAF}$ ,  $\overline{HF}$ ,  $\overline{PAE}$ , and  $\overline{EF}$  operate in the manner outlined in Table 3. To write data into to the FIFO, Write Enable (WEN) must be LOW. Data presented to the DATA IN lines will be clocked into the FIFO on subsequent transitions of the Write Clock (WCLK). After the first write is performed, the Empty Flag ( $\overline{EF}$ ) will go HIGH. Subsequent writes will continue to fill up the FIFO. The Programmable Almost-Empty flag ( $\overline{PAE}$ ) will go HIGH after n + 1 words have been loaded into the FIFO, where n is the empty offset value. The default setting for these values are stated in the footnote of Table 2. This parameter is also user programmable. See section on Programmable Flag Offset Loading.

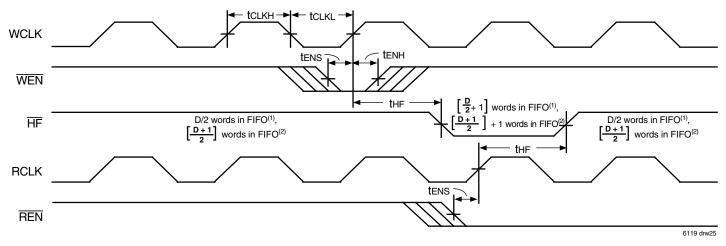

If one continued to write data into the FIFO, and we assumed no read operations were taking place, the Half-Full flag (HF) would toggle to LOW once (D/2 + 1) words were written into the FIFO. If x18 Input or x18 Output bus Width is selected, (D/2 + 1) = the 65,537th word for the IDT72V2103 and 131,073rd word for the IDT72V2113. If both x9 Input and x9 Output bus Widths are selected, (D/2 + 1) = the 131,073rd word for the IDT72V2103 and 262,145th word for the IDT72V2113. Continuing to write data into the FIFO will cause the Programmable Almost-Full flag (PAF) to go LOW. Again, if no reads are performed, the PAF will go LOW after (D-m) writes to the FIFO. If x18 Input or x18Output bus Width is selected, (D-m) = (131,072-m) writes for the IDT72V2103 and (262,144-m) writes for the IDT72V2113. If both x9 Input and x9 Output bus Widths are selected, (D-m) = (262,144-m) writes for the IDT72V2103 and (524,288-m) writes for the IDT72V2113. The offset "m" is the full offset value. The default setting for these values are stated in the footnote of Table 2. This parameter is also user programmable. See section on Programmable Flag Offset Loading.

When the FIFO is full, the Full Flag ( $\overline{FF}$ ) will go LOW, inhibiting further write operations. If no reads are performed after a reset,  $\overline{FF}$  will go LOW after D writes to the FIFO. If the x18 Input or x18 Output bus Width is selected, D = 131,072 writes for the IDT72V2103 and 262,144 writes for the IDT72V2113. If both x9 Input and x9 Output bus Widths are selected, D = 262,144 writes for the IDT72V2103 and 524,288 writes for the IDT72V2113, respectively.

If the FIFO is full, the first read operation will cause  $\overline{FF}$  to go HIGH. Subsequent read operations will cause  $\overline{PAF}$  and  $\overline{HF}$  to go HIGH at the conditions described in Table 3. If further read operations occur, without write operations,  $\overline{PAE}$  will go LOW when there are n words in the FIFO, where n is the empty offset value. Continuing read operations will cause the FIFO to become empty. When the last word has been read from the FIFO, the  $\overline{EF}$  will go LOW inhibiting further read operations.  $\overline{REN}$  is ignored when the FIFO is empty.

When configured in IDT Standard mode, the EF and FF outputs are double register-buffered outputs.

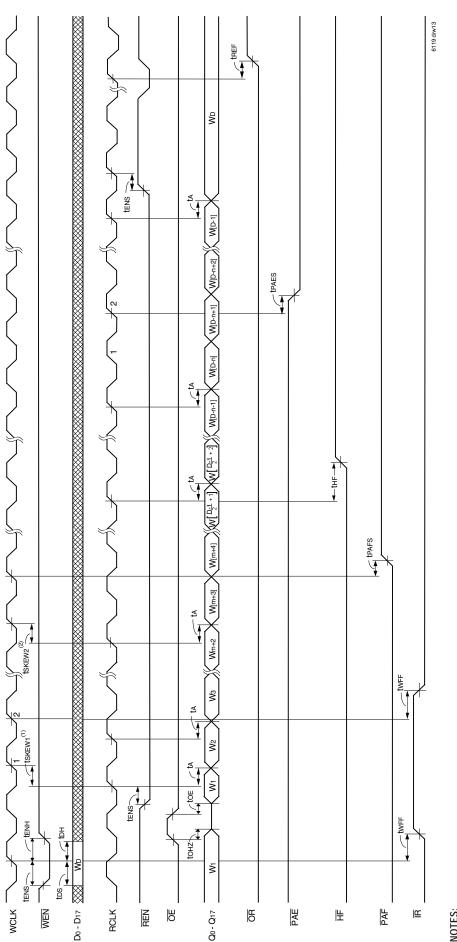

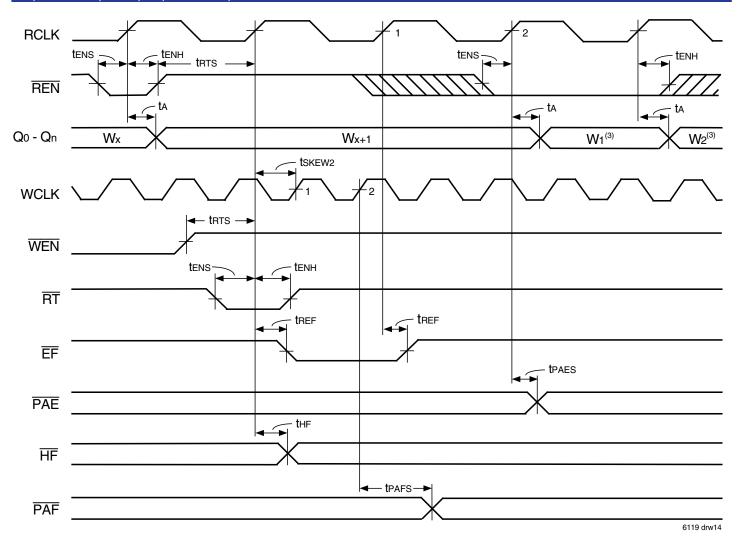

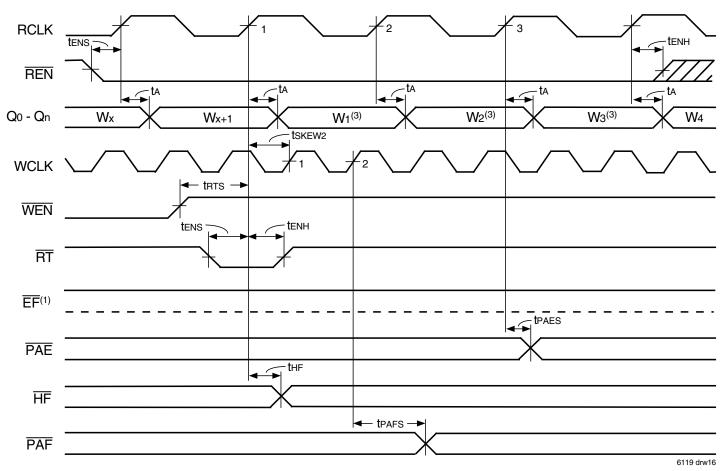

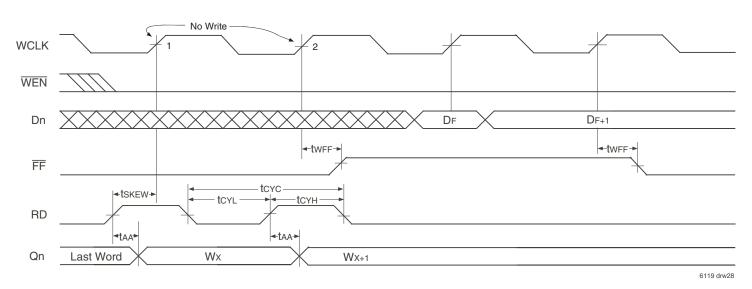

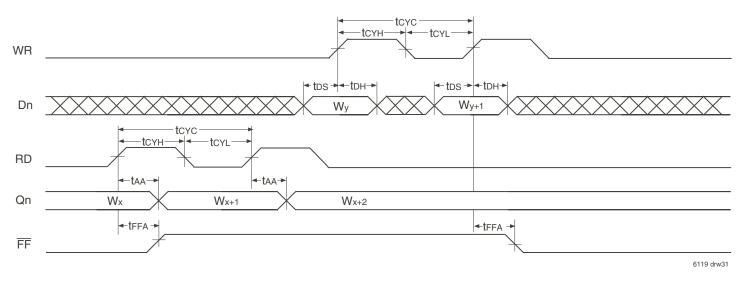

Relevant timing diagrams for IDT Standard mode can be found in Figure 7, 8 and 11.

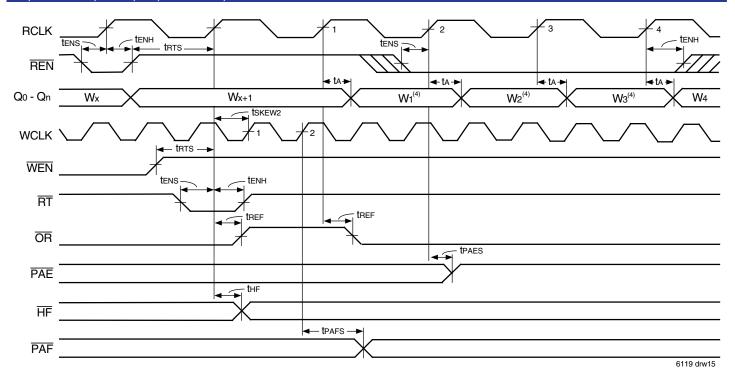

#### FIRST WORD FALL THROUGH MODE (FWFT)

In this mode, the status flags, **IR**, **PAF**, **HF**, **PAE**, and **OR** operate in the manner outlined in Table 4. To write data into the FIFO, **WEN** must be LOW. Data presented to the DATA IN lines will be clocked into the FIFO on subsequent transitions of WCLK. After the first write is performed, the Output Ready (**OR**) flag will go LOW. Subsequent writes will continue to fill up the FIFO. **PAE** will go HIGH after n+2 words have been loaded into the FIFO, where n is the empty offset value. The default setting for these values are stated in the footnote of Table 2. This parameter is also user programmable. See section on Programmable Flag Offset Loading.

If one continued to write data into the FIFO, and we assumed no read operations were taking place, the  $\overline{\text{HF}}$  would toggle to LOW once the (D/2 + 2) words were written into the FIFO. If x18 Input or x18 Output bus Width is selected, (D/2 + 2) = the 65,538th word for the IDT72V2103 and 131,074th word for the IDT72V2113. If both x9 Input and x9 Output bus Widths are selected, (D/2 + 2) = the 131,074th word for the IDT72V2103 and 262,146th word for the IDT72V2113. Continuing to write data into the FIFO will cause the PAF to go LOW. Again, if no reads are performed, the PAF will go LOW after (D-m) writes to the FIFO. If x18 Input or x18 Output bus Width is selected, (D-m) = (131,073-m) writes for the IDT72V2103 and (262,145-m) writes for the IDT72V2113. If both x9 Input and x9 Output bus Widths are selected, (D-m) = (262,145-m) writes for the IDT72V2103 and (524,289-m) writes for the IDT72V2113. The offset m is the full offset value. The default setting for these values are stated in the footnote of Table 2.

When the FIFO is full, the Input Ready ( $\overline{IR}$ ) flag will go HIGH, inhibiting further write operations. If no reads are performed after a reset,  $\overline{IR}$  will go HIGH after D writes to the FIFO. If x18 Input or x18 Output bus Width is selected, D = 131,073 writes for the IDT72V2103 and 262,145 writes for the IDT72V2113. If both x9 Input and x9 Output bus Widths are selected, D = 262,145 writes for the IDT72V2103 and 524,289 writes for the IDT72V2113, respectively. Note that the additional word in FWFT mode is due to the capacity of the memory plus output register.

If the FIFO is full, the first read operation will cause the IR flag to go LOW. Subsequent read operations will cause the PAF and HF to go HIGH at the conditions described in Table 4. If further read operations occur, without write operations, the PAE will go LOW when there are n+1 words in the FIFO, where n is the empty offset value. Continuing read operations will cause the FIFO to become empty. When the last word has been read from the FIFO, OR will go HIGH inhibiting further read operations. REN is ignored when the FIFO is empty.

When configured in FWFT mode, the  $\overline{OR}$  flag output is triple registerbuffered, and the  $\overline{IR}$  flag output is double register-buffered.

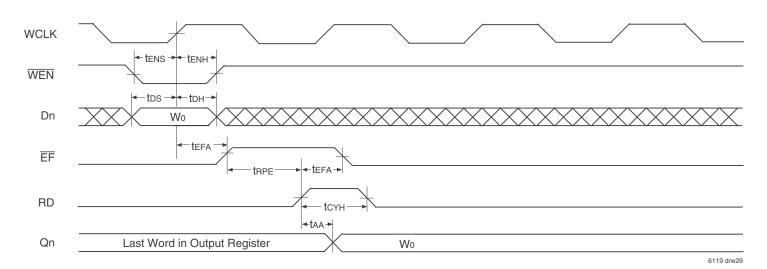

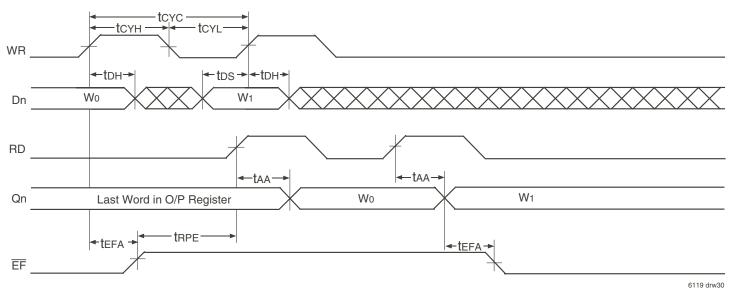

Relevant timing diagrams for FWFT mode can be found in Figure 9, 10 and 12.

# IDT72V2103/72V2113 3.3V HIGH DENSITY SUPERSYNC II™ NARROW BUS FIFO 131,072 x 18/262,144 x 9, 262,144 x 18/524,288 x 9

#### **PROGRAMMING FLAG OFFSETS**

Full and Empty Flagoffset values are user programmable. The IDT72V2103/ 72V2113 has internal registers for these offsets. There are eight default offset values selectable during Master Reset. These offset values are shown in Table 2. Offset values can also be programmed into the FIFO in one of two ways; serial or parallel loading method. The selection of the loading method is done using the  $\overline{LD}$  (Load) pin. During Master Reset, the state of the  $\overline{LD}$  input determines whether serial or parallel flag offset programming is enabled. A HIGH on  $\overline{LD}$ during Master Reset selects serial loading of offset values. A LOW on  $\overline{LD}$  during Master Reset selects parallel loading of offset values.

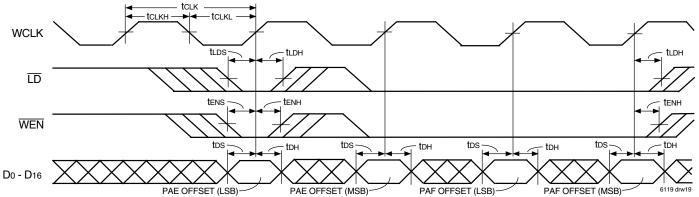

In addition to loading offset values into the FIFO, it is also possible to read the current offset values. Offset values can be read via the parallel output port Q0-Qn, regardless of the programming mode selected (serial or parallel). It is not possible to read the offset values in serial fashion.

## TABLE 2 — DEFAULT PROGRAMMABLE FLAG OFFSETS

| IDT72V2103, IDT72V2113 |       |       |                         |  |

|------------------------|-------|-------|-------------------------|--|

| LD                     | FSEL0 | FSEL1 | Offsets n,m             |  |

| L                      | L     | Н     | 16,383                  |  |

| L                      | Н     | L     | 8,191                   |  |

| L                      | Н     | Н     | 4,095                   |  |

| Н                      | L     | Н     | 2,047                   |  |

| Н                      | L     | L     | 1,023                   |  |

| Н                      | Н     | L     | 511                     |  |

| Н                      | Н     | Н     | 255                     |  |

| L                      | L     | L     | 127                     |  |

| ĒD                     | FSEL0 | FSEL1 | Program Mode            |  |

| Н                      | Х     | Х     | Serial <sup>(3)</sup>   |  |

| L                      | Х     | Х     | Parallel <sup>(4)</sup> |  |

NOTES:

1.  $n = empty offset for \overline{PAE}$ .

2. m = full offset for  $\overline{PAF}$ .

3. As well as selecting serial programming mode, one of the default values will also be loaded depending on the state of FSEL0 & FSEL1.

4. As well as selecting parallel programming mode, one of the default values will also be loaded depending on the state of FSEL0 & FSEL1. Figure 3, Programmable Flag Offset Programming Sequence, summaries the control pins and sequence for both serial and parallel programming modes. For a more detailed description, see discussion that follows.

The offset registers may be programmed (and reprogrammed) any time after Master Reset, regardless of whether serial or parallel programming has been selected. Valid programming ranges are from 0 to D-1.

# SYNCHRONOUS vs ASYNCHRONOUS PROGRAMMABLE FLAG TIMING SELECTION

The IDT72V2103/72V2113 can be configured during the Master Reset cycle with either synchronous or asynchronous timing for  $\overrightarrow{\text{PAF}}$  and  $\overrightarrow{\text{PAE}}$  flags by use of the PFM pin.

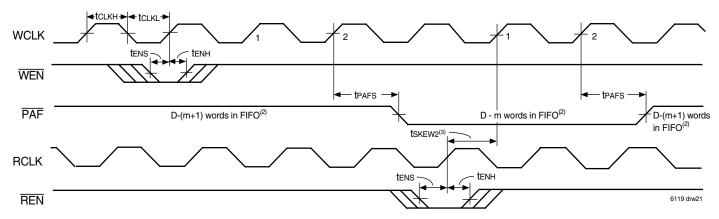

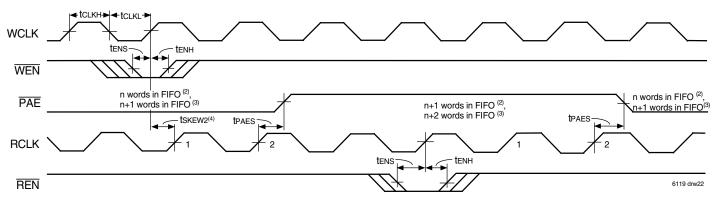

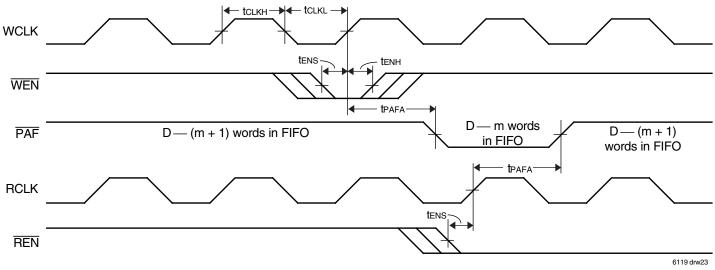

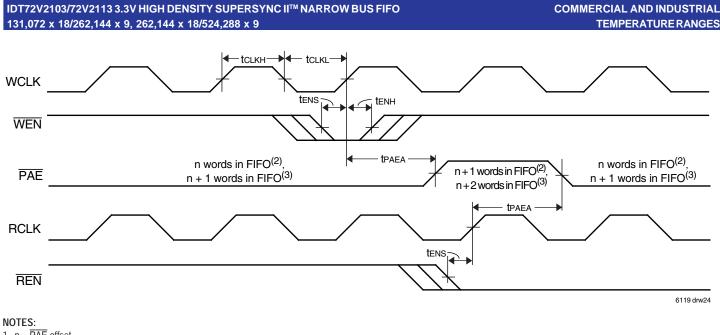

If synchronous PAF/PAE configuration is selected (PFM, HIGH during MRS), the PAF is asserted and updated on the rising edge of WCLK only and not RCLK. Similarly, PAE is asserted and updated on the rising edge of RCLK only and not WCLK. For detail timing diagrams, see Figure 18 for synchronous PAF timing and Figure 19 for synchronous PAE timing.

If asynchronous PAF/PAE configuration is selected (PFM, LOW during MRS), the PAF is asserted LOW on the LOW-to-HIGH transition of WCLK and PAF is reset to HIGH on the LOW-to-HIGH transition of RCLK. Similarly, PAE is asserted LOW on the LOW-to-HIGH transition of RCLK. PAE is reset to HIGH on the LOW-to-HIGH transition of WCLK. For detail timing diagrams, see Figure 20 for asynchronous PAF timing and Figure 21 for asynchronous PAE timing.

## TABLE 3 — STATUS FLAGS FOR IDT STANDARD MODE

| IW = OW = x9                             |                           | IDT72V2103                 | IDT72V2113                 |    |     |    |     |    |

|------------------------------------------|---------------------------|----------------------------|----------------------------|----|-----|----|-----|----|

| $IW \neq OW \text{ or}$<br>IW = OW = x18 | IDT72V2103                | IDT72V2113                 |                            | FF | PAF | ĦF | PAE | ĒF |

|                                          | 0                         | 0                          | 0                          | н  | н   | Н  | L   | L  |

|                                          | 1 to n                    | 1 to n                     | 1 to n                     | н  | н   | Н  | L   | Н  |

| Number of<br>Words in                    | (n+1) to 65,536           | (n+1) to 131,072           | (n+1) to 262,144           | н  | н   | н  | н   | Н  |

| FIFO                                     | 65,537 to (131,072-(m+1)) | 131,073 to (262,144-(m+1)) | 262,145 to (524,288-(m+1)) | н  | н   | L  | н   | н  |

| _                                        | (131,072-m) to 131,071    | (262,144-m) to 262,143     | (524,288-m) to 524,287     | н  | L   | L  | н   | Н  |

|                                          | 131,072                   | 262,144                    | 524,288                    | L  | L   | L  | Н   | Н  |

NOTE:

1. See Table 2 for values for n, m.

## TABLE 4 — STATUS FLAGS FOR FWFT MODE

| IW = OW = x9                |                           | IDT72V2103                 | IDT72V2113                 |    |     |    |     |           |

|-----------------------------|---------------------------|----------------------------|----------------------------|----|-----|----|-----|-----------|

| IW ≠ OW or<br>IW = OW = x18 | IDT72V2103                | IDT72V2113                 |                            | ĪR | PAF | HF | PAE | OR        |

|                             | 0                         | 0                          | 0                          | L  | н   | н  | L   | н         |

|                             | 1 to n+1                  | 1 to n+1                   | 1 to n+1                   | L  | н   | н  | L   | L         |

| Number of<br>Words in       | (n+2) to 65,537           | (n+2) to 131,073           | (n+2) to 262,145           | L  | н   | н  | н   | L         |

| FIFO <sup>(2)</sup>         | 65,538 to (131,073-(m+1)) | 131,074 to (262,145-(m+1)) | 262,146 to (524,289-(m+1)) | L  | н   | L  | н   | L         |

| 1                           | (131,073-m) to 131,072    | (262,145-m) to 262,144     | (524,289-m) to 524,288     | L  | L   | L  | н   | L         |

|                             | 131,073                   | 262,145                    | 524,289                    | Н  | L   | L  | н   | L         |

| NOTE:                       |                           |                            |                            |    |     |    | 46  | 666 drw05 |

1. See Table 2 for values for n, m.

2. Number of Words in FIFO = FIFO Depth + Output Register

# IDT72V2103/72V2113 3.3V HIGH DENSITY SUPERSYNC II<sup>™</sup> NARROW BUS FIFO 131,072 x 18/262,144 x 9, 262,144 x 18/524,288 x 9

#### COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

Figure 3. Programmable Flag Offset Programming Sequence

| ĒD | WEN | REN | SEN | WCLK | RCLK |                                                                                                                    | 72V2103<br>72V2113                                                                                          |  |

|----|-----|-----|-----|------|------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|

| 0  | 0   | 1   | 1   |      | x    | Parallel write to registers:<br>Empty Offset (LSB)<br>Empty Offset (MSB)<br>Full Offset (LSB)<br>Full Offset (MSB) |                                                                                                             |  |

| 0  | 1   | 0   | 1   | x    |      | Parallel read fror<br>Empty Offset (LS<br>Empty Offset (M<br>Full Offset (LSB)<br>Full Offset (MSB                 | SB)<br>SB)                                                                                                  |  |

| 0  | 1   | 1   | 0   |      | х    | x9 to x9 Mode<br>Serial shift into registers:<br>36 bits for the IDT72V2103<br>38 bits for the IDT72V2113          | All Other Modes<br>Serial shift into registers:<br>34 bits for the IDT72V2103<br>36 bits for the IDT72V2113 |  |

|    |     |     |     |      |      | 1 bit for each rising WCLK edge<br>Starting with Empty Offset (LSB)<br>Ending with Full Offset (MSB)               | 1 bit for each rising WCLK edge<br>Starting with Empty Offset (LSB)<br>Ending with Full Offset (MSB)        |  |

| Х  | 1   | 1   | 1   | Х    | Х    | No Oper                                                                                                            | ration                                                                                                      |  |

| 1  | 0   | x   | Х   |      | х    | Write Memory                                                                                                       |                                                                                                             |  |

| 1  | Х   | 0   | X   | X    |      | Read Memory                                                                                                        |                                                                                                             |  |

| 1  | 1   | 1   | Х   | Х    | Х    | No Oper                                                                                                            | ration                                                                                                      |  |

| L  | ļ   | ļ   | 1   | 1    | I    |                                                                                                                    | 6119 drw06b                                                                                                 |  |

#### NOTES:

1. The programming method can only be selected at Master Reset.

Parallel reading of the offset registers is always permitted regardless of which programming method has been selected.

The programming sequence applies to both IDT Standard and FWFT modes.

#### Figure 3. Programmable Flag Offset Programming Sequence (Continued)

#### IDT72V2103/72V2113 3.3V HIGH DENSITY SUPERSYNC II™ NARROW BUS FIFO 131,072 x 18/262,144 x 9, 262,144 x 18/524,288 x 9

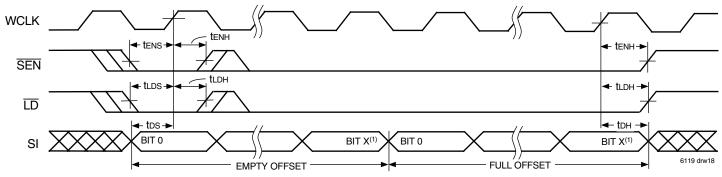

#### SERIAL PROGRAMMING MODE

If Serial Programming mode has been selected, as described above, then programming of PAE and PAF values can be achieved by using a combination of the LD, SEN, WCLK and SI input pins. Programming PAE and PAF proceeds as follows: when LD and SEN are set LOW, data on the SI input are written, one bit for each WCLK rising edge, starting with the Empty Offset LSB and ending with the Full Offset MSB. If x9 to x9 mode is selected, a total of 36 bits for the IDT72V2103 and 38 bits for the IDT72V2113. For any other mode of operation (that includes x18 bus width on either the Input or Output), minus 2 bits from the values above. So, a total of 34 bits for the IDT72V2103 and 36 bits for the IDT72V2113. See Figure 15, *Serial Loading of Programmable Flag Registers*, for the timing diagram for this mode.

Using the serial method, individual registers cannot be programmed selectively.  $\overrightarrow{PAE}$  and  $\overrightarrow{PAF}$  can show a valid status only after the complete set of bits (for all offset registers) has been entered. The registers can be reprogrammed as long as the complete set of new offset bits is entered. When  $\overrightarrow{LD}$  is LOW and  $\overrightarrow{SEN}$  is HIGH, no serial write to the registers can occur.

Write operations to the FIFO are allowed before and during the serial programming sequence. In this case, the programming of all offset bits does not have to occur at once. A select number of bits can be written to the SI input and then, by bringing LD and SEN HIGH, data can be written to FIFO memory via Dn by toggling WEN. When WEN is brought HIGH with LD and SEN restored to a LOW, the next offset bit in sequence is written to the registers via SI. If an interruption of serial programming is desired, it is sufficient either to set LD LOW and deactivate SEN or to set SEN LOW and deactivate LD. Once LD and SEN are both restored to a LOW level, serial offset programming continues.

From the time serial programming has begun, neither programmable flag will be valid until the full set of bits required to fill all the offset registers has been written. Measuring from the rising WCLK edge that achieves the above criteria; PAF will be valid after two more rising WCLK edges plus tPAF, PAE will be valid after the next two rising RCLK edges plus tSKEW2.

It is not possible to read the flag offset values in a serial mode.

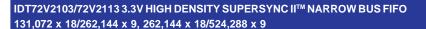

#### PARALLEL PROGRAMMING MODE

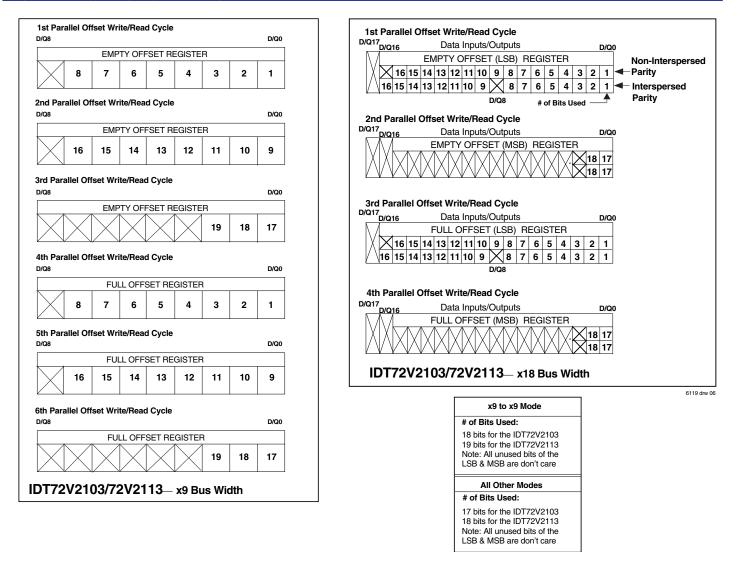

If Parallel Programming mode has been selected, as described above, then programming of PAE and PAF values can be achieved by using a combination of the LD, WCLK, WEN and Dn input pins. If the FIFO is configured for an input bus width and output bus width both set to x9, then the total number of write operations required to program the offset registers is 6 for the IDT72V2103/ 72V2113. Refer to Figure 3, *Programmable Flag Offset Programming Sequence*, for a detailed diagram of the data input lines Do-Dn used during parallel programming. If the FIFO is configured for an input to swidth of x9 to x18, x18 to x9 or x18 to x18, then the following number of write operations are required. For an input bus width of x18 total of 4 write operations will be required for the IDT72V2103/72V2113. For an input bus width of x9 a total of 6 will be required for the IDT72V2103/72V2113. Refer to Figure 3, *Programmable Flag Offset Programming*.

For example, programming PAE and PAF on the IDT72V2103/72V2113 configured for x18 bus width proceeds as follows: when LD and WEN are set LOW, data on the inputs Dn are written into the LSB of the Empty Offset Register on the first LOW-to-HIGH transition of WCLK. Upon the second LOW-to-HIGH transition of WCLK, data are written into the MSB of the Empty Offset Register. On the third LOW-to-HIGH transition of WCLK, data are written into the LSB of the Full Offset Register. On the fourth LOW-to-HIGH transition of WCLK, data are written into the MSB of the Full Offset Register. The fifth LOW-to-HIGH transition of WCLK, data are written into the MSB of the Full Offset Register. The fifth LOW-to-HIGH transition of WCLK, data are written into the MSB of the Full Offset Register.

Note that for x9 bus width, one extra Write cycle is required for both the Empty Offset Register and Full Offset Register. See Figure 16, *Parallel Loading of Programmable Flag Registers*, for the timing diagram for this mode.

The act of writing offsets in parallel employs a dedicated write offset register pointer. The act of reading offsets employs a dedicated read offset register pointer. The two pointers operate independently; however, a read and a write should not be performed simultaneously to the offset registers. A Master Reset initializes both pointers to the Empty Offset (LSB) register. A Partial Reset has no effect on the position of these pointers. Refer to Figure 3, *Programmable Flag Offset Programming Sequence*, for a detailed diagram of the data input lines Do-Dn used during parallel programming.

Write operations to the FIFO are allowed before and during the parallel programming sequence. In this case, the programming of all offset registers does not have to occur at one time. One, two or more offset registers can be written and then by bringing  $\overline{LD}$  HIGH, write operations can be redirected to the FIFO memory. When  $\overline{LD}$  is set LOW again, and  $\overline{WEN}$  is LOW, the next offset register in sequence is written to. As an alternative to holding  $\overline{WEN}$  LOW and toggling  $\overline{LD}$ , parallel programming can also be interrupted by setting  $\overline{LD}$  LOW and toggling  $\overline{WEN}$ .