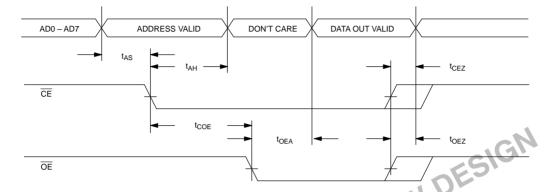

#### **OPERATION - READ CYCLE**

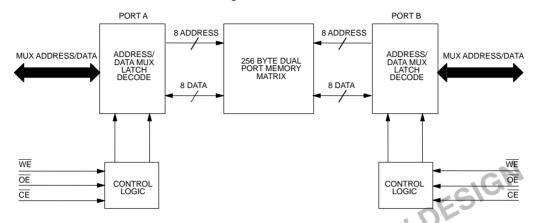

The main elements of the dual port RAM are shown in Figure 1.

A read cycle to either port begins by placing an address on the multiplexed bus pins AD0 – AD7. The port enable control ( $\overline{CE}$ ) is then transitioned low. This control signal causes address to be latched internally. Addresses can be removed from the bus provided address hold time is met. Next, the output enable control ( $\overline{OE}$ ) is transitioned low, which begins the data access portion of the read cycle. With both  $\overline{CE}$  and  $\overline{OE}$  active low, data will appear valid after the output enable access time  $t_{OEA}$ . Data will remain valid as long as both port enable and output enable remains low. A read cycle is terminated with the first occurring rising edge of either  $\overline{CE}$  or  $\overline{OE}$ . The address/data bus will return to a high impedance state after time  $t_{CEZ}$  or  $t_{OEZ}$  as referenced to the first occurring rising edge.  $\overline{WE}$  must remain high during read cycles.

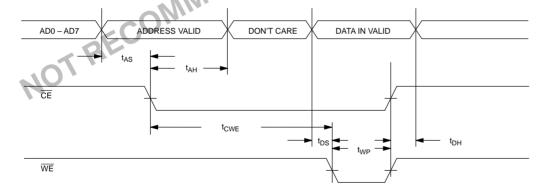

#### **OPERATION – WRITE CYCLE**

A write cycle to either port begins by placing an address on the multiplexed bus pins AD0 – AD7. The port enable control ( $\overline{\text{CE}}$ ) is then transitioned low. This control signal causes address to be latched internally. As with a read cycle, the address can be removed from the bus provided address hold time is met. Next the write enable control signal ( $\overline{\text{WE}}$ ) is transitioned low which begins the write data portion of the write cycle. With both  $\overline{\text{CE}}$  and

$\overline{\text{WE}}$  active low the data to be written to the selected memory location is placed on the multiplexed bus. Provided that data setup (tDS) and data hold (tDH) times are met, data is written into the memory and the write cycle is terminated on the first occurring rising edge of either  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$ . Data can be removed from the bus as soon as the write cycle is terminated.  $\overline{\text{OE}}$  must remain high during write cycles.

#### **ARBITRATION**

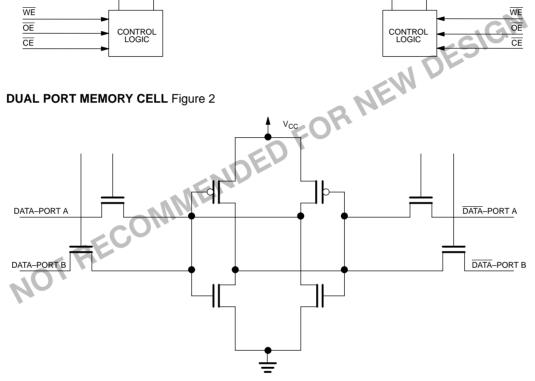

The DS1609 dual port RAM has a special cell design that allows for simultaneous accesses from two ports (see Figure 2). Because of this cell design, no arbitration is required for read cycles occurring at the same instant. However, an argument for arbitration can be made for reading and writing the cell at the exact same instant or for writing from both ports at the same instant. A simple way to assure that read/write conflicts don't occur is to perform redundant read cycles. Write/write arbitration needs can be avoided by assigning groups of addresses for write operation to one port only. Groups of data can be assigned check sum bytes which would guarantee correct transmission. A software arbitration system using a "mail box" to pass status information can also be employed. Each port could be assigned a unique byte for writing status information which the other port would read. The status information could tell the reading port if any activity is in progress and indicate when activity is going to occur.

# **BLOCK DIAGRAM: DUAL PORT RAM** Figure 1

ABSOLUTE MAXIMUM RATINGS\* Voltage on Any Pin Relative to Ground -0.5V to +7.0V Operating Temperature Storage Temperature -40°C to +85°C -55°C to +125°C Soldering Temperature 260°C for 10 seconds

# RECOMMENDED DC OPERATING CONDITIONS

(-40°C to +85°C)

|               |                 |      |     |                       | `     |       |

|---------------|-----------------|------|-----|-----------------------|-------|-------|

| PARAMETER     | SYMBOL          | MIN  | TYP | MAX                   | UNITS | NOTES |

| Power Supply  | V <sub>CC</sub> | 4.5  | 5.0 | 5.5                   | V     | 1     |

| Input Logic 1 | V <sub>IH</sub> | 2.0  |     | V <sub>CC</sub> + 0.3 | V C   | 7     |

| Input Logic 0 | V <sub>IL</sub> | -0.3 |     | +0.8                  | ٧     | 1     |

### DC ELECTRICAL CHARACTERISTICS

$(-40^{\circ}\text{C to } +85^{\circ}\text{C}; V_{CC} = 5\text{V} \pm 10\%)$

|                    |                   |      | _ ` |      | , 00  |          |

|--------------------|-------------------|------|-----|------|-------|----------|

| PARAMETER          | SYMBOL            | MIN  | TYP | MAX  | UNITS | NOTES    |

| Input Impedance    | Z <sub>IN</sub>   | 50K  | 60. |      | Ω     | 2        |

| CE, WE, OE Leakage | I <sub>LO</sub>   | -1.0 |     | +1.0 | μΑ    |          |

| Standby Current    | I <sub>CCS1</sub> | V    | 3.0 | 5.0  | mA    | 3, 4, 13 |

| Standby Current    | I <sub>CCS2</sub> |      | 50  | 300  | μΑ    | 3, 5, 13 |

| Standby Current    | I <sub>CCS3</sub> |      | 100 |      | nA    | 3, 6, 13 |

| Operating Current  | I <sub>CC</sub>   |      | 18  | 30   | mA    | 7, 13    |

| Logic 1 Output     | V <sub>OH</sub>   | 2.4  |     |      | V     | 8        |

| Logic 0 Output     | V <sub>OL</sub>   |      |     | 0.4  | V     | 9        |

#### **CAPACITANCE** $(t_A = 25^{\circ}C)$

| PARAMETER         | SYMBOL           | MIN | TYP | MAX | UNITS | NOTES |

|-------------------|------------------|-----|-----|-----|-------|-------|

| Input Capacitance | C <sub>IN</sub>  |     | 5   | 10  | pF    |       |

| I/O Capacitance   | C <sub>I/O</sub> |     | 5   | 10  | pF    |       |

<sup>\*</sup> This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

# **AC ELECTRICAL CHARACTERISTICS**

$(-40^{\circ}\text{C to } +85^{\circ}\text{C}; \text{V}_{\text{CC}} = 5\text{V} \pm 10\%)$

| PARAMETER            | SYMBOL           | MIN | TYP  | MAX | UNITS | NOTES |

|----------------------|------------------|-----|------|-----|-------|-------|

| Address Setup Time   | t <sub>AS</sub>  | 5   |      |     | ns    |       |

| Address Hold Time    | t <sub>AH</sub>  | 25  |      |     | ns    |       |

| Output Enable Access | t <sub>OEA</sub> | 0   |      | 50  | ns    | 10    |

| OE to High Z         | t <sub>OEZ</sub> | 0   |      | 20  | ns    |       |

| CE to High Z         | t <sub>CEZ</sub> | 0   |      | 20  | ns    |       |

| Data Setup Time      | t <sub>DS</sub>  | 0   |      |     | ns    |       |

| Data Hold Time       | t <sub>DH</sub>  | 10  |      |     | ns    |       |

| Write Pulse Width    | t <sub>WP</sub>  | 50  |      |     | ns    | 11    |

| CE Recovery Time     | t <sub>CER</sub> | 20  |      |     | ns    | 12    |

| WE Recovery Time     | t <sub>WER</sub> | 20  |      | 100 | ns    | 12    |

| OE Recovery Time     | t <sub>OER</sub> | 20  |      | 1EA | ns    | 12    |

| CE to OE Setup Time  | tCOE             | 25  | -B   |     | ns    |       |

| CE to WE Setup Time  | t <sub>CWE</sub> | 25  | \$O, |     | ns    |       |

# AC ELECTRICAL CHARACTERISTICS

$(-40^{\circ}\text{C to } +85^{\circ}\text{C}; V_{\text{CC}} = 2.5\text{V} - 4.5\text{V})$

| PARAMETER            | SYMBOL           | MIN | TYP | MAX | UNITS | NOTES |

|----------------------|------------------|-----|-----|-----|-------|-------|

| Address Setup Time   | t <sub>AS</sub>  | 5   |     |     | ns    |       |

| Address Hold Time    | t <sub>AH</sub>  | 25  |     |     | ns    |       |

| Output Enable Access | t <sub>OEA</sub> | 0   |     | 100 | ns    | 10    |

| OE to High Z         | t <sub>OEZ</sub> | 0   |     | 20  | ns    |       |

| CE to High Z         | t <sub>CEZ</sub> | 0   |     | 20  | ns    |       |

| Data Setup Time      | t <sub>DS</sub>  | 0   |     |     | ns    |       |

| Data Hold Time       | t <sub>DH</sub>  | 10  |     |     | ns    |       |

| Write Pulse Width    | t <sub>WP</sub>  | 100 |     |     | ns    | 11    |

| CE Recovery Time     | t <sub>CER</sub> | 20  |     |     | ns    | 12    |

| WE Recovery Time     | t <sub>WER</sub> | 20  |     |     | ns    | 12    |

| OE Recovery Time     | t <sub>OER</sub> | 20  |     |     | ns    | 12    |

| CE to OE Setup Time  | t <sub>COE</sub> | 25  |     |     | ns    |       |

| CE to WE Setup Time  | t <sub>CWE</sub> | 25  |     |     | ns    |       |

### **DUAL PORT RAM TIMING: READ CYCLE**

DURING READ CYCLE  $\overline{WE} = V_{IH}$

# NOTES:

- 1. During read cycle the address must be off the bus prior to  $t_{\mbox{\scriptsize OEA}}$  minimum to avoid bus contention.

- 2. Read cycles are terminated by the first occurring rising edge of  $\overline{\text{OE}}$  or  $\overline{\overline{\text{CE}}}$ .

# DUAL PORT RAM TIMING: WRITE CYCLE

DURING WRITE CYCLE OF = VIH

# NOTE:

1. Write cycles are terminated by the first occurring edge of  $\overline{\text{WE}}$  or  $\overline{\text{CE}}$ .

#### NOTES:

- 1. All Voltages are referenced to ground.

- 2. All pins other than CE, WE, OE, V<sub>CC</sub> and ground are continuously driven by a feedback latch in order to hold the inputs at one power supply rail or the other when an input is tristated. The minimum driving impedance presented to any pin is 50KΩ. If a pin is at a logic low level, this impedance will be pulling the pin to ground. If a pin is at a logic high level, this impedance will be pulling the pin to V<sub>CC</sub>.

- 3. Standby current is measured with outputs open circuited.

- 4. I<sub>CCS1</sub> is measured with all pins within 0.3V of V<sub>CC</sub> or GND and with  $\overline{\text{CE}}$  at a logic high or logic low level.

- 5.  $I_{CCS2}$  is measured with all pins within 0.3V of  $V_{CC}$  or ground and with  $\overline{CE}$  within 0.3V of  $V_{CC}$ .

- 6. I<sub>CCS3</sub> is measured with all pins at V<sub>CC</sub> or ground potential and with  $\overline{\text{CE}} = \text{V}_{\text{CC}}$ . Note that if a pin is floating, the internal feedback latches will pull all the pins to one power supply rail or the other.

- 7. Active current is measured with outputs open circuited, and inputs swinging full supply levels with one port reading and one port writing at 100 ns cycle time. Active currents are a DC average with respect to the number of 0's and 1's being read or written.

- 8. Logic one voltages are specified at a source current of 1 mA.

- 9. Logic zero voltages are specified at a sink current of 4 mA.

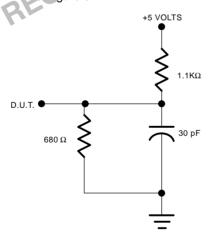

- 10. Measured with a load as shown in Figure 3.

- 11.  $t_{WP}$  is defined as the time from  $\overline{WE}$  going low to the first of the rising edges of  $\overline{WE}$  and  $\overline{CE}$ .

- 12. Recovery time is the amount of time control signals must remain high between successive cycles.

- 13. Typical values are at 25°C

### **LOAD SCHEMATIC** Figure 3

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated:

DS1609S-50 DS1609-50