## 2 Features and benefits

- High output power: 5.1 W (average) into 8 W at 4.0 V supply voltage (THD = 1 %)

- Supports handset (16  $\Omega$  or 32  $\Omega$ ) and hands-free (4  $\Omega$  or 8  $\Omega$ ) speaker configurations

- · High efficiency, low power dissipation and low-noise speaker driver

- Adaptive DC-to-DC converter increases the supply voltage smoothly when switching between fixed boost and adaptive boost modes, preventing large battery supply spikes and limiting quiescent power consumption.

- Wide supply voltage range (fully operational from 2.7 V to 5.5 V)

- Very low noise output <20×mV (with null data input at F<sub>s</sub> = 48 kHz)

- Low battery current consumption <130 mA (P<sub>o</sub> = 380 mW, average music power)

- I<sup>2</sup>C-bus control interface (400 kHz)

- Speaker current and voltage monitoring (via the I<sup>2</sup>S-bus) for Acoustic Echo Cancellation (AEC) at the host

- 16 kHz /44.1 kHz/48 kHz sample frequencies supported

- Ultrasonic support (limited) via TDM/I<sup>2</sup>S running at 96 kHz/192 kHz

- Configurable full-duplex 4-wire TDM/I<sup>2</sup>S input interface supporting up to 16 slots

- · Low-latency input path supporting side tone mixing via dedicated PDM input interface

- Speaker-as-Microphone feedback path on dedicated PDM output interface or TDM interface

- Programmable interrupt control via a dedicated interrupt pin

- Low RF susceptibility

- Thermal foldback and overtemperature protection

- 15 kV system-level ESD protection without external components on amplifier output

## 3 Applications

- Mobile phones & Tablets

- Portable Navigation Devices (PND)

- Notebooks/Netbooks

- Internet of Things applications embedding high-quality audio

## 4 Quick reference data

| Symbol              | Parameter                                   | Conditions                                                                                                                                                                                                                        | Min   | Тур  | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Unit |

|---------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| V <sub>BAT</sub>    | battery supply voltage                      | on pin VBAT $V_{\text{BAT}}$ must not be lower than $V_{\text{DDD}}$ or $V_{\text{DDE}}$ in application                                                                                                                           | 2.7   | -    | 5.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V    |

| V <sub>DDD</sub>    | digital supply voltage                      | on pin VDDD                                                                                                                                                                                                                       | 1.65  | 1.8  | 1.95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V    |

| V <sub>DD(IO)</sub> | input/output supply voltage                 | on pin VDDE                                                                                                                                                                                                                       | 1.65  | 1.8  | 1.95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V    |

| I <sub>BAT</sub>    | battery supply current                      | Active state<br>on pin VBAT; Operating mode with load; $R_L$<br>= 6 $\Omega$ ; DC-to-DC converter in Adaptive Boost<br>mode; $P_o$ = 380 mW (average music power);<br>$V_{BAT}$ = 4.0 V; $V_{DDP}$ = 8.5 V                        | -     | 122  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | mA   |

|                     |                                             | Idle state<br>on pin VBAT; Operating mode with load; R <sub>L</sub><br>= 6 $\Omega$ and no output signal (idle); DC-to-DC<br>converter in Adaptive Boost mode; V <sub>BAT</sub> =<br>4.0 V; V <sub>DDP</sub> = 8.5 V              | -     | 1.8  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | mA   |

|                     |                                             | Power-down state<br>on pin VBAT; DC-to-DC converter in power-<br>down mode; $T_j = 25$ °C; no clock                                                                                                                               | -     | 1    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | μA   |

| DDD                 | digital supply current                      | Active state<br>on pin VDDD; Operating mode with load;<br>$R_L = 6 \Omega$ ; DC-to-DC converter in Adaptive<br>Boost mode, $P_0 = 380 \text{ mW}$ (average music<br>power), $V_{BAT} = 4.0 \text{ V}$ ; $V_{DDP} = 8.5 \text{ V}$ | -     | 6.8  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | mA   |

|                     |                                             | Idle state<br>on pin VDDD; Operating mode with load;<br>$R_L = 6 \Omega$ and no output signal (idle); DC-to-<br>DC converter in Adaptive Boost mode; $V_{BAT}$<br>= 4.0 V; $V_{DDP}$ = 8.5 V                                      | -     | 4.1  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | mA   |

|                     |                                             | Power down state<br>on pin VDDD; DC-to-DC converter in power-<br>down mode; $T_j = 25$ °C; no clock                                                                                                                               | -     | 10   | 1.95         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -        < | μA   |

| P <sub>o(AVG)</sub> | average output power                        | THD+N = 1 %; L <sub>L</sub> = 44 $\mu$ H; V <sub>BAT</sub> = 4.0 V; V <sub>DDD</sub> = 1.8 V                                                                                                                                      |       |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

|                     |                                             | $V_{BST}$ = 9.5 V; R <sub>L</sub> = 8 $\Omega$                                                                                                                                                                                    | - 5.1 | -    | W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

|                     |                                             | V <sub>BST</sub> = 8.5 V; R <sub>L</sub> = 8 Ω                                                                                                                                                                                    | -     | 4.0  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | W    |

|                     |                                             | $V_{BST}$ = 9.5 V; R <sub>L</sub> = 6 $\Omega$                                                                                                                                                                                    | -     | 5.9  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | W    |

|                     |                                             | $V_{BST}$ = 8.5 V; R <sub>L</sub> = 6 $\Omega$                                                                                                                                                                                    | -     | 5.1  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | W    |

| SaM S/N             | speaker-as-microphone signal-to-noise ratio | A-weighted; PDM output; full scale input;<br>PGA gain setting GAIN_10                                                                                                                                                             | -     | 78.6 | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | dB   |

## **5** Ordering information

#### Table 2. Ordering information

| Type number Package |         |                                                                  |           |  |  |  |

|---------------------|---------|------------------------------------------------------------------|-----------|--|--|--|

|                     | Name    | Description                                                      | Version   |  |  |  |

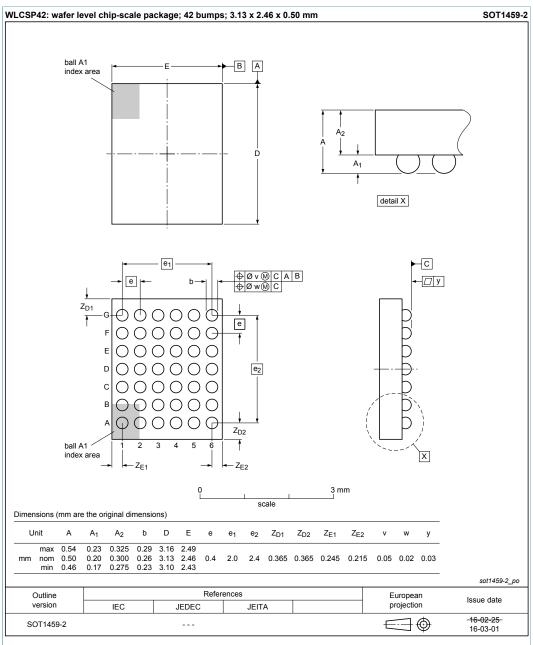

| TFA9872AUK/N1       | WLCSP42 | wafer level chip-scale package; 42 bumps; 3.13 × 2.46 × 0.50 mm  | SOT1459-2 |  |  |  |

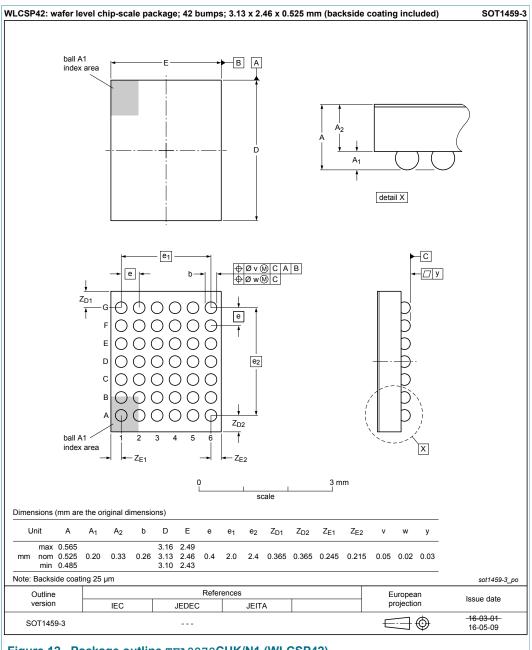

| TFA9872CUK/N1       | WLCSP42 | wafer level chip-scale package; 42 bumps; 3.13 × 2.46 × 0.525 mm | SOT1459-2 |  |  |  |

High Efficiency Class-D Audio Amplifier with Speaker-as-Microphone

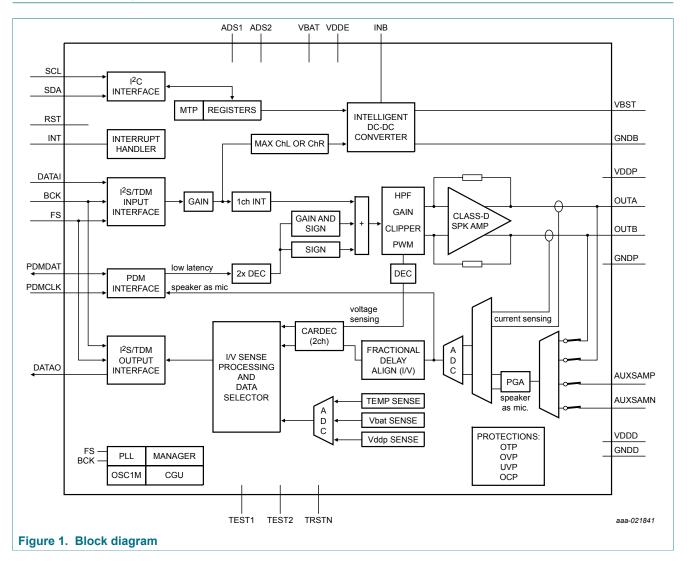

## 6 Block diagram

High Efficiency Class-D Audio Amplifier with Speaker-as-Microphone

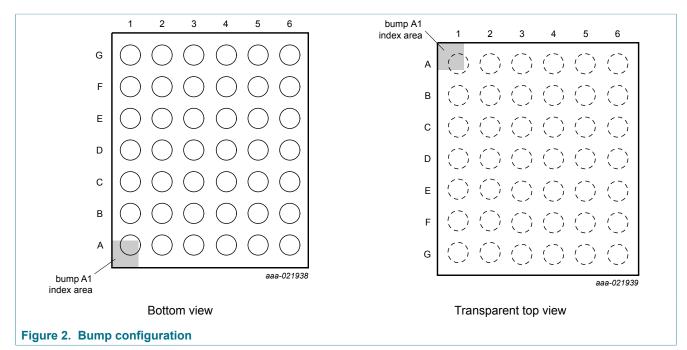

## 7 Pinning information

## 7.1 Pinning

|                        | 1      | 2       | 3     | 4    | 5    | 6          |

|------------------------|--------|---------|-------|------|------|------------|

| А                      | FS     | DATAI   | DATAO | GNDD | OUTB | VDDP       |

| В                      | ВСК    | INT     | RST   | GNDP | GNDP | VDDP       |

| С                      | PDMCLK | PDMDAT  | TRSTN | GNDD | OUTA | VDDP       |

| D                      | SCL    | AUXSAMP | TEST2 | GNDD | OUTA | VBST       |

| E                      | SDA    | AUXSAMN | TEST1 | GNDB | INB  | VBST       |

| F                      | VDDD   | ADS1    | GNDD  | GNDB | INB  | VBST       |

| G                      | VDDE   | ADS2    | VBAT  | GNDB | INB  | VBST       |

|                        |        |         |       |      |      | aaa-021936 |

| Figure 3. Bump mapping |        |         |       |      |      |            |

#### Transparent top view

High Efficiency Class-D Audio Amplifier with Speaker-as-Microphone

## 7.2 Pin description

| Table 3. Pinni | ng  |      |                                                                    |

|----------------|-----|------|--------------------------------------------------------------------|

| Symbol         | Pin | Туре | Description                                                        |

| FS             | A1  | I    | digital audio frame sync for TDM/I <sup>2</sup> S interface        |

| DATAI          | A2  | I    | digital audio data input for TDM/I <sup>2</sup> S interface        |

| DATAO          | A3  | 0    | digital audio data output for TDM/I <sup>2</sup> S interface       |

| GNDD           | A4  | Р    | digital ground                                                     |

| OUTB           | A5  | 0    | inverting output                                                   |

| VDDP           | A6  | Р    | power supply voltage                                               |

| BCK            | B1  | I    | digital audio bit clock input for TDM/I <sup>2</sup> S interface   |

| INT            | B2  | 0    | digital interrupt output                                           |

| RST            | В3  | I    | digital reset input                                                |

| GNDP           | B4  | Р    | power ground                                                       |

| GNDP           | B5  | Р    | power ground                                                       |

| VDDP           | B6  | Р    | power supply voltage                                               |

| PDMCLK         | C1  | I    | digital audio clock for PDM interface                              |

| PDMDAT         | C2  | I    | digital audio data for PDM interface                               |

| TRSTN          | C3  | I    | test reset signal (for JTAG); connect to PCB ground                |

| GNDD           | C4  | Р    | digital ground                                                     |

| OUTA           | C5  | 0    | non-inverting output                                               |

| VDDP           | C6  | Р    | power supply voltage                                               |

| SCL            | D1  | I    | digital I <sup>2</sup> C-bus clock input                           |

| AUXSAMP        | D2  | I/O  | auxiliary speaker-as-microphone non-inverting input                |

| TEST2          | D3  | I/O  | test signal input 2; for test purposes only, connect to PCB ground |

| GNDD           | D4  | Р    | digital ground                                                     |

| OUTA           | D5  | 0    | non-inverting output                                               |

| VBST           | D6  | 0    | boosted supply voltage output                                      |

| SDA            | E1  | I    | digital I <sup>2</sup> C-bus data input                            |

| AUXSAMN        | E2  | I/O  | auxiliary speaker-as-microphone inverting input                    |

| TEST1          | E3  | I/O  | test signal input 1; for test purposes only, connect to PCB ground |

| GNDB           | E4  | Р    | boosted ground                                                     |

| INB            | E5  | Р    | DC-to-DC boost converter input                                     |

| VBST           | E6  | 0    | boosted supply voltage output                                      |

| VDDD           | F1  | Р    | digital supply voltage                                             |

| ADS1           | F2  | I    | digital address select input 1                                     |

| GNDD           | F3  | Р    | digital ground                                                     |

| GNDB           | F4  | Р    | boosted ground                                                     |

TFA9872\_SDS

# TFA9872\_SDS

| Symbol | Pin | Туре | Description                    |

|--------|-----|------|--------------------------------|

| INB    | F5  | Р    | DC-to-DC boost converter input |

| VBST   | F6  | 0    | boosted supply voltage output  |

| VDDE   | G1  | Р    | digital IO supply voltage      |

| ADS2   | G2  | I    | digital address select input 2 |

| VBAT   | G3  | Р    | battery supply voltage         |

| GNDB   | G4  | Р    | boosted ground                 |

| INB    | G5  | Р    | DC-to-DC boost converter input |

| VBST   | G6  | 0    | boosted supply voltage output  |

## 8 Functional description

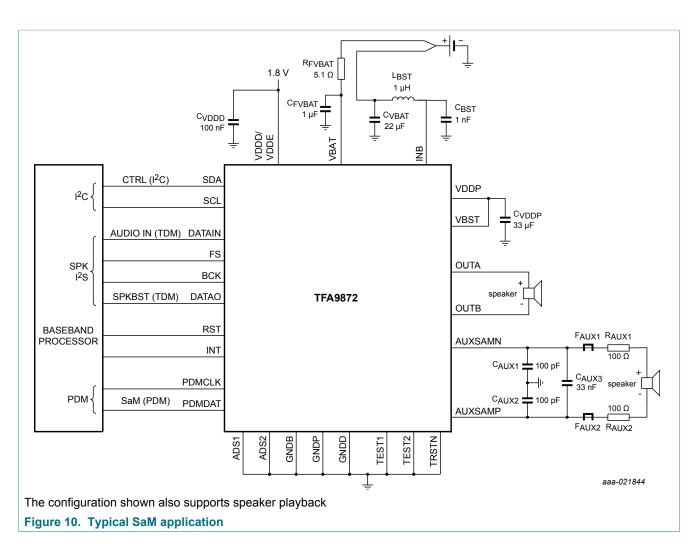

The TFA9872 is a highly efficient Bridge Tied Load (BTL) class-D audio amplifier embedding Speaker-as-Microphone (SaM) support, as depicted in the block diagram of <u>Figure 1</u>.

The TFA9872 contains a TDM/I<sup>2</sup>S input/output interface for communicating with the audio host. The maximum number of slots is 16 (at  $f_s = 48$  kHz) and the minimum number is 2 (I<sup>2</sup>S mode). The interface is compliant with all I<sup>2</sup>S interface configurations and supports a wide range of TDM interface configurations. It also features an optional ultrasonic path to the speaker.

The TFA9872 features a slave-configurable IN or OUT PDM interface. This audio interface can be connected to the audio host to provide a low-latency path (for side tone mixing) to the speaker. The 1-bit PDM stream is decimated and applied to the TDM interface. The PDM stream can, optionally, be attenuated or amplified by the gain module. Soft mute control prevents pop and click noise occurring when this signal path is switched on or off. The PDM output also provides a SaM stream back to the host.

At low battery voltage levels, the gain is automatically reduced to limit battery current (when battery safeguard is enabled).

The digital audio stream is converted into two PWM signals which are then injected into the class-D audio amplifier. The 3-level PWM scheme supports filterless speaker drive.

An adaptive DC-to-DC converter boosts the battery supply voltage when the audio stream crosses two programmable voltage thresholds. It switches automatically to Follower mode ( $V_{BST} = V_{BAT}$ ; no boost) when the audio output voltage is lower than the battery voltage.

The SaM feature is available in both PDM and I<sup>2</sup>S modes. This function can be used to turn the speaker into a dynamic microphone, providing an output audio stream on the digital interfaces. Due to the nature of the speaker membrane, the microphone equivalent characteristics perform best in high Sound Pressure Level (SPL) environments. Consequently, this feature is targeted at specific use cases such as concert recording or calls affected by wind noise. It is not intended to replace a primary/standard microphone but rather to complement it in such use cases by providing a signal that is less sensitive to saturation.

For SaM, a dedicated PGA is used to amplify the weak signal coming from the main speaker or receiver speaker. The result is a microphone that can handle high SPL environments.

SaM can be enabled on the main speaker connected to OUTA/OUTB, when the amplifier is off. Alternatively, SaM can be enabled on auxiliary inputs AUXSAMP/AUXSAMN, with the receiver speaker connected as input.

## 9 Limiting values

#### Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol           | Parameter                       | Conditions                             | Min  | Max                | Unit |

|------------------|---------------------------------|----------------------------------------|------|--------------------|------|

| V <sub>x</sub>   | voltage on pin x                | on pin VBAT                            | -0.3 | +6                 | V    |

|                  |                                 | on pins VBST, VDDP, AUXSAMP, AUXSAMN   | -0.3 | +12                | V    |

|                  |                                 | on pin INB, OUTA, OUTB                 | -0.3 | +12 <sup>[1]</sup> | V    |

|                  |                                 | on pins VDDD, VDDE, TEST1, TEST2       | -0.3 | +2.5               | V    |

| Tj               | junction temperature            |                                        | -40  | +150               | °C   |

| T <sub>stg</sub> | storage temperature             |                                        | -55  | +150               | °C   |

| T <sub>amb</sub> | ambient temperature             |                                        | -40  | +85                | °C   |

| V <sub>ESD</sub> | electrostatic discharge voltage | according to Human Body Model (HBM)    | -2   | +2                 | kV   |

|                  |                                 | according to Charge Device Model (CDM) | -500 | +500               | V    |

[1] Using an NXP demo board with a 1 mm wire/PCB track length on pin INB, AC pulses up to 18 V and -9 V can be observed without causing any damage as these spikes only partly penetrate the device (which is protected by internal clamp circuits).

# **10** Thermal characteristics

| Table 5. Thern | nal characteristics |

|----------------|---------------------|

| Symbol         | Devementer          |

| Symbol               | Parameter                                   | Conditions                | Тур | Unit |

|----------------------|---------------------------------------------|---------------------------|-----|------|

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | 4-layer application board | 36  | K/W  |

## **11 Characteristics**

### **11.1 DC Characteristics**

#### Table 6. DC characteristics

All parameters guaranteed for  $V_{BAT}$  = 3.6 V;  $V_{DDD}$  = 1.8 V;  $V_{DDP}$  =  $V_{BST}$  = 9.0 V; Adaptive Boost mode;  $L_{BST}$  = 1  $\mu H^{[1]}$ ;  $R_L$  = 8  $\Omega^{[1]}$ ;  $L_L$  = 44  $\mu H^{[1]}$ ;  $f_i$  = 1 kHz;  $f_s$  = 48 kHz;  $T_{amb}$  = 25 °C; default settings, unless otherwise specified.

| Symbol              | Parameter                   | Conditions                                                                                                                                                                                                                         |     | Min          | Тур | Max          | Unit |

|---------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------|-----|--------------|------|

| V <sub>BAT</sub>    | battery supply voltage      | on pin $V_{BAT}$ $V_{BAT}$ must not be lower than $V_{DDD}$ or $V_{DDE}$ in application                                                                                                                                            |     | 2.7          | -   | 5.5          | V    |

| IBAT                | battery supply current      | Active state<br>on pin V <sub>BAT</sub> ; Operating mode with load<br>$R_L = 6 \Omega$ ; DC-to-DC in Adaptive Boost<br>mode; P <sub>o</sub> = 380 mW, (average music<br>power), V <sub>BAT</sub> = 4.0 V, V <sub>DDP</sub> = 8.5 V |     | -            | 122 | -            | mA   |

|                     |                             | Idle state<br>on pin V <sub>BAT</sub> ; Operating mode with load<br>$R_L = 6 \Omega$ and no output signal (idle);<br>DC-to-DC converter in Adaptive Boost<br>mode; V <sub>BAT</sub> = 4.0 V, V <sub>DDP</sub> = 8.5 V              |     | -            | 1.8 | -            | mA   |

|                     |                             | Power-down state<br>on pin VBAT; DC-to-DC in power down<br>mode; $T_j = 25$ °C, no clock.                                                                                                                                          |     | -            | 1   | -            | μA   |

| V <sub>DDP</sub>    | power supply voltage        | on pin VDDP                                                                                                                                                                                                                        |     | 2.7          | -   | 10           | V    |

| V <sub>DD(IO)</sub> | input/output supply voltage | on pin VDDE                                                                                                                                                                                                                        |     | 1.65         | 1.8 | 1.95         | V    |

| V <sub>DDD</sub>    | digital supply voltage      | on pin VDDD                                                                                                                                                                                                                        |     | 1.65         | 1.8 | 1.95         | V    |

| I <sub>DDD</sub>    | digital supply current      | Active state<br>on pin VDDD; Operating mode with<br>load $R_L = 6 \Omega$ ; DC-to-DC in Adaptive<br>Boost mode; $P_o = 380 \text{ mW}$ , (average<br>music power); $V_{BAT} = 4.0 \text{ V}; V_{DDP} =$<br>8.5 V                   |     | -            | 6.8 | -            | mA   |

|                     |                             | Idle state<br>on pin V <sub>DDD</sub> ; Operating mode with load<br>$R_L = 6 \Omega$ and no output signal (idle);<br>DC-to-DC converter in Adaptive Boost<br>mode; V <sub>BAT</sub> = 4.0 V, V <sub>DDP</sub> = 8.5 V              |     | -            | 4.1 | -            | mA   |

|                     |                             | Power-down state<br>on pin VDDD; DC-to-DC in power down<br>mode; $T_j = 25$ °C, no clock.                                                                                                                                          |     | -            | 10  | -            | μA   |

| Pins FS, B          | CK, DATAI, ADS1, ADS2, SCL  | , SDA, PDMCLK, PDMDAT, RST, TRSTN                                                                                                                                                                                                  |     |              | 1   |              |      |

| V <sub>IH</sub>     | HIGH-level input voltage    |                                                                                                                                                                                                                                    |     | $0.7V_{DDD}$ | -   | 3.6          | V    |

| V <sub>IL</sub>     | LOW-level input voltage     |                                                                                                                                                                                                                                    |     | -            | -   | $0.3V_{DDD}$ | V    |

| Ci                  | input capacitance           |                                                                                                                                                                                                                                    | [2] | -            | -   | 3            | pF   |

# TFA9872\_SDS

#### High Efficiency Class-D Audio Amplifier with Speaker-as-Microphone

| Symbol                    | Parameter                                   | Conditions                               | Min  | Тур | Max                       | Unit |

|---------------------------|---------------------------------------------|------------------------------------------|------|-----|---------------------------|------|

| ILI                       | input leakage current                       | 1.8 V on input pin                       | -    | -   | 0.1                       | μA   |

| Pins DATA                 | O, INT, PDMDAT, push-pull outp              | out stages                               |      |     |                           |      |

| V <sub>OH</sub>           | HIGH-level output voltage                   | I <sub>OH</sub> = 4 mA                   | -    | -   | V <sub>DDD</sub> -<br>0.4 | V    |

| V <sub>OL</sub>           | LOW-level output voltage                    | I <sub>OL</sub> = 4 mA                   | -    | -   | 400                       | mV   |

| Pins SDA,                 | open drain outputs, external 10 k           | $\Omega$ resistor to V <sub>DDD</sub>    |      |     |                           |      |

| V <sub>OH</sub>           | HIGH-level output voltage                   | I <sub>OH</sub> = 4 mA                   | -    | -   | V <sub>DDD</sub> -<br>0.4 | V    |

| V <sub>OL</sub>           | LOW-level output voltage                    | I <sub>OL</sub> = 4 mA                   | -    | -   | 400                       | mV   |

| Pins OUTA                 | , OUTB                                      |                                          |      |     | -                         |      |

| R <sub>DSon</sub>         | drain-source on-state<br>resistance         | PMOS + NMOS transistors                  | -    | 510 | -                         | mΩ   |

| Protection                |                                             |                                          |      |     | 1                         |      |

| T <sub>act(th_prot)</sub> | thermal protection activation temperature   |                                          | 130  | -   | 150                       | °C   |

| V <sub>uvp(VBAT)</sub>    | undervoltage protection voltage on pin VBAT |                                          | 2.3  | -   | 2.5                       | V    |

| I <sub>O(ocp)</sub>       | overcurrent protection output current       |                                          | 2    | -   | -                         | A    |

| DC-to-DC                  | converter                                   |                                          |      |     |                           |      |

| V <sub>bst</sub>          | boost voltage                               | DCVOS = 111; Boost mode (after trimming) | 9.32 | 9.5 | 9.68                      | V    |

[1]

$L_{BST}$  = boost converter inductance;  $R_L$  = load resistance;  $L_L$  = load inductance (speaker). This parameter is not tested during production; the value is guaranteed by design and checked during product validation. [2]

### **11.2 AC characteristics**

#### Table 7. AC characteristics

All parameters guaranteed for  $V_{BAT}$  = 3.6 V;  $V_{DDD}$  = 1.8 V;  $V_{DDP}$  =  $V_{BST}$  = 9.0 V; Adaptive Boost mode;  $L_{BST}$  = 1  $\mu H^{[1]}$ ;  $R_L$  = 8  $\Omega^{[1]}$ ;  $L_L$  = 44  $\mu H^{[1]}$ ;  $f_i$  = 1 kHz;  $f_s$  = 48 kHz;  $T_{amb}$  = 25 °C; default settings, unless otherwise specified.

| Symbol                 | Parameter                            | Conditions                                                                                                                                                                                                |     | Min | Тур  | Max  | Unit |

|------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|------|

| Amplifier ou           | itput power                          |                                                                                                                                                                                                           |     |     |      |      |      |

| P <sub>o(AV)</sub>     | average output power                 | Hands-free speaker, THD+N = 1 %                                                                                                                                                                           |     |     |      |      |      |

|                        |                                      | R <sub>L</sub> = 8 Ω; f <sub>s</sub> = 48 kHz, V <sub>BST</sub> =<br>9.5 V, V <sub>BAT</sub> = 4.0 V                                                                                                      |     | 3.6 | 5.1  | -    | W    |

|                        |                                      | R <sub>L</sub> = 6 Ω; f <sub>s</sub> = 48 kHz, V <sub>BST</sub> =<br>9.5 V, V <sub>BAT</sub> = 4.0 V                                                                                                      |     | -   | 5.9  | -    | W    |

|                        |                                      | $R_L$ = 4 Ω; $f_s$ = 48 kHz, $V_{BST}$ = 9.5<br>V, $V_{BAT}$ = 4.0 V                                                                                                                                      |     | -   | 6.0  | -    | W    |

|                        |                                      | R <sub>L</sub> = 8 Ω; f <sub>s</sub> = 48 kHz, V <sub>BST</sub> =<br>8.5 V, V <sub>BAT</sub> = 3.6 V                                                                                                      |     | 3.6 | 4.0  | -    | W    |

|                        |                                      | R <sub>L</sub> = 6 Ω; f <sub>s</sub> = 48 kHz, V <sub>BST</sub> = 8.5 V, V <sub>BAT</sub> = 3.6 V                                                                                                         |     | -   | 5.1  | -    | W    |

|                        |                                      | R <sub>L</sub> = 4 Ω; f <sub>s</sub> = 48 kHz, V <sub>BST</sub> =<br>8.5 V, V <sub>BAT</sub> = 3.6 V                                                                                                      |     | -   | 5.2  | -    | W    |

|                        |                                      | Receiver speaker.THD+N = 1 %;<br>V <sub>BST</sub> = 9.5 V,                                                                                                                                                |     |     |      |      |      |

|                        |                                      | $R_L$ = 32 Ω; Voice mode                                                                                                                                                                                  |     | -   | 0.2  | -    | W    |

|                        |                                      | $R_L$ = 32 Ω; Audio mode                                                                                                                                                                                  |     | -   | 1.2  | -    | W    |

| Amplifier ou           | Itput pins (OUTA and OUTB)           |                                                                                                                                                                                                           |     |     |      |      |      |

| V <sub>O(offset)</sub> | output offset voltage                | absolute value after trimming; V <sub>DDP</sub> = 3.4 V to 9.5 V, V <sub>BAT</sub> = 3.4 V to 5 V                                                                                                         |     | -   | -    | 1.0  | mV   |

| Amplifier pe           | erformances                          |                                                                                                                                                                                                           |     |     |      |      |      |

| η <sub>ρο</sub>        | output power efficiency              | on pin VBAT; Operating mode with<br>load; $R_L = 6 \Omega$ ; DC-to-DC in Adaptive<br>Boost mode, $P_o = 380 \text{ mW}$ , (average<br>music power), $V_{BAT} = 4.0 \text{ V}$ , $V_{DDP} = 8.5 \text{ V}$ | [2] | -   | 80   | -    | %    |

|                        |                                      | on pin VBAT; input: 100 Hz sine<br>wave, $R_L = 8 \Omega$ ; DC-to-DC in<br>Adaptive Boost mode, $V_{BAT} = 4.0 V$ ,<br>$V_{DDP} = 8.5 V$ , $P_0 = 700 mW$                                                 | [2] | -   | 90   | -    | %    |

|                        |                                      | on pin VBAT; input: 100 Hz sine<br>wave, $R_L = 8 \Omega$ ; DC-to-DC in<br>Adaptive Boost mode, $V_{BAT} = 4.0 V$ ,<br>$V_{DDP} = 8.5 V$ , $P_o = 4 W$                                                    | [2] | -   | 84   | -    | %    |

| THD+N                  | total harmonic distortion-plus-noise | $V_{DDP}$ > 9 V, P <sub>o</sub> = 2.0 W, R <sub>L</sub> = 8 $\Omega$                                                                                                                                      | [2] | -   | 0.04 | 0.09 | %    |

|                        |                                      | $V_{DDP}$ > 9 V, P <sub>o</sub> = 2.0 W, R <sub>L</sub> = 4 $\Omega$                                                                                                                                      | [2] | -   | -    | 0.09 | %    |

| V <sub>n(o)</sub>      | output noise voltage                 | A-weighted; DATAI = 0 V; Low Noise<br>mode (ISTLA = 1); f <sub>s</sub> = 8 kHz                                                                                                                            | [2] | -   | 19   | 24   | μV   |

# TFA9872\_SDS

## High Efficiency Class-D Audio Amplifier with Speaker-as-Microphone

| Symbol                | Parameter                       | Conditions                                                                                                                                                                                                                                                   |     | Min  | Тур  | Max | Unit |

|-----------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|-----|------|

|                       |                                 | A-weighted; DATAI = 0 V; Low Noise mode (ISTLA = 1); $f_s = 16 \text{ kHz}$                                                                                                                                                                                  | [2] | -    | 55   | 60  | μV   |

| S/N                   | signal-to-noise ratio           | A-weighted, $V_{BAT}$ = 3.4 V to 5 V,<br>maximum signal at THD = 1 %                                                                                                                                                                                         | [2] | 100  | -    | -   | dB   |

| PSRR                  | power supply rejection ratio    | from V <sub>BAT</sub> ; booster in follower mode<br>(V <sub>DDP</sub> = V <sub>BAT</sub> ); f <sub>ripple</sub> = 217 Hz square<br>wave, V <sub>ripple</sub> = 50 mV(p-p), V <sub>BAT</sub> =<br>4.0 V                                                       |     | -    | 80   | -   | dB   |

|                       |                                 | from V <sub>BAT</sub> ; booster in follower mode<br>(V <sub>DDP</sub> = V <sub>BAT</sub> ); f <sub>ripple</sub> = 20 Hz to 1 kHz<br>sine wave, V <sub>ripple</sub> = 200 mV (RMS),<br>V <sub>BAT</sub> = 3.4 V to 5.0 V; Low Power<br>and Low Noise modes on |     | 60   | 80   | -   | dB   |

|                       |                                 | from V <sub>BAT</sub> ; $f_{ripple} = 20$ Hz to 1 kHz<br>sine wave, V <sub>ripple</sub> = 200 mV (RMS),<br>V <sub>BAT</sub> = 3.4 V to 5.0 V; DC-DC in<br>follower OR booster; Low Power and<br>Low Noise modes off                                          |     | -    | 75   | -   | dB   |

|                       |                                 | from V <sub>BAT</sub> ; booster in follower mode<br>(V <sub>DDP</sub> = V <sub>BAT</sub> ); f <sub>ripple</sub> = 1 kHz to 20<br>kHz sine wave, V <sub>ripple</sub> = 200 mV<br>(RMS), V <sub>BAT</sub> = 3.4 V to 5.0 V                                     |     | -    | 70   | -   | dB   |

| ∆G/∆f                 | gain variation with frequency   | BW = 20 Hz to 15 kHz, $V_{BAT}$ = 3.4 V to 5 V                                                                                                                                                                                                               |     | -0.1 | -    | 0.7 | dB   |

| V <sub>POP</sub>      | pop noise voltage               | at mode transition and gain change.                                                                                                                                                                                                                          |     |      |      | 2   | mV   |

| R <sub>L</sub>        | load resistance                 |                                                                                                                                                                                                                                                              |     | 4    | 8    | 32  | Ω    |

| CL                    | load capacitance                |                                                                                                                                                                                                                                                              |     | -    | -    | 200 | pF   |

| f <sub>sw</sub>       | switching frequency             | directly coupled to the I <sup>2</sup> S input frequency                                                                                                                                                                                                     |     | 256  | -    | 384 | kHz  |

| G <sub>v</sub>        | voltage gain                    | $I^2$ S/TDM to V <sub>O</sub> ; INPLEV = 0 (0 dB)                                                                                                                                                                                                            |     | 6    | -    | 21  | dB   |

| Amplifier po          | ower-up, power-down and propaga | tion delays                                                                                                                                                                                                                                                  |     |      |      |     |      |

| t <sub>d(on)PLL</sub> | PLL turn-on delay time          | PLL locked on BCK, $f_s$ = 48 kHz                                                                                                                                                                                                                            |     | -    | 2    | -   | ms   |

| t <sub>d(on)amp</sub> | amplifier turn-on delay time    | f <sub>s</sub> = 48 kHz                                                                                                                                                                                                                                      |     | -    | 1    | -   | ms   |

| t <sub>d(off)</sub>   | turn-off delay time             |                                                                                                                                                                                                                                                              |     | -    | 32   | -   | μs   |

| t <sub>d(alarm)</sub> | alarm delay time                |                                                                                                                                                                                                                                                              |     | -    | 200  | -   | ms   |

| t <sub>PD</sub>       | propagation delay               | f <sub>s</sub> = 16 kHz (I <sup>2</sup> S/TDM)                                                                                                                                                                                                               |     | -    | 1750 | -   | μs   |

|                       |                                 | f <sub>s</sub> = 48 kHz (I <sup>2</sup> S/TDM)                                                                                                                                                                                                               |     | -    | 600  | -   | μs   |

|                       |                                 | f <sub>s</sub> = 96/192 kHz (l <sup>2</sup> S/TDM)                                                                                                                                                                                                           |     | -    | 320  | -   | μs   |

|                       |                                 | f <sub>s</sub> = 48 kHz (PDM)                                                                                                                                                                                                                                |     | -    | 70   | -   | μs   |

| Booster Inc           | ductance                        | ·                                                                                                                                                                                                                                                            |     |      |      |     |      |

| L <sub>bst</sub>      | boost inductance                |                                                                                                                                                                                                                                                              |     | 0.7  | 1.0  | 2.2 | μH   |

| Current-sei           | nsing performance               |                                                                                                                                                                                                                                                              |     |      |      |     |      |

| L <sub>L(spk)</sub>   | speaker load inductance         |                                                                                                                                                                                                                                                              |     | 30   | -    | -   | μH   |

TFA9872\_SDS

**COMPANY PUBLIC**

© NXP B.V. 2017. All rights reserved.

# TFA9872\_SDS

## High Efficiency Class-D Audio Amplifier with Speaker-as-Microphone

| Symbol                | Parameter                            | Conditions                                                                                                              |     | Min  | Тур  | Max  | Unit |

|-----------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|------|

| S/N                   | signal-to-noise ratio                | I <sub>O</sub> = 1.1A (peak); A-weighted                                                                                |     | 62   | 65   | -    | dB   |

| ∆l <sub>sense</sub>   | current sense mismatch               | over frequency; 20 Hz to 4 kHz                                                                                          |     | -    | -    | 3    | %    |

|                       |                                      | over temperature; f <sub>i</sub> = 1 kHz; T <sub>j</sub> =<br>-20 °C to 85 °C                                           |     | -    | 2    | -    | %    |

|                       |                                      | over V <sub>DDP</sub> ; f <sub>i</sub> = 1 kHz, V <sub>DDP</sub> = 2.7 V to 9.5 V                                       |     | -    | 1    | -    | %    |

| THD+N                 | total harmonic distortion-plus-noise | f <sub>i</sub> = 20 Hz to 20 kHz; V <sub>i</sub> = -6 dBFS;<br>TDMSPKG = 0110                                           |     | -    | -    | 0.75 | %    |

| В                     | bandwidth                            |                                                                                                                         | [2] | 0.02 | -    | 20   | kHz  |

| Speaker-as            | s-microphone performance; pins OUTA  | , OUTB                                                                                                                  |     |      |      |      |      |

| GPGA                  | PGA gain                             | PGAGAIN = 30 dB (± 1.5 dB accuracy)                                                                                     |     | -    | 27.6 | -    | dB   |

|                       |                                      | PGAGAIN = 24 dB (± 1.5 dB accuracy)                                                                                     |     | -    | 22.2 | -    | dB   |

|                       |                                      | PGAGAIN = 18 dB (± 1.5 dB accuracy)                                                                                     |     | -    | 16.8 | -    | dB   |

|                       |                                      | PGAGAIN = 16 dB (± 1.5 dB accuracy)                                                                                     |     | -    | 14.9 | -    | dB   |

| V <sub>i(max)</sub>   | maximum input voltage                | PGAGAIN = 18 dB; RMS value                                                                                              | [3] | -    | 10.5 | -    | mV   |

|                       |                                      | PGAGAIN = 30 dB; RMS value                                                                                              | [4] | -    | 3.0  | -    | mV   |

| V <sub>n(i)(eq)</sub> | equivalent input noise voltage       | A-weighted, PGAGAIN: 30 dB; TDM<br>Output; RMS value                                                                    |     | -    | 1.05 | -    | μV   |

|                       |                                      | A-weighted, PGAGAIN: 16 dB; TDM<br>Output; RMS value                                                                    |     | -    | 2.35 | -    | μV   |

|                       |                                      | A-weighted, PGAGAIN: 30 dB; PDM<br>Output; RMS value                                                                    |     | -    | 1.20 | -    | μV   |

|                       |                                      | A-weighted, PGAGAIN: 16 dB; PDM<br>Output; RMS value                                                                    |     | -    | 1.35 | -    | μV   |

| S/N                   | signal-to-noise ratio                | A-weighted; PDM output; full scale input; PGAGAIN: 18 dB;                                                               |     | -    | 78.6 | -    | dB   |

|                       |                                      | A-weighted; PPDM Output<br>Full scale input, PGA gain setting<br>GAIN_00                                                |     | -    | 70.3 | -    | dB   |

|                       |                                      | A-weighted; PTDM output; full scale input; PGAGAIN: 18 dB;                                                              |     | -    | 76.9 | -    | dB   |

|                       |                                      | TDM output; full scale input;<br>PGAGAIN: 30 dB                                                                         |     | -    | 69.6 | -    | dB   |

| THD+N                 | total harmonic distortion-plus-noise | $f_i = 1 \text{ kHz}, V_i = 0.5\Omega \text{mV} (\text{RMS}),$<br>maximum PGA gain setting (30 dB),<br>on pin OUTA/OUTB |     | -    | 0.3  | -    | %    |

|                       |                                      | f <sub>i</sub> = 1 kHz, V <sub>i</sub> = 0. 5 mV (RMS),<br>maximum PGA gain setting (30 dB),<br>on pin AUXSAMN/AUXSAMP  |     | -    | 0.45 | -    | %    |

© NXP B.V. 2017. All rights reserved.

# **TFA9872\_SDS**

#### High Efficiency Class-D Audio Amplifier with Speaker-as-Microphone

| Symbol                 | Parameter                    | Conditions                                                                                                                            | Min                | Тур | Max | Unit |

|------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-----|------|

| PSRR                   | power supply rejection ratio | square wave on VDDD, f <sub>ripple</sub> = 217<br>Hz, V <sub>ripple</sub> = 50 mV (p-p), maximum<br>PGA gain setting ( <b>30 dB</b> ) | -                  | 70  | -   | dB   |

|                        |                              | sine wave on VDDD, f <sub>ripple</sub> = 20 Hz to<br>1 kHz, V <sub>ripple</sub> = 100 mV (RMS),<br>maximum PGA gain setting (30 dB)   | -                  | 70  | -   | dB   |

|                        |                              | sine wave on VDDD, f <sub>ripple</sub> = 1 kHz to<br>20 kHz, V <sub>ripple</sub> = 100 mV (RMS),<br>maximum PGA gain setting (30 dB)  | -                  | 60  | -   | dB   |

| V <sub>O(offset)</sub> | output offset voltage        | % of Full Scale; PDM output only<br>(offset is removed on TDM output)                                                                 | <sup>[5]</sup> -10 | -   | 10  | %    |

$L_{BST}$  = boost converter inductance;  $R_L$  = load resistance;  $L_L$  = load inductance (speaker). This parameter is not tested during production; the value is guaranteed by design and checked during product validation. Overload level at input; output is specified at 0 dBFS for TDM/PDM output max, or output limited at THD+N = 1 % if reached before 0 dBFS; THD = 1 %. Overload level at input; output is specified at 0 dBFS for TDM/PDM output max, or output limited at THD+N = 1 % if reached before 0 dBFS; THD = 1 %. When using PDM output for Speaker-as-Microphone, PDM stream decimation shall be done in codec or AP running SAM software and it must include a [1] [2] [3] [4] [5] DC offset remover.

#### High Efficiency Class-D Audio Amplifier with Speaker-as-Microphone

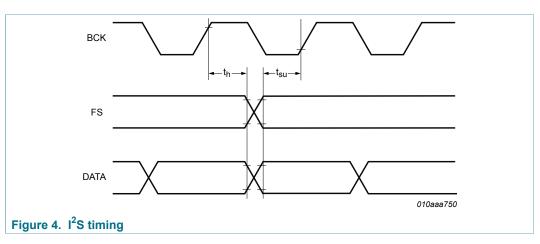

# 11.3 I<sup>2</sup>S timing characteristics

#### Table 8. I<sup>2</sup>S bus interface characteristics; see Figure 4

All parameters are guaranteed for  $V_{BAT} = 3.6 \text{ V}$ ;  $V_{DDD} = 1.8 \text{ V}$ ;  $V_{DDP} = V_{BST} = 9.0 \text{ V}$ , Adaptive Boost mode;  $L_{BST} = 1 \ \mu H^{[1]}$ ;  $R_L = 8 \ \Omega^{[1]}$ ;  $L_L = 44 \ \mu H^{[1]}$ ;  $f_i = 1 \ kHz$ ;  $f_s = 48 \ kHz$ ;  $T_{amb} = 25 \ ^{\circ}\text{C}$ ; default settings, unless otherwise specified.

| Symbol           | Parameter          | Conditions                  |     | Min              | Тур | Max               | Unit |

|------------------|--------------------|-----------------------------|-----|------------------|-----|-------------------|------|

| f <sub>s</sub>   | sampling frequency | on pin WS, audio mode       | [2] | 16               | -   | 48                | kHz  |

|                  |                    | on pin WS, ultrasonic mode  |     | 96               | -   | 192               | kHz  |

| f <sub>clk</sub> | clock frequency    | on pin BCK, audio mode      | [2] | 32f <sub>s</sub> | -   | 384f <sub>s</sub> | kHz  |

|                  |                    | on pin BCK, ultrasonic mode |     | -                | -   | 96f <sub>s</sub>  | MHz  |

| t <sub>su</sub>  | set-up time        | WS edge to BCK HIGH         | [3] | 10               | -   | -                 | ns   |

|                  |                    | DATA edge to BCK HIGH       |     | 10               | -   | -                 | ns   |

| t <sub>h</sub>   | hold time          | BCK HIGH to WS edge         | [3] | 10               | -   | -                 | ns   |

|                  |                    | BCK HIGH to DATA edge       |     | 10               | -   | -                 | ns   |

[1]

$L_{BST}$  = boost converter inductance;  $R_L$  = load resistance;  $L_L$  = load inductance. The I<sup>2</sup>S bit clock input (BCK) is used as a clock input for the amplifier and the DC-to-DC converter. Note that both the BCK and WS signals must be [2] present for the clock to operate correctly. This parameter is not tested during production; the value is guaranteed by design and checked during product validation.

[3]

#### High Efficiency Class-D Audio Amplifier with Speaker-as-Microphone

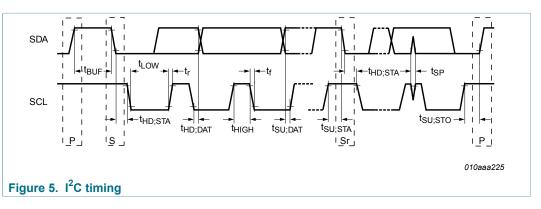

# 11.4 I<sup>2</sup>C timing characteristics

#### Table 9. I<sup>2</sup>C-bus interface characteristics; see Figure 5

All parameters are guaranteed for  $V_{BAT} = 3.6 \text{ V}$ ;  $V_{DDD} = 1.8 \text{ V}$ ;  $V_{DDP} = V_{BST} = 9.0 \text{ V}$ , Adaptive Boost mode;  $L_{BST} = 1 \ \mu H^{[1]}$ ;  $R_L = 8 \ \Omega^{[1]}$ ;  $L_L = 44 \ \mu H^{[1]}$ ;  $f_i = 1 \ kHz$ ;  $f_s = 48 \ kHz$ ;  $T_{amb} = 25 \ ^{\circ}\text{C}$ ; default settings, unless otherwise specified.

| Symbol              | Parameter                                                         | Conditions          |     | Min                     | Тур | Max | Unit |

|---------------------|-------------------------------------------------------------------|---------------------|-----|-------------------------|-----|-----|------|

| f <sub>SCL</sub>    | SCL clock frequency                                               |                     |     | -                       | -   | 400 | kHz  |

| t <sub>LOW</sub>    | LOW period of the SCL clock                                       |                     |     | 1.3                     | -   | -   | μs   |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                      |                     |     | 0.6                     | -   | -   | μs   |

| t <sub>r</sub>      | rise time                                                         | SDA and SCL signals | [2] | 20 + 0.1 C <sub>b</sub> | -   | -   | ns   |

| t <sub>f</sub>      | fall time                                                         | SDA and SCL signals |     | 20 + 0.1 C <sub>b</sub> | -   | -   | ns   |

| t <sub>HD;STA</sub> | hold time (repeated) START condition                              |                     | [3] | 0.6                     | -   | -   | μs   |

| t <sub>SU;STA</sub> | set-up time for a repeated START condition                        |                     |     | 0.6                     | -   | -   | μs   |

| t <sub>SU;STO</sub> | set-up time for STOP condition                                    |                     |     | 0.6                     | -   | -   | μs   |

| t <sub>BUF</sub>    | bus free time between a STOP and START condition                  |                     |     | 1.3                     | -   | -   | μs   |

| t <sub>SU;DAT</sub> | data set-up time                                                  |                     |     | 100                     | -   | -   | ns   |

| t <sub>HD;DAT</sub> | data hold time                                                    |                     |     | 0                       | -   | -   | μs   |

| t <sub>SP</sub>     | pulse width of spikes that must be suppressed by the input filter |                     | [4] | 0                       | -   | 50  | ns   |

| C <sub>b</sub>      | capacitive load for each bus line                                 |                     |     | -                       | -   | 400 | pF   |

[1]

$L_{BST}$  = boost converter inductance;  $R_L$  = load resistance;  $L_L$  = load inductance.  $C_b$  is the total capacitance of one bus line in pF. The maximum capacitive load for each bus line is 400 pF. [2]

After this period, the first clock pulse is generated. To be suppressed by the input filter. [3]

[4]

#### High Efficiency Class-D Audio Amplifier with Speaker-as-Microphone

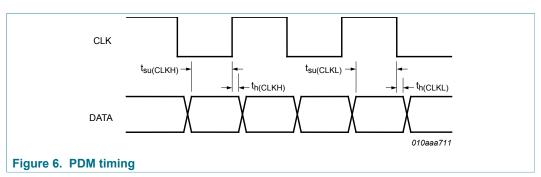

### 11.5 PDM timing characteristics

#### Table 10. PDM interface characteristics; see Figure 6

All parameters are guaranteed for  $V_{BAT} = 3.6 \text{ V}$ ;  $V_{DDD} = 1.8 \text{ V}$ ;  $V_{DDP} = V_{BST} = 9.0 \text{ V}$ , Adaptive Boost mode;  $L_{BST} = 1 \ \mu H^{[1]}$ ;  $R_L = 8 \ \Omega^{[1]}$ ;  $L_L = 44 \ \mu H^{[1]}$ ;  $f_i = 1 \ kHz$ ;  $f_s = 48 \ kHz$ ;  $T_{amb} = 25 \ ^{\circ}\text{C}$ ; default settings, unless otherwise specified.

| Symbol           | Parameter        | Conditions       | Min | Тур                  | Max | Unit |

|------------------|------------------|------------------|-----|----------------------|-----|------|

| f <sub>clk</sub> | clock frequency  |                  | -   | 3.072 <sup>[2]</sup> | -   | MHz  |

| δ <sub>clk</sub> | clock duty cycle |                  | 45  | -                    | 55  | %    |

| t <sub>h</sub>   | hold time        | after clock HIGH | 30  | -                    | -   | ns   |

|                  |                  | after clock LOW  | 30  | -                    | -   | ns   |

| t <sub>su</sub>  | set-up time      | after clock HIGH | 30  | -                    | -   | ns   |

|                  | -                | after clock LOW  | 30  | -                    | -   | ns   |

[1]

$L_{BST}$  = boost converter inductance;  $R_L$  = load resistance;  $L_L$  = load inductance. PDM Clock is 64xfs, with fs selected by AUDFS. Typical 3.072 Mhz is corresponding to f<sub>s</sub> = 48 kHz. [2]

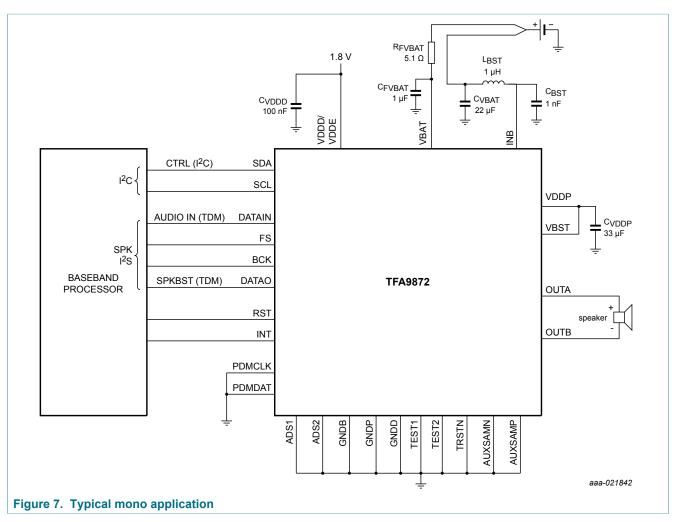

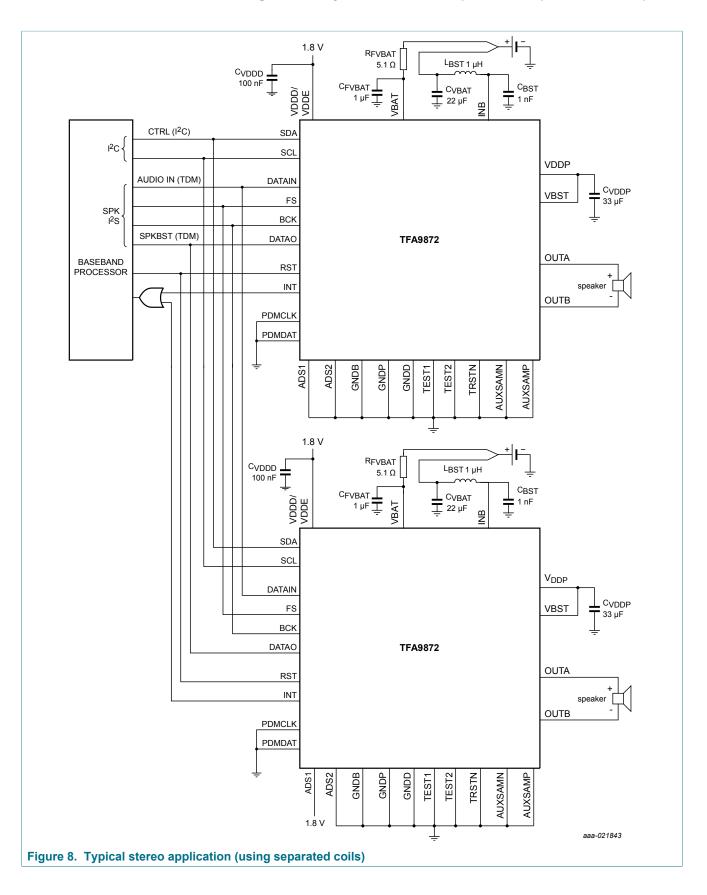

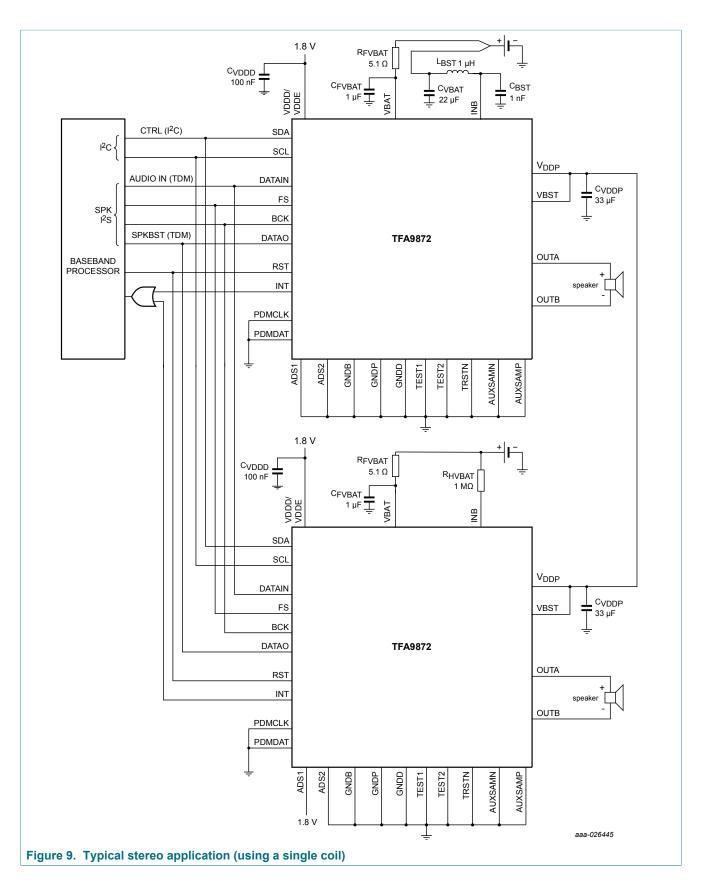

## **12** Application information

## 12.1 Application diagrams

# TFA9872\_SDS

# TFA9872\_SDS

# TFA9872\_SDS

High Efficiency Class-D Audio Amplifier with Speaker-as-Microphone

## 13 Package outline

# TFA9872\_SDS

#### High Efficiency Class-D Audio Amplifier with Speaker-as-Microphone

Figure 12. Package outline TFA9872CUK/N1 (WLCSP42)

## 14 Soldering of WLCSP packages

### 14.1 Introduction to soldering WLCSP packages

This text provides a very brief insight into a complex technology. A more in-depth account of soldering WLCSP (Wafer Level Chip-Size Packages) can be found in application note *AN10439 "Wafer Level Chip Scale Package"* and in application note *AN10365 "Surface mount reflow soldering description"*.

Wave soldering is not suitable for this package.

All NXP WLCSP packages are lead-free.

### 14.2 Board mounting

Board mounting of a WLCSP requires several steps:

- 1. Solder paste printing on the PCB

- 2. Component placement with a pick and place machine

- 3. The reflow soldering itself

### 14.3 Reflow soldering

Key characteristics in reflow soldering are:

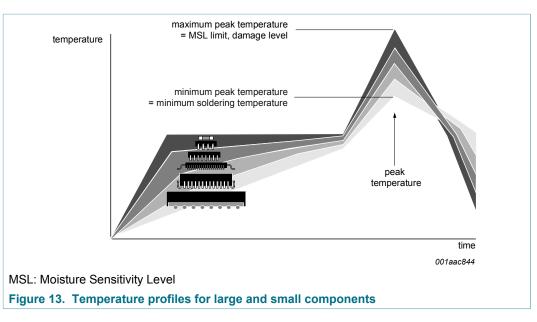

- Lead-free versus SnPb soldering; note that a lead-free reflow process usually leads to higher minimum peak temperatures (see Figure 1) than a SnPb process, thus reducing the process window

- Solder paste printing issues, such as smearing, release, and adjusting the process window for a mix of large and small components on one board

- Reflow temperature profile; this profile includes preheat, reflow (in which the board is heated to the peak temperature), and cooling down. It is imperative that the peak temperature is high enough for the solder to make reliable solder joints (a solder paste characteristic) while being low enough that the packages and/or boards are not damaged. The peak temperature of the package depends on package thickness and volume and is classified in accordance with <u>Table 11</u>.

| Package thickness (mm) | Package reflow temperature (°C)<br>Volume (mm <sup>3</sup> ) |             |        |  |  |  |

|------------------------|--------------------------------------------------------------|-------------|--------|--|--|--|

|                        |                                                              |             |        |  |  |  |

|                        | < 350                                                        | 350 to 2000 | > 2000 |  |  |  |

| < 1.6                  | 260                                                          | 260         | 260    |  |  |  |

| 1.6 to 1.5             | 260                                                          | 250         | 245    |  |  |  |

| > 2.5                  | 250                                                          | 245         | 245    |  |  |  |

#### Table 11. Lead-free process (from J-STD-020D)

Moisture sensitivity precautions, as indicated on the packing, must be respected at all times.

Studies have shown that small packages reach higher temperatures during reflow soldering, see <u>Figure 13</u>.

High Efficiency Class-D Audio Amplifier with Speaker-as-Microphone

For further information on temperature profiles, refer to application note AN10365 "Surface mount reflow soldering description".

#### 14.3.1 Stand off

The stand off between the substrate and the chip is determined by:

- The amount of printed solder on the substrate

- The size of the solder land on the substrate

- The bump height on the chip

The higher the stand off, the better the stresses are released due to TEC (Thermal Expansion Coefficient) differences between substrate and chip.

The higher the stand off, the better the stresses are released due to TEC (Thermal Expansion Coefficient) differences between substrate and chip.

#### 14.3.2 Quality of solder joint

A flip-chip joint is considered to be a good joint when the entire solder land has been wetted by the solder from the bump. The surface of the joint should be smooth and the shape symmetrical. The soldered joints on a chip should be uniform. Voids in the bumps after reflow can occur during the reflow process in bumps with high ratio of bump diameter to bump height, i.e. low bumps with large diameter. No failures have been found to be related to these voids. Solder joint inspection after reflow can be done with X-ray to monitor defects such as bridging, open circuits and voids.

#### 14.3.3 Rework

In general, rework is not recommended. By rework we mean the process of removing the chip from the substrate and replacing it with a new chip. If a chip is removed from the substrate, most solder balls of the chip will be damaged. In that case it is recommended not to re-use the chip again.

#### High Efficiency Class-D Audio Amplifier with Speaker-as-Microphone

Device removal can be done when the substrate is heated until it is certain that all solder joints are molten. The chip can then be carefully removed from the substrate without damaging the tracks and solder lands on the substrate. Removing the device must be done using plastic tweezers, because metal tweezers can damage the silicon. The surface of the substrate should be carefully cleaned and all solder and flux residues and/ or underfill removed. When a new chip is placed on the substrate, use the flux process instead of solder on the solder lands. Apply flux on the bumps at the chip side as well as on the solder pads on the substrate. Place and align the new chip while viewing with a microscope. To reflow the solder, use the solder profile shown in application note *AN10365 "Surface mount reflow soldering description*".

### 14.3.4 Cleaning

Cleaning can be done after reflow soldering.

# **15 Revision history**

| Table 12. Revision history |              |                    |               |            |

|----------------------------|--------------|--------------------|---------------|------------|

| Document ID                | Release date | Data sheet status  | Change notice | Supersedes |

| TFA9872_SDS v.1            | 20170412     | Product data sheet | -             | -          |

## 16 Legal information

### 16.1 Data sheet status

| Document status <sup>[1][2]</sup> | Product status <sup>[3]</sup> | Definition                                                                            |

|-----------------------------------|-------------------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet      | Development                   | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet    | Qualification                 | This document contains data from the preliminary specification.                       |

| Product [short] data sheet        | Production                    | This document contains the product specification.                                     |

Please consult the most recently issued document before initiating or completing a design. [1]

The term 'short data sheet' is explained in section "Definitions".

[2] [3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

### 16.2 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for guick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

Product specification — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

#### 16.3 Disclaimers